1

Изобретение относится к области вычислительной техники и может быть . использовано в цифровой вычислительной машине.

Известны устройства Для обработки данных, содержащие микропрограммную управляющую память с регистром микрокоманд и дешифраторами микрооперации, двухбайтный операционный узел с четырехбайтными регистрами - источниками и регистрами - приемниками информации и с селектором входных регистров, узел синхронизации l « 2.

Однако построение операционных узлов в этих устройствах и система связи операционных узлов с регистрами : источниками и регистрами - приемниками не позволяет вьтолнять в них обработку слов операндов, начиная со старших полуслов (обработка слева направо), что приводит к сильному усложнению микропрограмм реализации логических команд, команд сдвигов и, в результате.

К увеличению объема управляющей памяти и снижению быстродействия.

Наиболее близким техническим решением к данному предложению является устройство для обработки Данных, содержащее узел синхронизации, первый выход которого соединен со входом микропрограммной памяти, выход которой соединен со входами полей управления занесением выхода, выбора регистра - источника и многоцелевого назначения регистра микрокоманды, вьосоды которых соединены, соответственно, со входами дешифраторов микроопераций занесения выхода, микроопераций занесения на вход и многоцелевого поля, N регистров - источников информации, каждый из которых состоит из старшего и младшего полуслов, выходы которых подключены, соответственно, К первому, второму, , , . , 2 - у информационным входам селектора регистров, с первым, вторым, . . ., Ь -м управляющими входами которого соединены, соответственно, первый, второй, . , . ,

.N-и выходы дешифратора йТ1Кроог1ераций занесения на вход двухбайтный операционный узел и М регистров - приемников информации, состоящих из старших и млад.ших полуслов, причем управляющие входы первого, второго, ... и М-го регистра - приемника соединены, соответственно, с первым, вторым, . . . и М-м выходами дешифратора микроопераций Занесения выхода з.

Недостатком этого устройства является низкое быстродействие при изменении направления обработки слов операндов, так как при обработке данных слева направо необходимо использовать однобайтный режим работы двухбайтного операционного узла, т. е. этот узел работает с недогрузкой.

Цель изобретения - повышение быстродействия устройства.

. Поставленная цель достигается тем, что устройство, содержащее микропрограммную память, три дешифратора микрокома|{Д, регистр микрокоманд, И вхоДных регистров, И1 выходных регистров, коммутатор, операционный блок, блок синхронизации, причем выход микропрограммной памяти подключен ко входу регистра микрокоманд, первый, второй и третий выходы которого соединены, соответствен но, со входами первого, второго и третьего дешифраторов микрокоманд, выходы первого дешифратора микрокоманд соединены с первыми входами соответствующих гыходных регистров, первый выход второго дешифратора микрокоманд является выходом устройства, выходы третьего Дешифратора микрокоманд подключены к первой группе входов коммутатора, вторая группа входов которого соединена с выходами входных регистров, первый выход блока синхронизации подклиэчен ко входу микропрограммной памяти, введены входной коммутатор и выходной коммутатор, при этом второй выход второго де-шифратора микрокоманд соединен с первыми группами входов выходного коммутатора и входного коммутатора, вторые и третьи входы выходных регистров соединены, соответственно, с первым и: вторым выходами выходного коммутатора,, второй вход которого подключен к выход;) операционного блока, вход которого со«;динен с выходом входного коммутатора, вторая группа входов которого подключена к вы- ходам коммутатора, третий ичетьертый входы входного коммутатора соединены, соответственно, с первым и вторь м выходами блока синхронизации, третий и четвертый выходы которого подключены, соответственно, к третьему и четвертому входу выходного коммутатора.

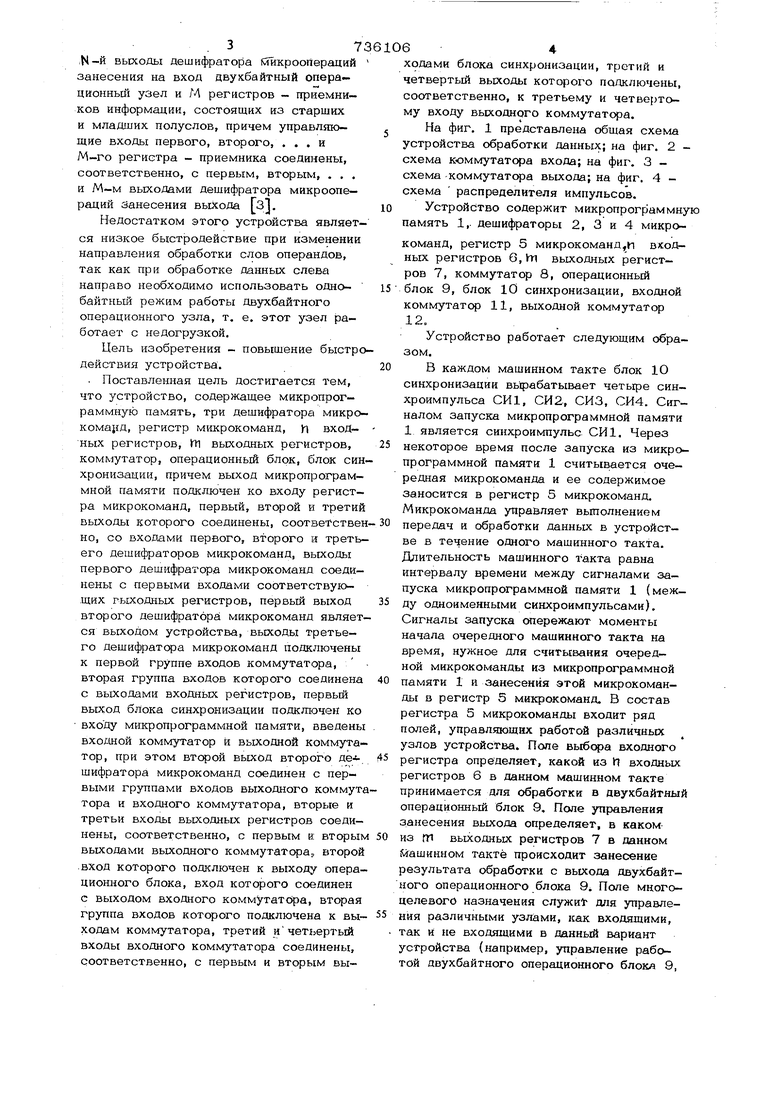

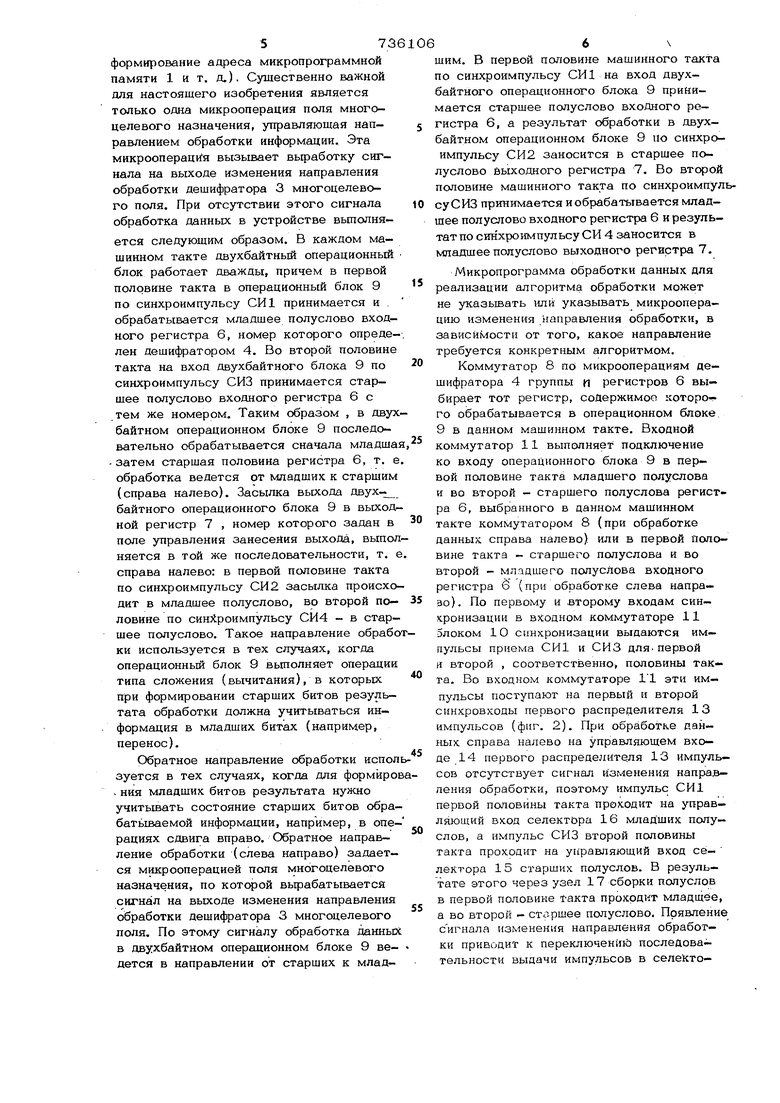

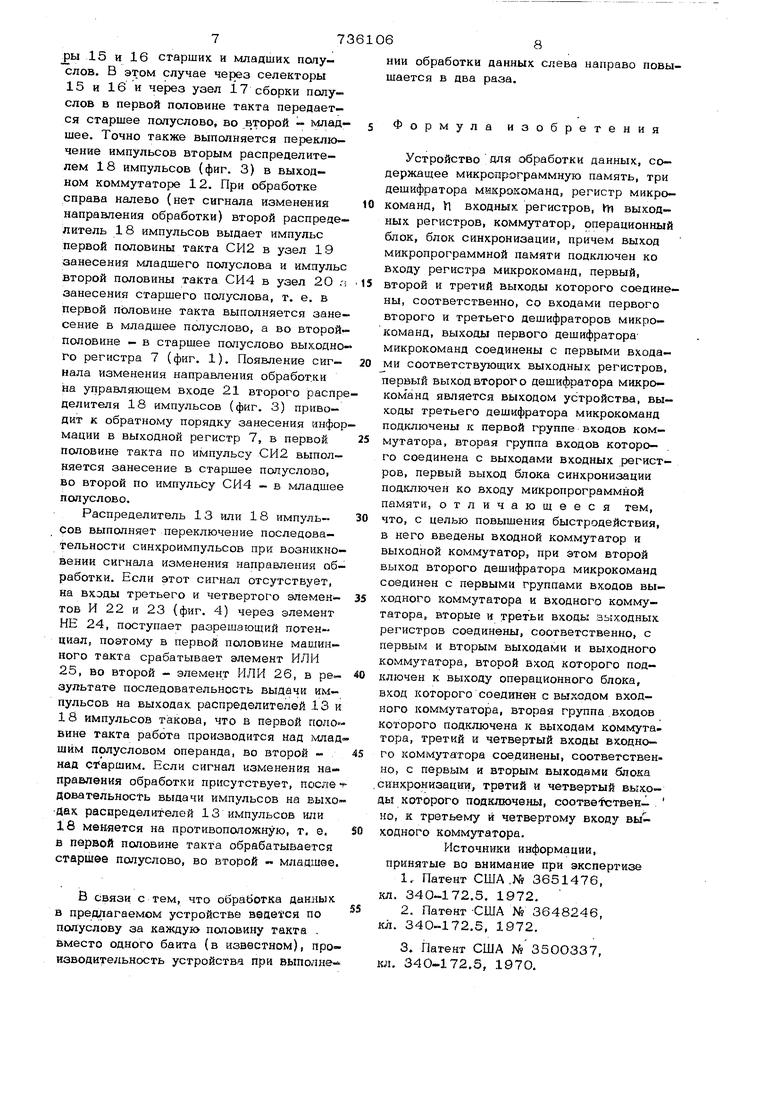

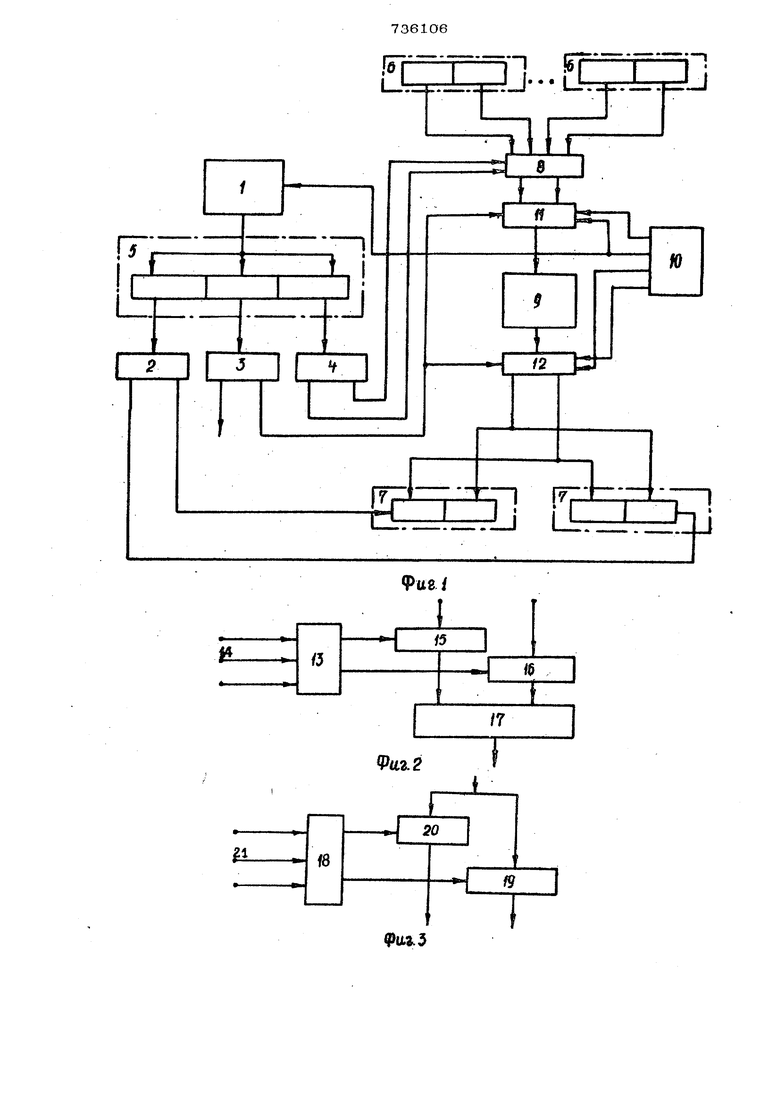

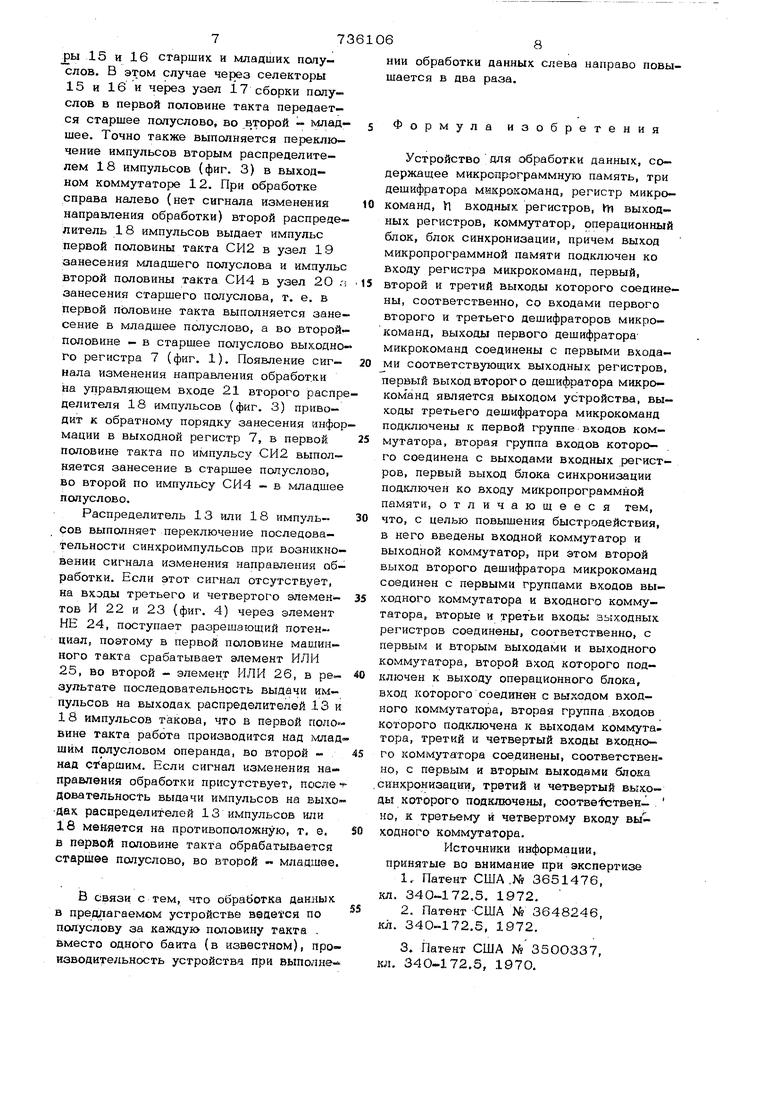

На фиг. 1 представлена общая схема устройства обработки данных; на фиг. 2 схема коммутатора входа; на фиг. 3 схема -коммутатора выхода; на фиг. 4 схема распределителя импульсов.

Устройство содержит микропрограммн память 1,. дешифраторы 2, 3 и 4 микрокоманд, регистр 5 микрокоманд,и входных регистров 6, hi выходных регистров 7, коммутатор 8, операционный блок 9, блок 10 синхронизации, входной коммутатор 11, выходной коммутатор 12.

Устройство работает следующим образом.

В каждом машинном такте блок 10 синхронизации вырабатывает четьфе синхроимпульса СИ1, СИ2, СИЗ, СИ4. Сигналом запуска микропрограммной памяти 1 является синхроимпульс СИ1. Через некоторое время после запуска из микропрограммной памяти 1 считывается очередная микрокоманда и ее содержимое заносится в регистр 5 микрокоманд. Микрокоманда управляет вьтолнением передач и обработки данных в устройстве в течение одного машинного такта. Длительность машинного такта равна интервалу времени между сигналами запуска микропрограммной памяти 1 (между одноименными синхроимпульсами). Сигналы запуска опережают моменты начала очередного машинного такта на время, нужное для считывания очередной микрокоманды из микропрограммной памяти 1 и занесения этой микрокомандь в регистр 5 микрокоманд. В состав регистра 5 микрокоманды входит ряд полей, управляющих работой различных узлов устройства. Попе выбсра входного регистра определяет, какой из И входных регистров 6 в данном машинном такте принимается для обработки в двухбайтны операционный блок 9, Поле управления занесения выхода определяет, в каком из ГЛ выходных регистров 7 в данном Машинном такте происходит занесение результата обработки с выхода двухбайтного операционного блока 9i Поле многоцелевого назначения служи для управления различньгми узлами, как входящими, так и не входящими в данный вариант устройства (например, управление работой двухбайтного операционного блокл 9, формирование адреса микропрограммной памяти 1 и т. д.). Существенно важной для настоящего изобретения является только одна микрооперация поля многоцелевого назначения, управляющая нап- равлением обработки информации. Эта микрооперация вызывает вьфаботку сигнала на выходе изменения направления обработки дешифратора 3 многоцелевого поля. При отсутствии этого сигнала обработка данных в устройстве вьшолняется следующим образом. В каждом мащинном такте двухбайтный операционный блок работает дважды, причем в первой половине такта в операционный блок 9 по синхроимпульсу СИ1 принимается и . обрабатывается младшее полуслово входного регистра 6, номер которого опреде лен дешифратором 4. Во второй половине такта на вход двухбайтного блока 9 по синхроимпульсу СИЗ принимается старшее полуслово входного регистра 6 с .тем же номером. Таким образом , в дву байтном операционном блоке 9 последовательно обрабатывается сначала младша -затем старшая половина регистра 6, т. обработка ведется от младших к старшим (справа налево). Засылка выхода двух- байтного операционного блока 9 в выход ной регистр 7 , номер которого задан в поле управления занесейия выхода, выпо няется в той же последовательности, т. справа налево: в первой половине такта по синхроимпульсу СИ2 засылка происхо дит в младшее полуслово, во второй по- ловине по синз4роимпульсу СИ4 - в старшее полуслово. Такое направление обраб ки используется в тех случаях, когда операционный блок 9 вьшолняет операции типа сложения (вычитания), в которых при формировании старших битов результата обработки должна учитываться информация в младших битах (например, перенос). Обратное направление обработки испол зуется в тех случаях, когда для формиро . ния младших битов результата нужно учитывать состояние старших битов обра батьшаемой информации, например, в oneрациях сдвига вправо. Обратное направление обработки (слева направо) задается микрооперацией поля К1ногоцелевого назначения, по которой вьфабатываетсй сигнал на выходе изменения направления обработки дешифратора 3 многоцелевого поля. По этому сигналу обработка данны в двухбайтном операционном блоке 9 ведется в направлении от старших к младшим. в первой половине машинного такта по синхроимпульсу СИ1 на вход двухбайтного операционного блока 9 принимается старшее полуслово входного регистра 6, а результат обработки в двухбайтном операционном блоке 9 по синхроимпульсу СИ2 заносится в старшее полуслово выходного регистра 7. Во второй половине машинного такта по синхроимпульсу С ИЗ принимается и обрабатывается младшее полуслово входного регистра 6 и результат по синхроимпульсу СИ 4 заносится в младшее полуслово выходного регистра 7. Микропрограмма обработки данных для реализации алгоритма обработки может не указьшать или указывать микрооперацию изменения направления обработки, в зависимости от того, какое направление требуется конкретным алгоритмом. Коммутатор 8 по микрооперациям дешифратора 4 группы и регистров 6 выбирает тот регистр, содержимое которого обрабатывается в операционном блоке 9 в данном машинном такте. Входной коммутатор 11 выполняет подключение ко входу операционного блока 9 в первой половине такта младшего полуслова и во второй - старшего полуслова регистра 6, выбранного в данном машинном такте коммутатором 8 (при обработке данных, справа налево) или в первой Половине такта - старшего полуслова и во второй - младшего полуслова входного регистра 6 (при обработке слева направо). По первому и второму входам синхронизации в входном коммутаторе 11 блоком 10 синхронизации выдаются импульсы приема СИ1 и СИЗ для. первой И второй , соответственно, половины такта. Во входном коммутаторе 11 эти импульсы поступают на первый и второй синхровходы первого распределителя 13 импульсов (фиг. 2). При обработке данных справа налево на управляющем входе 14 первого распределителя 13 импульсов отсутствует сигнал изменения направления обработки, поэтому импульс СИ1 первой половины такта проходит на управляющий вход селектора 16 младших полуслов, а импульс СИЗ второй половины такта проходит на у1фавляющий вход се- лектора 15 старших полуслов. В результате этого через узел 17 сборки полуслов в первой половине т-акта проходит младщёе, а во второй - старшее полуслово. Появление сигнала изменения направления обработки приводит к переключению последовательности выдачи импульсов в селеКто- jpbi 15 и 16 старших и младших паауслов. В этом случае через селекторы 15 и 16 и через узел 17 сборки псшуслов в первой половине такта передается старшее полуслово, во второй - «шад- шее. Точно также выполняется переключение импульсов вторым распределителем 18 импульсов (фиг. 3) в выходном коммутаторе 12. При обработке справа налево (нет сигнала изменения направления обработки) второй распределитель 18 импульсов выдает импульс первой половины такта СИ2 в узел 19 занесения младшего полуслова и импульс второй половины такта СИ4 в узел 20 л занесения старшего полуслова, т. е. в первой половине такта выполняется занесение в младшее полуслово, а во второй- половине - в старшее полуслово выкодно- Го регистра 7 (фиг. 1). Появление сигнала изменения направления обработки на управляющем входе 21 второго распре делителя 18 импульсов (фиг. 3) приводит к обратному порядку занесения инфор мации в выходной регистр 7, в первой половине такта по импульсу СИ2 выполняется занесение в старшее полуслово, во второй по импульсу СИ4 - в младшее полуслово. Распределитель 13 или 18 импульсов выполняет переключение последовательности синхроимпульсов при возникновении сигнала изменения направления обработки. Если этот сигнал отсутствует, на входы третьего и четвертого элементов И 22 и 23 (фиг. 4) через элемент НЕ 24, поступает разрешающий потенциал, поэтому в первой половине машинного такта срабатывает элемент ИЛИ 25, во второй - элемент ИЛИ 26, в результате последовательность выдачи импульсов на выходах распределителей 13 и 18 импульсов такова, что в первой половине такта работа производится над 1Ш1ад шим полусловом операнда, во второй над старшим. Если сигнал изменения направления обработки присутствует, после довательность выдачи импульсов на выхо дах распределителей 13 импульсов или 18 меняется на противоположную, т, е, в первой половине такта обрабатывается старшее полуслово, во второй - младшяе. В связи с тем, что обработка данных в предлагаемом устройстве ведемся по полуслову за каждук половину гакта , вместо одного байта (в известном), производительность устройства при выполне- НИИ обработки данных слева направо повышается в два раза. Формула изобретения Устройство для обработки данных, содержащее микропрограммную память, три дешифратора микрокоманд, регистр микро- команд, входных регистров, hi выходных регистров, коммутатор, операционный блок, блок синхронизации, причем выход микропрограммной памяти подключен ко входу регистра микрокоманд, первый, второй и третий выходы которого соединены, соответственно, со входами первого второго и третьего дешифраторов микрокоманд, выходы первого дешифраторамикрокоманд соединены с первыми входа- ми соответствующих выходных регистров, первый выход второго дешифратора микрокоманд является выходом устройства, выходы третьего дешифратора микрокоманд подключены к первой группе входов ком- мутатора, вторая группа входов которого соединена с выходами входных регистров, первый выход блока синхронизации подключен ко входу микропрограммной памяти, отличающееся тем, что, с целью повышения быстродействия, в него введены входной коммутатор и выходной коммутатор, при этом второй выход второго дешифратора микрокоманд соединен с первыми группами входов выходного коммутатора и входного коммутатора, вторые и третьи входы выходных регистров соединены, соответственно, с первым и вторым выходами и выходного KOMMjTaTOpa, второй вход которого под- ключей к выходу операционного блока, вход которого соединен с выходом входного коммутатора, вторая группа входов которого подключена к выходам коммута« тора, третий и четвертый входы входного коммутатора соединены, соответственно, с первым и вторым выходами блока синхронизации, третий и четвертый выходы которого подключены, соответственно, к третьему и четвертому входу выходного коммутатора. Источники информации, принятые во внимание при экспертизе 1.. Патент США .№ 3651476, кл. 340-172.5. 1972. 2. Патент США № 3648246, кл. 340-172.5, 1972. 3. Патент США № 3500337, кл. 340-172.5, 1970.

П бГ

,ТГ

.

JJ

и

м t т

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство микропрограммного управления | 1983 |

|

SU1151961A1 |

| Процессор с микропрограммным управлением и динамическим ветвлением | 1979 |

|

SU773624A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

а

Рва /

.

f(

Фаз.

Фаз.3

Авторы

Даты

1980-05-25—Публикация

1978-02-15—Подача