О

с

00

ю XI

лизацию в устройстве функций сдвига (выравнивания) и маскирования данных с помощью масок, формируемых шифраторами 19 и 20. Устройство позволяет обрабатывать данные переменной длины блоками (полуслово, слово и т.д.), формат которых превышает байт. Устройство обеспечивает

обработку десятичных данных без применения схемы десятичной коррекции, наложение двух разных масок на обрабатываемую информацию, а также оперативное изменение и использование новой маски (новых масок) в каждом цикле работы устройства. 2 ил., 3 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Вычислительное устройство с переменной длиной операндов | 1984 |

|

SU1160396A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для обработки данных переменной длины | 1976 |

|

SU648984A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах цифровых вычислительных машин. Изобретение позволяет повысить пропускную способность устройства для обработки данных переменной длины за счет сокращения внутреннего цикла работы, а также ускоренного выполнения операций маскирования и часто встречающихся видов логической обработки данных. Устройство реализовано на основном оборудовании процессора и содержит шины 1-4 данных, являющиеся информационными входами-выходами 5-8 устройства, блок 9 памяти, блоки 10,11 коммутации, арифметико-логический блок 13, коммутатор 12, регистр 16 маски, регистр 18 тетрадных переносов, первый 19 и второй 20 шифраторы маски. Блоки 10 и 11 обеспечивают pea

Изобретение относится к вычислительной технике, в частности к устройствам для обработки данных переменной длины, и может быть использовано в процессорах цифровых вычислительных машин.

Цель изобретения - повышение пропускной способности.

На фиг. 1 представлена структурная схема устройства для обработки данных переменной длины; на фиг. 2 - предпочтитель- ный вариант реализации блоков коммутации для случая малых универсальных ЭВМ.

Устройство для обработки данных переменной длины (фиг. 1) содержит первую 1, вторую 2, третью 3 и четвертую 4 шины данных, являющиеся соответственно первым 5, вторым 6, третьим 7 и четвертым 8 информационными входами-выходами, блок 9 памяти, первый 10 и второй 11 блоки коммутации, коммутатор 12, арифметико- логический блок 13, блок 14 управления сдвигом, выход которого является входом 15 управления сдвигом, регистр 16 маски, вход которого является входом 17 маски, регистр 18 тетрадных переносов, первый 19 и второй 20 шифраторы маски и шину, 21 управления. Первый выход 22 блока 9 памяти, первый информационный вход 23 блока 10 коммутации и первый информационный вход 24 второго блока 11 коммутации подключены к первой шине 1 данных, второй выход 25 блока памяти 9, второй информационный вход26 первого блока 10 коммутации и второй информационный вход 27 второго блока 11 коммутации подключены к второй шине 2 данных, первый информационный вход 28 блока памяти 9 и выход 29 коммутатора 12 подключены к третьей шине 3 данных, второй информационный вход 30 блока 9 памяти и выход 31 коммутатора 12 подключены к четвертой шине 4 данных. Выход 32 первого блока 10 коммутации и выход 33 второго блока 11 коммутации соединены соответственно с первым 34 и вторым 35 информационными входами блока 13, выход 36 тетрадных переносов которого подключен к информационному входу 37 регистра 18 тетрадных переносов, а информационный выход 38 - к информационному входу 39 коммутатора 12. Выходы 40 и 41 соответственно первого 10 и второго 11 блоков коммутации объединены и подключены к информационному входу 42 коммутатора

19 и второго 20 шифраторов маски соединены соответственно с информационным входом 48 блока 10 и информационным входом 49 блока 11, вход 15 управления сдвигом подключен к информационным входам 50 и

51 блоков 10 и 11 соответственно. Шина 21 управления подключена к управляющим входам 52-61 соответственно блока 9 памяти, первого 10, второго 11, третьего 12 коммутаторов, блока 13, блока 14 управления

сдвигом, регистра 16 маски, регистра 18тетрадных переносов, первого 19 и второго 20 шифраторов маски.

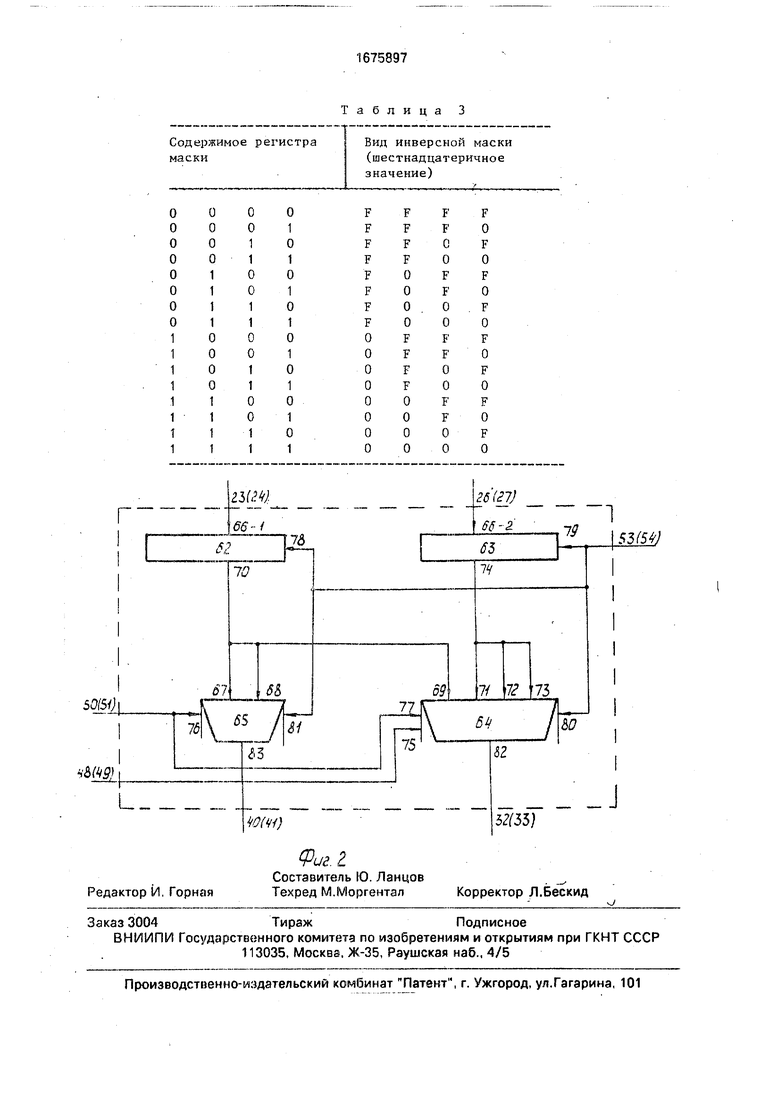

В представленном на фиг. 2 варианте реализации первого 10 и второго 11 блоков

коммутации, учитывающем особенности структурной организации малых универсальных вычислительных машин, каждый из них содержит первый 62 и второй 63 регистры исходных данных, мультиплексоры 64

входных данных и мультиплексор 65 сдвига. Входы 66-1 и 66-2 соответственно регистров 62 и 63 являются информационными входами 23 (24), 26 (27) блока 10 (11). Вход 67 левого сдвига, вход 68 правого сдвига мультиплексора 65 сдвига и первый 69 информационный вход мультиплексора 64 соединены с выходом 70 первого регистра 62 исходных данных. Второй информационный вход 71, вход 72 левого сдвига и вход 73

правого сдвига мультиплексора 64 соединены с выходом 74 второго регистра 63 исходных данных. Вход 75 маскирования мультиплексора 64 является информационным входом 48 (49) блока 10 (11). Входы 76 и 77 управления сдвигом соответственно мультиплексора 65 сдвига и мультиплексора 64 образуют информационный вход 50 (51) блока 10 (11), Управляющие входы 78-81 соответственно первого 62, второго 63 регистров исходных данных, мультиплексора 64 и мультиплексора 65 сдвига, образуют уп- равпяющий вход 53 (управляющий вход 54) блока 10 (11). Выход 82 мультиплексора 64 является выходом 32 (33) блока 10 (11), выход 83 мультиплексора 65 сдвига является выходом 40 (41) блока 10 (11).

Команды процессора, служащие для обработки полей переменной длины, имеют, как правило, формат память-память. В большинстве современных ЭВМ, включая ЕС ЭВМ, в команде задаются адреса и длины первого и второго операндов, результат операции записывается на место первого операнда. На расположение операндов относительно целочисленных границ памяти не накладывается существенных ограничений, т.е. операнды (поля данных) могут начинаться с любого байта и заканчиваться любым байтом в пределах слова памяти. При обработке данных переменной длины на основном оборудовании процессора блоками данных, формат которых (полуспово, слово и т.п.) совпадает с форматом основных средств обработки, в первую очередь арифметико-логического устройства, обычно выделяют следующие этапы: выборка операндов из основной памяти; выравнивание операндов относительно друг друга (так, чтобы позиции одноименных байтов в пределах целочисленных границ у обоих операндов совпадали); выполнение операции; запись результата в основную память (на место первого операнда).

Устройство работает следующим образом,

В процессе выборки из основной памяти (на фиг. 1 не показана) слова операндов поступают на шины 3 и 4 данных, являющиеся информационными входами-выходами 7 и 8 устройства, и через входы 28 и 30 по сигналам с шины 21 записываются в блок 9 памяти. Для выравнивания, например, второго операнда относительно первой границы первого операнда определяется параметр сдвига, указывающий направление сдвига и количество разрядов, на кото- чрое необходимо сдвинуть второй операнд. Определение параметра сдвига осуществляется по значениям двух младших разрядов адресов крайних правых байтов первого

и второго операндов и может быть выполнено двумя путями. В первом случае в состав блока 14 управления сдвигом вводится специальное оборудование, которое вычисляет

параметр сдвига. Для этого вход 15 управления сдвигом устройства должен быть подключен к шинам 1 и 2 данных, на которые из блока 9 памяти через выходы 22 и 25 должны считываться адреса (или младшие разряды

0 адресов) крайних правых байтов обоих операндов.

Для малых универсальных ЭВМ, например терминальных ЭВМ, для которых весьма актуальным является экономия

5 оборудования, целесообразнее определять параметр сдвига микропрограммным способом путем анализа кодов крайних правых байтов обоих операндов. В этом случае управление сдвигом второго операнда осуще0 ствляется через блок 14 управления сдвигом по сигналам от блока микропрограммного управления (на фиг. 1 не показан), подаваемым через вход 15 устройства.

Функции сдвига в предлагаемом уст5 ройстве реализуются блоками 10 и 11 (фиг. 2). Для этого выход 74 регистра 63 подключен к входам 72 и 73 мультиплексора 64 так, чтобы получить на выходе 82 мультиплексора 64 по сигналам управления, поступаю0 щим-через входы 77 и 80, информацию, сдвинутую соответственно влево и вправо, При выполнении сдвига на четыре разряда к входу 42 коммутатора 12 подключается выход 41 блока 11, при сдвиге на один

5 разряд к входу 42 коммутатора 12 подключается выход 40 коммутатора 10.

Младшее полуслово сдвинутого на четыре разряда слова второго операнда с выхода 33 блока 11 поступает на вход 35 блока

0 13, настроенного через управляющий вход 56 на функцию транзита по входу 35. С выхода 38 блока 13 младшее полуслово поступает на вход 39 коммутатора 12. Последний по сигналу на входе 55 осуществляет прямое

5 подключение входов 42 и 39 на выходы соответственно 31 и 29 либо перекрестное подключение указанных входов на выходы 32 и 29. Подобная организация коммутатора 12 обеспечивает удобство компоновки дан0 ных, например, записываемых в блок 9 памяти. С выходов 29 и 31 коммутатора 12 сдвинутое слово второго операнда через шины 3 и 4 данных записывается в блок 9 памяти.

5 Аналогично выход 70 регистра 62 подключен к еходам 67 и 68 мультиплексора 65 сдвига так, чтобы получать на выходе 83 мультиплексора 65 по сигналам управления, поступающим через входы 76 и 81, информацию, сдвинутую соответственно влево и

вправо. Через первый 69 и второй 71 входы мультиплексора 64 информация с выходов 70 и 74 соответственно регистров 62 и 63 передается на выход 82 мультиплексора 64 без сдвига. Занесение информации в регистры 62,и 63 через входы 66-1 и 66-2 соответственно осуществляется по сигналам шины 21, поступающим через управляющие входы 78 и 79.

Для малых универсальных ЭВМ, в частности терминальных ЭВМ, необходимым и достаточным является наличие возможности сдвига информации на один и четыре разряда влево и вправо. Наличие сдвига на один разряд обеспечивает реализацию команд сдвига, а также алгоритмов итеративного получения результата (умножения, деления и т.п.). С помощью сдвига на четыре разряда осуществляется обработка информации экономического характера, основными элементами которой являются цифры, зоны и тому подобное, представляющие собой четырехразрядные коды, а также реализация алгоритмов итеративного получения результатов, например, в командах обработки десятичных данных.

В предлагаемом устройстве сдвиг на четыре разряда реализуется в блоке 11, сдвиг на один разряд - в блоке 10. Слово второго операнда по сигналам шины 21 управления, поступающим через управляющий вход 52, считывается на шинах 1 и 2 данных и через входы 24 и 27 по полусловам поступает в блок 11, где по сигналам управления, поступающим через входы 54 и 51, осуществляется его сдвиг на четыре разряда в требуемом направлении. Выход 83 мультиплексора 65 выполнен на элементах, допускающих непосредственное объединение по входу (например, мультиплексор 65 может быть реализован на микросхемах К555КП11, имеющих выход с тремя состояниями).

В командах десятичной арифметики (ЕС ЭВМ) размер операндов не превышает 16 байтов, поэтому в них, как правило, выравниванию подвергается весь операнд. В командах логической обработки данных переменной длины, в которых максимальная длина операнда может составлять 256 байтов, выравнивание производится последовательно блоками определенной длины.

Если операнд (или его часть) состоит из нескольких слов, описанная процедура сдвига повторяется необходимое число раз. В результате весь операнд (или определенная его часть) оказывается сдвинутым на четыре разряда. Циклы сдвига операнда на четыре разряда повторяются столько раз, сколько это необходимо для выравнивания второго операнда или его части относительно первого операнда. В частности, позиции крайних правых байтов операндов в пределах полуслова могут отличаться не более чем на один байт, поэтому при ориентации

на обработку полусловами (что характерно для малых ЭВМ) выравнивание либо не требуется, либо выполняется за два последовательных цикла сдвига на четыре разряда. В ходе подготовки к выполнению опера0 ции, а во многих командах - и во время выполнения операции над словами (полусловами) операндов, интенсивно используется аппарат маскирования. Аппарат маскирования обеспечивает обнуление не5 нужной (паразитной) информации главным образом слева и справа от левой и правой границ операнда соответственно, а также используется для выделения различных частей операндов, их сочленения и т.д. В

0 предлагаемом устройстве аппарат маскирования обеспечивает формирование и наложение тетрадных масок, что позволяет эффективно обрабатывать данные переменной длины на уровне их элементарных со5 ставляющих (цифр, знаков, зон и т.п.).

Маскирование информации, поступающей на вход 34 арифметико-логического блока 13, осуществляется в блоке 10 с помощью маски, вырабатываемой шифрато0 ром 19 маски. Маскирование информации, поступающей на вход 35 блока 13, осуществляется в блоке 11 с помощью маски, вырабатываемой шифратором 20. Вид маски определяется информацией, записанной в

5 регистр 16 маски (для первого 19 и второго 20 шифраторов маски) либо в регистр 18 тетрадных переносов (только для шифратора 20).

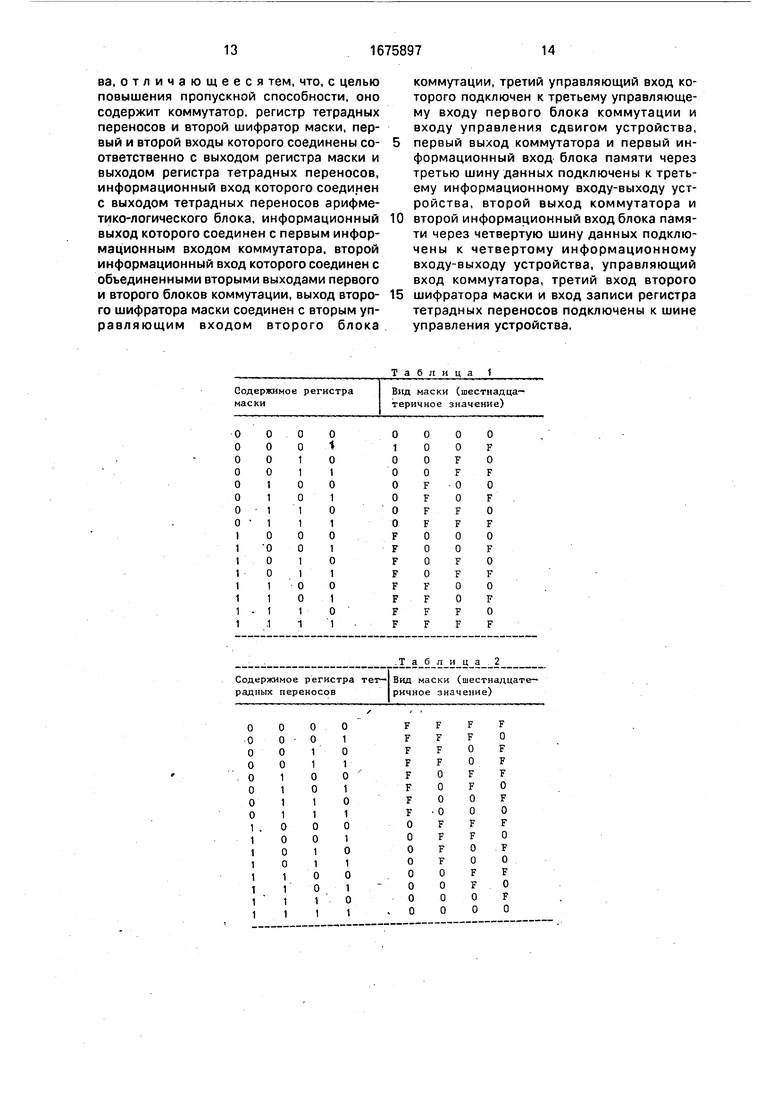

Шифратор 19 маски работает в двух ре0 жимах и может управляться с помощью одного разряда микрокоманды: 0 - нет маскирования (фактически маскирование с помощью маски FFFF для полуслова, где F (1111)2); 1 - маскирование с помощью маски,

5 записанной в регистр 16 маски в соответствии с табл. 1 (для полуслова).

Шифратор 20 маски работает в четырех режимах и может управляться с помощью двух разрядов микрокоманды: 00 - нет мас0 кирования (равносильно формированию для полуслова единичной маски FFFF); 01 - маскирование с помощью маски, записанной в регистр 18 тетрадных переносов в соответствии с табл. 2 (для полуслова); 11 - маски5 рование с помощью маски, записанной в регистр 16 маски в соответствии с табл. 3 (для полуслова).

Занесение информации в регистр 16 маски производится по сигналу шины 21, подаваемому через управляющий вход 58.

Вход регистра 16 маски, являющийся входом 17 маски устройства, может быть подключен непосредственно к управляющей памяти (памяти микрокоманд) процессора (на фиг. 1 не показана), в этом случае маска является одним из полей микрокоманды и может изменяться в каждом такте (цикле) работы устройства.

В предпочтительном варианте реализации блоков 10 и 11 (фиг. 2) непосредственно операция маскирования выполняется в мультиплексоре 64, при подаче на вход 75 маскирования которого нулевого значения маски с его выхода 82 считывается нуль независимо от значения входной информации. При построении мультиплексора 64 на микросхемах, например, К531КП2 и их функциональных аналогах функция маскирования реализуется элементарным образом.

Обработка десятичных данных в рассматриваемом устройстве не требует схемы коррекции +Ю и выполняется следующим образом. Для того, чтобы двоичный перенос идентифицировал десятичный перенос при сложении двух двоично-десятичных чисел, один из операндов должен быть представлен в коде с избытком 6. Получение одного из операндов в коде с избытком 6 производится путем его сложения на арифметико- логическом устройстве с константой 6666 (для полуслова) в шестнадцатеричном представлении. С этой целью полуслова операнда считываются из блока 9 памяти на одну из шин данных, например шину 1 данных, на другую шину данных (шину 2 данных) считывается, например, из зоны константы с микрокоманды или из ПЗУ констант (на фиг. 1 не показаны) константа 6666. Далее через блоки 10 и 11 слагаемые подаются на входы соответственно 34 и 35 блока 13, с выхода 38 которого очередное полуслово операнда в коде с избытком 6 поступает на вход 39 коммутатора 12. Последний обеспечивает выдачу информации как на шину 3 данных, так и на шину 4 данных, с которых она может быть записана в блок 9 памяти.

При слржении в арифметико-логическом устройстве одного из операндов с другим, представленным в коде с избытком 6, тетрадные переносы по сигналу с шины 21, подаваемому через управляющий вход 59, фиксируются в регистре 18 тетрадных переносов. При этом справедливо следующее правило: тетрады результата, из которых не было переноса, получены в коде с избытком 6, и требуют корректировки; тетрады результата, из которых был перенос, получены в коде 8421 и не требуют корректировки. Полуслово результата, отдельные тетрады которого требуют корректировки, с выхода

38 блока 13 через коммутатор 12 записывается в блок 9 памяти и в следующем цикле (такте) работы устройства считывается на шину 1 данных для корректировки. Корректировка производится с помощью константы 6666, использовавшейся при получении одного из операндов в коде с избытком 6 и хранящейся в регистре 63 коммутатора 11 либо вновь считываемой на шину 2 данных

из зоны константы микрокоманды или ПЗУ констант. Корректировка заключается в вычитании из полуслова результата, требующего корректировки, константы 6666, отмаскированной с помощью маски, вид которой определяется содержимым регистра 18 тетрадных переносов в соответствии с табл. 2. Откорректированное полуслово результата записывается в блок 9 памяти. Аналогично обрабатываются все последующие

полуслова операндов.

П р и м е р 1. Сложить числа 1234 и 5678. Получение числа 1234 в коде с избытком

1234

+ 6666

789А (шестнадцатиричное значение) Выполнение операции сложения

результат

(неоткорректиро- ванный) тетрадные переносы

789А + 5678

-CF12 (шестнадцатиричное значение)

-0011

(двоичное значение)

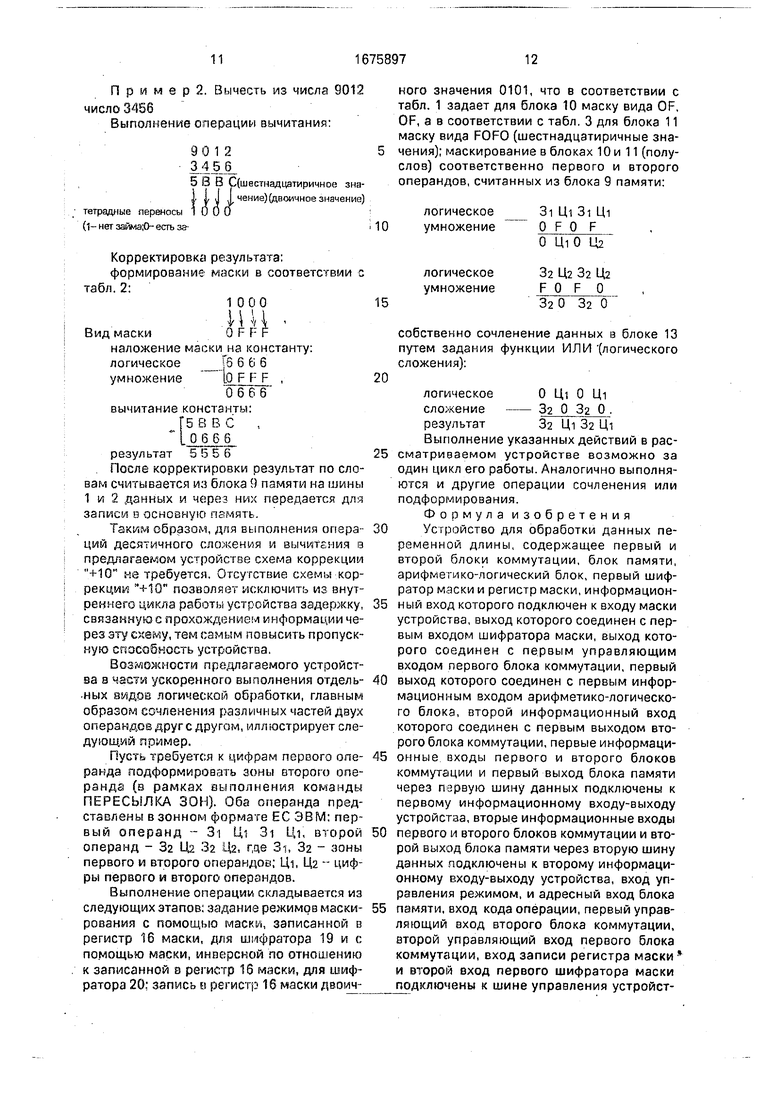

Корректировка результата: формирование маски в соответствии с табл 2:

содержимое регистра0011

тетрадных переносов

вид маски (шестнадцати-FFOO ричное значение) наложение маски на константу (в коммутаторе 11): Г

логическое 6666 умножениеF F О О

6600

вычисление константы:

CF 1 2 - 6 6-0 О

результат 6912

При вычитании двоично-десятичных чисел этап получения одного из операндов в коде с избытком 6 опускается. Корректировка цифр результата выполняется аналогично случаю сложения.

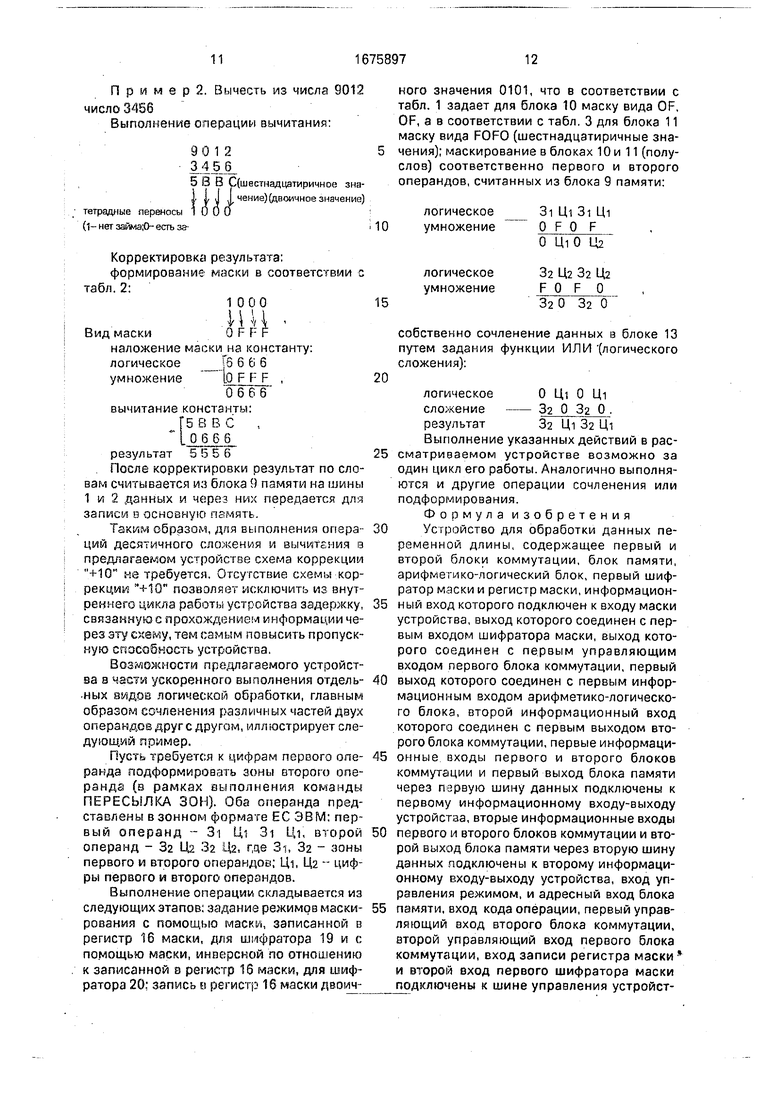

П р и м е р 2. Вычесть из числа 9012

число 3458

Выполнение операции вычитания:

9012 3456

5 В В ((шестнадцатиричное зна- 1 У 3 1чение) (Двоичное значение)

тетрадные переносы (1 - нет займами есть заКорректировка результата: формирование маски в соответствии с табл. 2:

1 000

OFFF

Вид маскиО

наложение маски на константу:

логическоеГб 666

умножение 0 F F F , 0666

вычитание константы: 5 В В С , 0666

результат 5556

После корректировки результат по словам считывается из блока 9 памяти на шины 1 и 2 данных и через них передается для записи в основную память.

Таким образом, для выполнения операций десятичного сложения и вычитания в предлагаемом устройстве схема коррекции +10И не требуется. Отсутствие схемы коррекции +10 позволяет исключить из внутреннего цикла работы устройства задержку, связанную с прохождением информации через эту схему, тем самым повысить пропуск- нуга способность устройства.

Возможности предлагаемого устройства в части ускоренного выполнения отдель- ных видов логической обработки, главным образом сочленения различных частей двух операндов друг с другом, иллюстрирует следующий пример.

Пусть требуется к цифрам первого операнда подформировать зоны второго операнда (в рамках выполнения команды ПЕРЕСЫЛКА ЗОН). Оба операнда представлены s зонном формате ЕС ЭВМ: первый операнд - 3i Lb 3i Ui, второй операнд - 32 Ц2 32 Ца, где 3i, 32 - зоны первого и второго операндов; Ui, Ц2 - цифры первого и второго операндов.

Выполнение операции складывается из следующих этапов: задание режимов маскирования с помощью маски, записанной в регистр 16 маски, для шифратора 19 и с помощью маски, инверсной по отношению к записанной в регистр 16 маски, для шифратора 20: запись в регистр 16 маски двоичного значения 0101, что в соответствии с табл. 1 задает для блока 10 маску вида OF, OF, а в соответствии с табл. 3 для блока 11 маску вида FOFO (шестнадцатиричные зна- чения); маскирование в блоках 10 и 11 (полуслов) соответственно первого и второго операндов, считанных из блока 9 памяти:

логическое умножение

логическое умножение

3i ui3i Ui

О F О F О ЦтО Ц2

32 Ц2 За Lb FOFO

320 32 О

20

собственно сочленение данных в блоке 13 путем задания функции ИЛИ (логического сложения):

логическое

сложение

результат

О Цт 0 Ui

32 0 32 0 .

32 Ui 32 Ui Выполнение указанных действий в рас5 сматриваемом устройстве возможно за один цикл его работы. Аналогично выполняются и другие операции сочленения или подформирования.

Формула изобретения

0 Устройство для обработки данных переменной длины, содержащее первый и второй блоки коммутации, блок памяти, арифметико-логический блок, первый шифратор маски и регистр маски, информацион5 ный вход которого подключен к входу маски устройства, выход которого соединен с первым входом шифратора маски, выход которого соединен с первым управляющим входом первого блока коммутации, первый

0 выход которого соединен с первым информационным входом арифметико-логического блока, второй информационный вход которого соединен с первым выходом второго блока коммутации, первые информаци5 онные входы первого и второго блоков коммутации и первый выход блока памяти через первую шину данных подключены к первому информационному входу-выходу устройства, вторые информационные входы

0 первого и второго блоков коммутации и второй выход блока памяти через вторую шину данных подключены к второму информационному входу-выходу устройства, вход управления режимом, и адресный вход блока

5 памяти, вход кода операции, первый управляющий вход второго блока коммутации, второй управляющий вход первого блока коммутации, вход записи регистра маски и второй вход первого шифратора маски подключены к шине управления устройства, отличающееся тем, что, с целью повышения пропускной способности, оно содержит коммутатор, регистр тетрадных переносов и второй шифратор маски, первый и второй входы которого соединены соответственно с выходом регистра маски и выходом регистра тетрадных переносов, информационный вход которого соединен с выходом тетрадных переносов арифметико-логического блока, информационный выход которого соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с объединенными вторыми выходами первого и второго блоков коммутации, выход второго шифратора маски соединен с вторым уп- равляющим входом второго блока

Содержимое регистра маски

Содержимое регистра тетрадных переносов

коммутации, третий управляющий вход которого подключен к третьему управляющему входу первого блока коммутации и входу управления сдвигом устройства,

первый выход коммутатора и первый информационный вход блока памяти через третью шину данных подключены к третьему информационному входу-выходу устройства, второй выход коммутатора и

второй информационный вход блока памяти через четвертую шину данных подключены к четвертому информационному входу-выходу устройства, управляющий вход коммутатора, третий вход второго

шифратора маски и вход записи регистра тетрадных переносов подключены к шине управления устройства.

Таблица 1

Вид маски (шестнадца- теричное значение)

Таблица 2

Вид маски (шестнадцате- ричное значение)

Таблица 3

Содержимое регистра маски

Вид инверсной маски

(шестнадцатеричное

значение)

| МЕХАНИЧЕСКАЯ ТРАМБОВКА ДЛЯ ИЗГОТОВЛЕНИЯ ИСКУССТВЕННЫХ ЖЕРНОВОВ | 1923 |

|

SU1033A1 |

| В.А.Комарницкого, Г.П.Сорокина | |||

| - М.: Машиностроение, 1982, с.61, 69-71 | |||

| Патент США №4219874, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-07—Публикация

1986-10-02—Подача