Изобретение отиосптея к области радиотехники и может быть использовано в измерителях коэффиииента стоячей волиы в СВЧ-технике, а также в схемах спектрометров и сиектросЬотометров.

Известно ycTpoiiCTBO, содсржаи1ее схему сравнения, на один вход которой подается первый входной сигнал, а на второй - выход иитегратора, вход которого иодключен к выходу ключа, прерываюгцего второй входной сигнал, а управляющий вход соединен с выходиой клеммой и выходом широтно-импульсного модулятора, вход которого через усилитель подключен к выходу ехемы сравнения, а второй вход - к генератору тактовых импульсов 1.

Недостатком этой схемы является нпзкнй коэффициент подавлення синфазной составляющей, так как однн входной сигнал ннте-. грируется и сравниваетея с мгновенным значением второго, следовательно, в случае присутствия выброса иоказапие ирибора будет неверное. К тому же такого рода схемы теряют информацию о нроцессах за счет иитегрироваипя лищь одного сигнала, что ограннчнвает их быстродействие.

Извеетно также устройство для измереп гя отнощения, содержащее первый интегратор, выход которого соединеи с первым разрядным ключом н с первым входом ехемы сраппення, нсточннк опорного спгнала, второй ннтегратор. выход которого соединен с выходио шглюй ycTpoiiCTBU и вторым разрядным ключом .

о Недостатком это10 ттройства яв.1яется низкий коэффпдионт подавления сиифазиой сост; В.1Я1ои1,ей, так как одии из сигна.юв ннтегрнруется н сравнивается с мгновенным значением второго, кроме того, в случае

10 иитегрирования одиого сигнала иолучается иедостовсрная ннформацня, так как в обHieM случае ее несет отнощеине ннтегральиых зиачеиий обоих енгналов.

Целью изобретения является увелпчеиие

ЬЗ коэффициеита иодавления сиифазной составляющей и повыщение достоверности информации иоередством одиовремениого ннтегрнровання еигиалов и еравиения одного из инх с онорным.

20 Поставленная цель доетигается тем, что в измеритель отнощетщя, еодержаиип) иерBbiii пптегратор. выход которого соединен е первым разрядным ключом н е нервым входом схемы еравпения. неточник опорного

2.5 .еигиала, второй интегратор, выход которого соедннен с выходноГ щино) ycTpoiicTBa и вторым разрядиым ключо у1, введеиы трети) и четвертый разрываюище ключи, тригге 1 и линия задержки, иричем ннвертироваииьп

30 выход триггера иодключен к унравляюихим

выходам первого, третьего, четвертого и через линию задержки второго ключей, третий разрывающий ключ подключен входом ко второй входной шиие устройства п выходом - ко входу второго интегратора, а четвертый - входом к иервой входной шине устройства, а выходом - ко входу первого интегратора; выход схемы сравнений нодключен к / -входу триггера, к 5-входу которого нодключеиа входная шина синхронизации, а выход источ ;нка онорного сигиала подключен ко второму входу схемы сравнения.

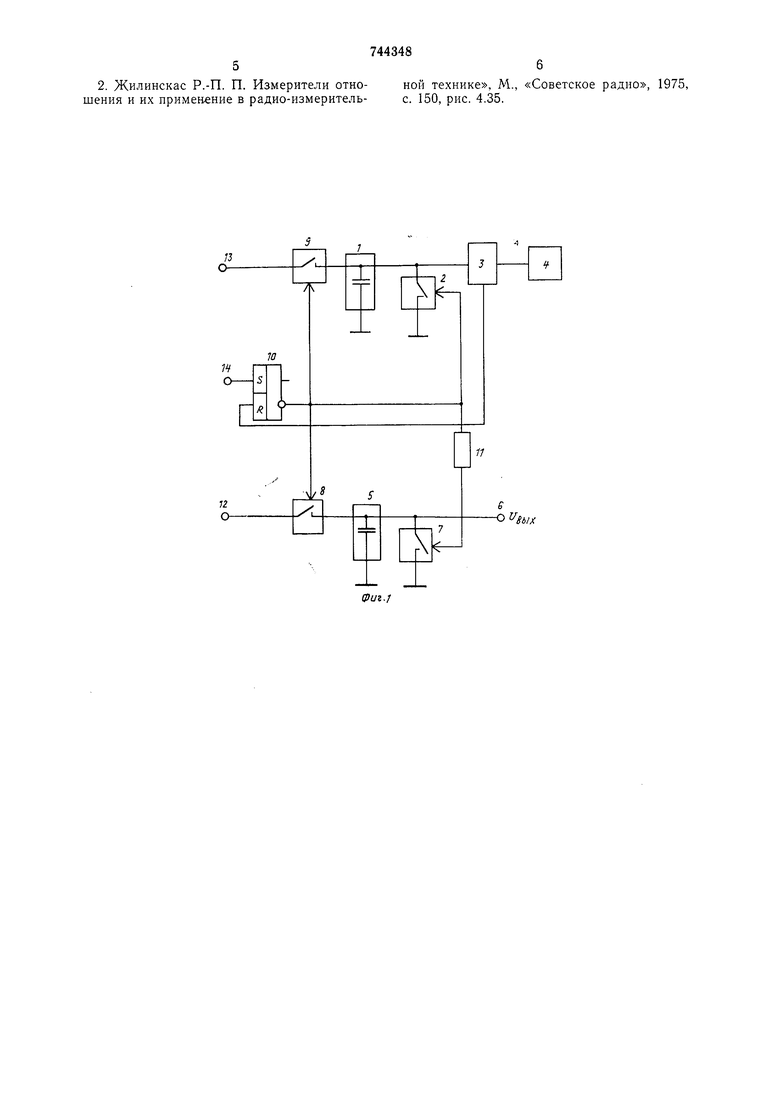

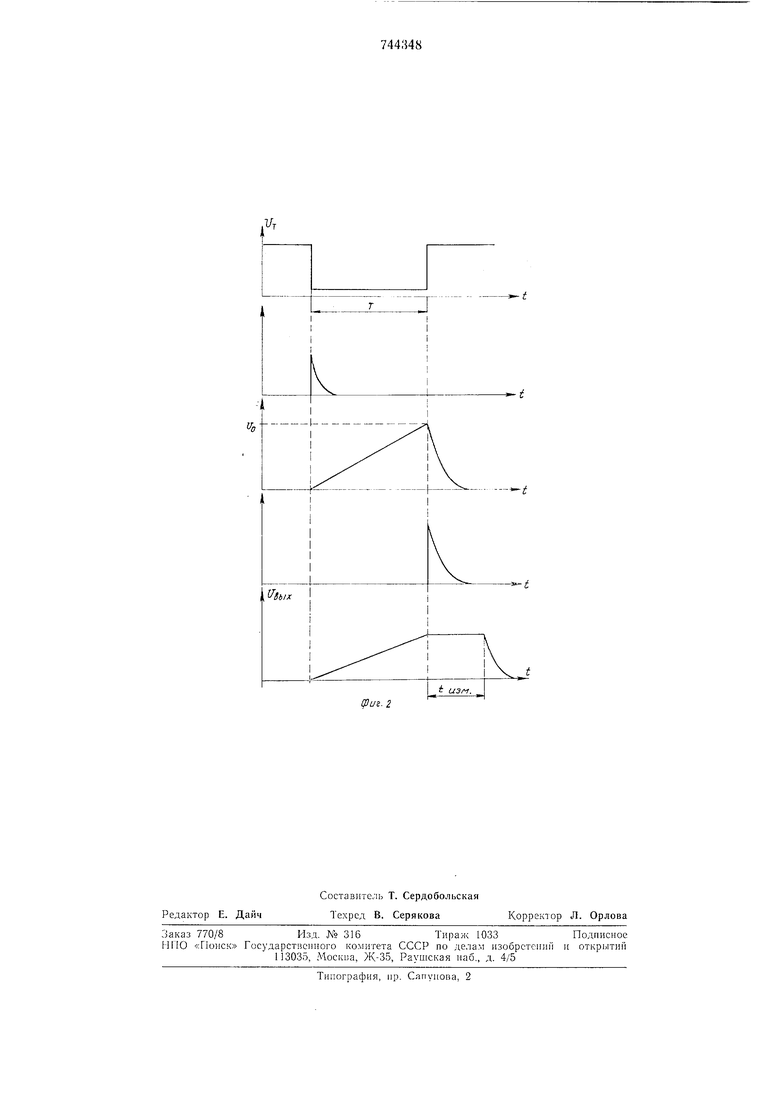

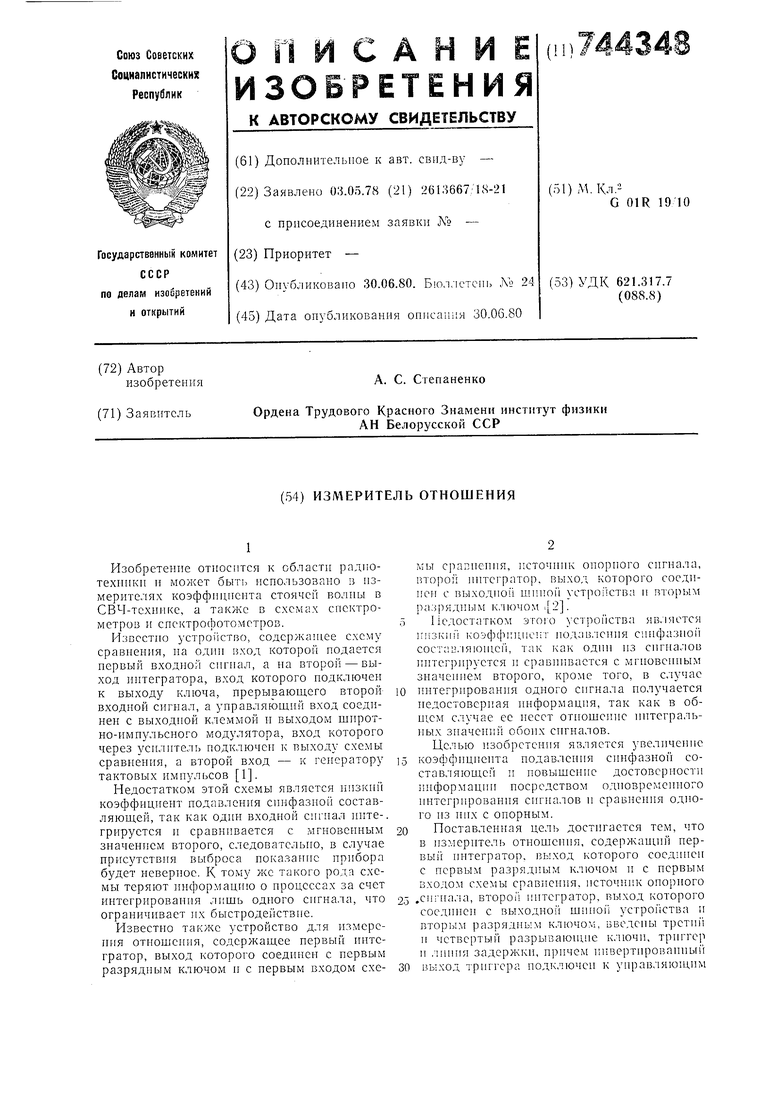

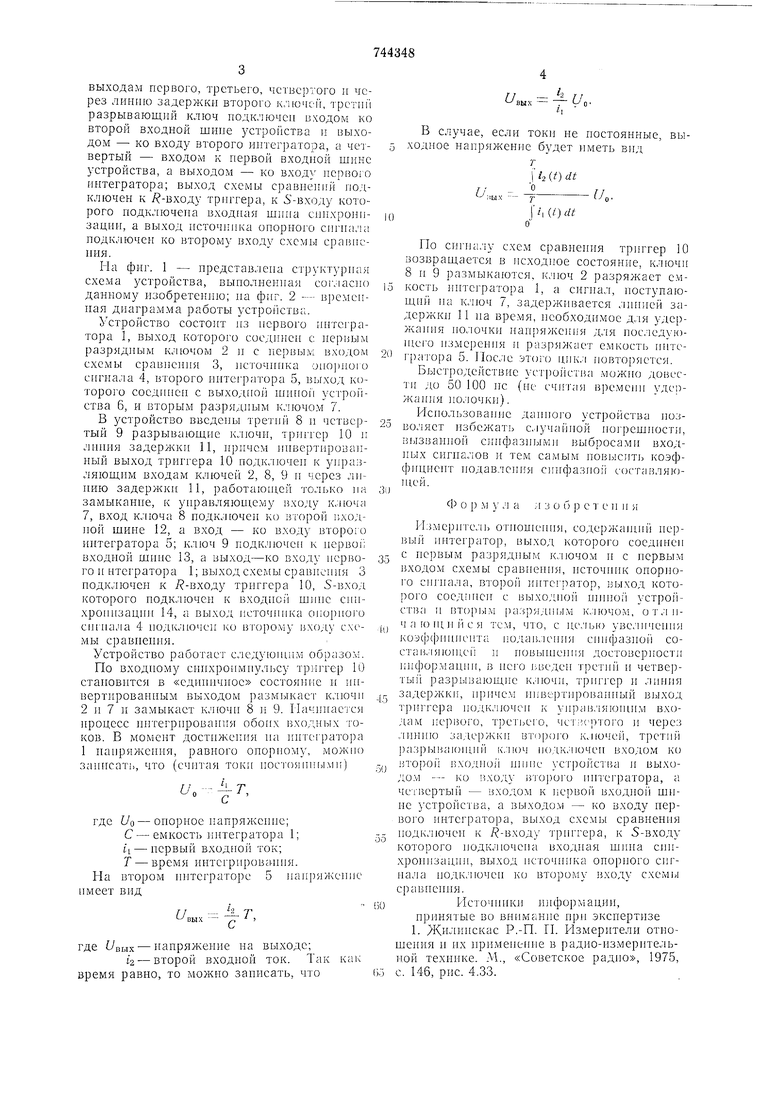

На фиг. 1 - представлена етруктурнаи схема устройства, вынолненная coiviacno данпому изобретению; на фиг. 2 -- временная днагра.м.ма работы устройства.

Устройство состоит из первого иитсгратора 1, выход которого сосдинеи с первым разрядным ключом 2нс первым входом схемы сравпсппя 3, источпнка оио)1шго сигнала 4, второго интегратора 5, выход которого соедииен с выходной Н1иио1| устройства 6, н вторым разрядиым ключом 7.

В устройство введены третий 8 и четвертый 9 разрывающие ключи, триггер 10 п лнння задержки И, причем инвертированный выход триггера 10 нодключеи к управляющим входам ключей 2, 8, 9 и через линию задержки 11, работаюи1,ей 1олько на замыкание, к уиравляюи1,ему входу ключа 7, вход ключа 8 иодключеп ко второй пходной шиие 12, а вход - ко входу второго интегратора 5; ключ 9 подключеи к нервоГ: входной щнне 13, а выход-ко входу первого н нтегратора 1; выход схемв сравпеиня 3 подключен к / -входу триггера 10, S-вход которого иодключен к входной еиихроинзацин 14, а выход псточипка опорпого сигпала 4 подключен ко второму входу схемы сравнения.

Устройство работает еледуюп1им образом.

По входиому енихроимнулвсу триггер 10 етановнтся в «единичное состояние п иивертироваииым выходом размыкает ключи 2 и 7 п замыкает ключи 8 н 9. Пачннаетея процесс иитегрироваиия обоих входных токов. В момент достнженпя на интегратора 1 нанриження, равного опорному, можио заиисать, что (считая токи ностояипимп)

- IL т

L с

где Lo - опорное напряжение;

С - емкость интегратора 1;

tl - иервв1Й ток;

Т - время интегрирова-иия. На втором иитеграторе 5 нап)яже1И1е имеет вид

2 Т

и

:х ВЫ

где t/Bbix - нанряженне на выходе;

г2 - второй входной ток. Так как время равно, то можио заиисать, что

и - з /7

-вы.ч - Т - О i

В случае, если токи ие иоетояиные, выходпое напряжеиие будет иметь вид т

i 4 (О dt

Г -

(Г.. -- -J

/, (О dt

Но сигиалу схем сравпеиня тр1итер 10 возвращаетея в исходное состояние, ключи 8 и 9 размыкаютея, ключ 2 разряжает емo кость нитегратора I, а сигиал, иоступающий иа ключ 7, задержги ается лииисЧ задержки 11 иа время, необходимое для удержания иолочки иаиряжеп11я для иослсдуюИ1его измерения и разряжает емкость И1гге г)атора 5. После этого цик. повторяется.

Быстродейетвие устройства м(;жно д.овести до 50 100 НС (ие сч1ггая в)емепп удеожаиия полочки).

Нсиользоваиие даппого устройства 1юз5 воляст избежать с.1учайной ногрешности, В,1зваииой снифазиыми выбросами входных епгиа.лов и тем самым повыеить коэффпцнепт подавления синфазноГ составляю0 о р м у л а .т 3 о б э е т е и п si

Из.мерп1х :1ь отношегни, еодержащпй иервый интегратор, выход которого еоединеи с иервым разрядиым к.лючом н с первым входом схемы сравиення, нсточннк онориого сигиала, интегратор, выход которого соединен с выходной ттюй устройства и вторым |)а,)ядпым к.лючом, от.1ич а IO 1Н и и с я тем, что, с це.лыо увелпченпя коэф(|лии1епта подавлеиия сипфазпой состав.-|яюи1,ей и повьииеиия достовериости ппформацпп, в пего 1:.ведеи т) и четверTbui разрывающие ключи, триггер и линия задержки, иргигем 1И1В :ртироваииый выход т 1нггера подключеп к управ.чяклнн.м вхо дам первого, третье1о, чст сртого н через .пп-ппо заде|) вто)()1о ключе , третий ()И,Й к.иоч 1()дключен входом ко iJTOpoii устройет1 а выходо.м - о входу 1те -ратора, а

четвертый - входом к 1ервой шнне устройства, а выходом - ко входу первого итегратора, выход ехе.мы еравнения одключеи к / -входу тр нтера, к S-входу

которого ВХОДИая СИ 1хрои 1заин, выход 1сточиика С и-на.ча ко второму входу схемы сравие 1ня.

Иеточ ип информации, ирииятые во нри экепертизе 1. Жнлипскас Р.-П. П. Измер1 телн отношения н нх ири.ме 1еиие в радио-измерительной техннке. М., «Советское радио, 1975, с. 146, рне. 4.33.

2. Жилинскас P.-П. П. Измерители отношения и их применение в радио-измерительной технике, М., «Советское радио, 1975, с. 150, рис. 4.35.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 1971 |

|

SU427488A1 |

| Цифровой компенсатор | 1972 |

|

SU439915A1 |

| УСТРОЙСТВО для КОМПЕНСАЦИИ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 1972 |

|

SU343272A1 |

| Устройство для телеуправления | 1978 |

|

SU769590A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО ПЕРЕМЕННОГО ТОКА | 1968 |

|

SU231899A1 |

| Частотно-импульсное множительноделительное устройство | 1975 |

|

SU595731A1 |

| СЧЕТЧИК ЭНЕРГИИ ПОСТОЯННОГО ТОКАВСЕСОЮЗНАЯПАТЕНТНО-][ХНГ:^"КАЯБИБЛИОТЕКА | 1970 |

|

SU283394A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СИГНАЛОВ | 1971 |

|

SU420082A1 |

| Устройство для контроля интегральных схем | 1975 |

|

SU558230A1 |

| Устройство для измерения экстремальных значений аналогового сигнала | 1978 |

|

SU744347A1 |

73

W

14

t

(риг. 2

Авторы

Даты

1980-06-30—Публикация

1978-05-03—Подача