(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частот | 1975 |

|

SU577527A1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ ПОДКЛЮЧАЕМЫХ НА ПАРАЛЛЕЛЬНУЮ РАБОТУ ГЕНЕРАТОРОВ | 2011 |

|

RU2460193C1 |

| Умножитель частоты | 1982 |

|

SU1083330A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПАРАМЕТРОВ ПОДКЛЮЧАЕМЫХ НА ПАРАЛЛЕЛЬНУЮ РАБОТУ ГЕНЕРАТОРОВ | 2014 |

|

RU2557672C1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1092717A1 |

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1990 |

|

RU2042264C1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

1

Изобретение относится к автоматике и вы числительной технике и может быть использовано в устройствах, требуюидах повышения частоты электрических сигналов.

Известно устройство для умножения частот, содержащее триггеры, элементы И, генератор управляемой частоты, делитель частоты, п-разрядные суммирующие и вьрштающие счетчики, осуществляющие преобразование входной частоты умножителя в цифровой код 1 .

Однако преобразование частоты в Щ1фровой код сопровождается погрешностью, пропорциональной величине дискретности сигнала, заполняющего п-разрядные вычитающие счетчики. Поэтому, обеспечивая дальнейшее расширение частотного диапазона и повышенное быстродействие, такой умножитель отличается недостаточной точностью умножения, а также cJioxdioCTbto технической реализации.

Наиболее близким техническим решением к предлагаемому изобретению является умножитель частоты, содержащий управляемый генератор, делитель частоты, выход которого соединен с первым входам первого элемента И и.

через элемент задержки, с первым входом первого триггера, первый выход которого подI ключей ко второму входу первого и первому входу второго элементов И, второй выход пер; вого триггера подключен к первым входам третьего и четвертого элементов И, второй вход первого триггера через второй элемент задержки соединен со входом устройства и вторым входом третьего элемента И, выходы первого и третьего элементов И подключены, со10ответственно, к первому и второму входам эторого триггера, выходы которого подйлючены, соответственно, ко вторым входам второго и четвертого элементов И, выход которого подключен к первому входу интегратора, вы15ход которого подключен ко входу )пправляемого генератора, выход которого соеданея с выходом змиожителя и в 4одом делителя частоты 2.

Недостатком умножителя является низкая

20 точность и ограниченный диапазон коэффшщен-. тов умножения.

Цель изобретения - повышение точности и расширение диапазона умножения.

Цель изобретения достигается тем, что умножитель содержит первый и второй элементы НЕ, пятый и шестой элементы И и одновибратор, вход которого подключен ко входу умножителя, выход - к первому входу пятого элемента И и,через первый элемент НЕ, к первому входу шестого элемента И, вьисод которого подключен к первому входу интегратора, второй вход которого подключен к выходу пятого элемента И, второй вход которого подключен к выходу второго элемента И и входу второго элемента НЕ, выход которого подключен ко второму входу шестого элемента И.

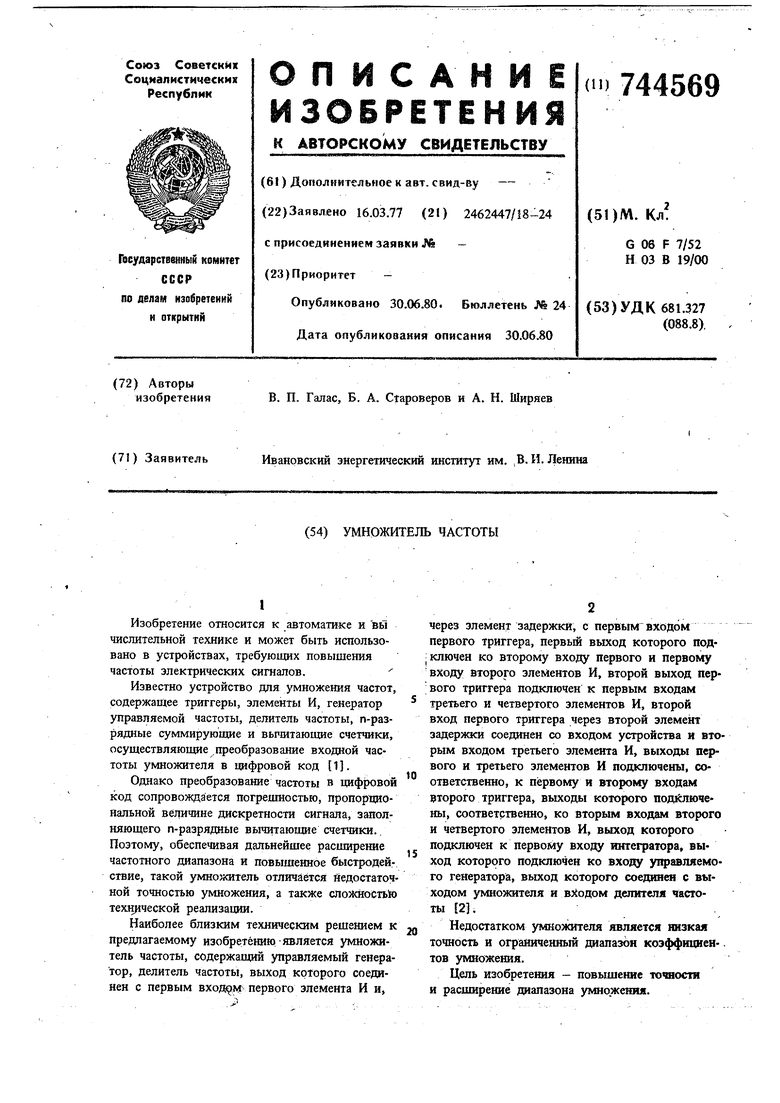

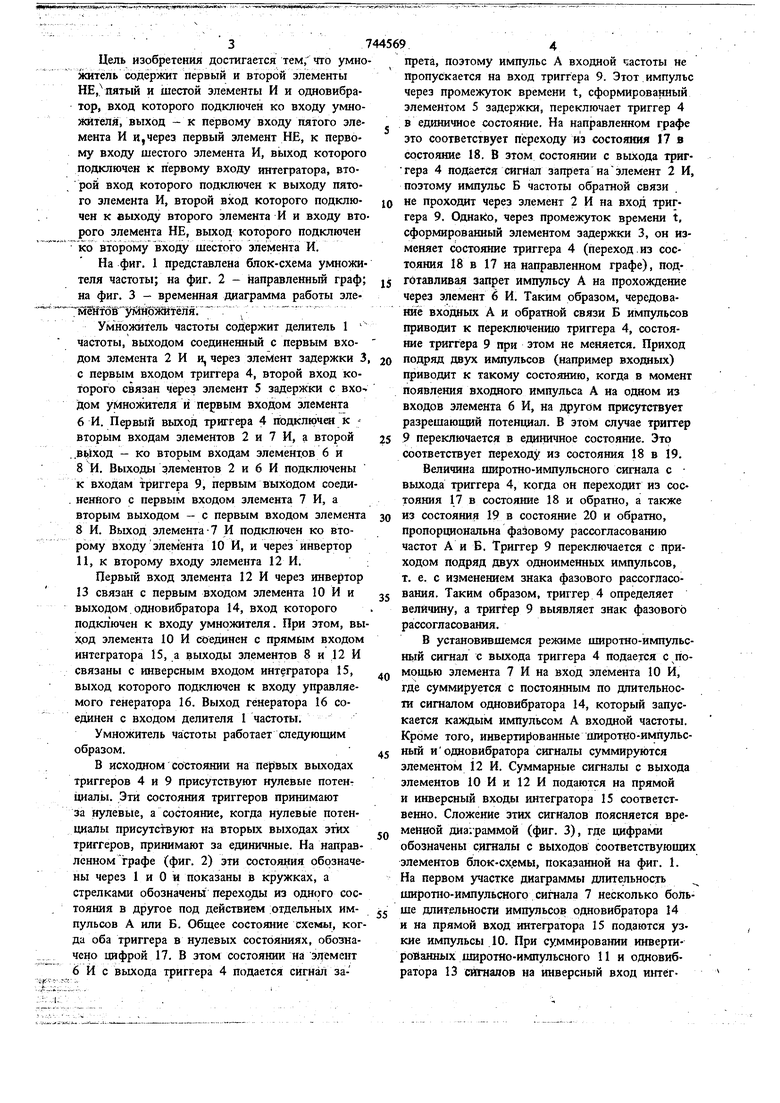

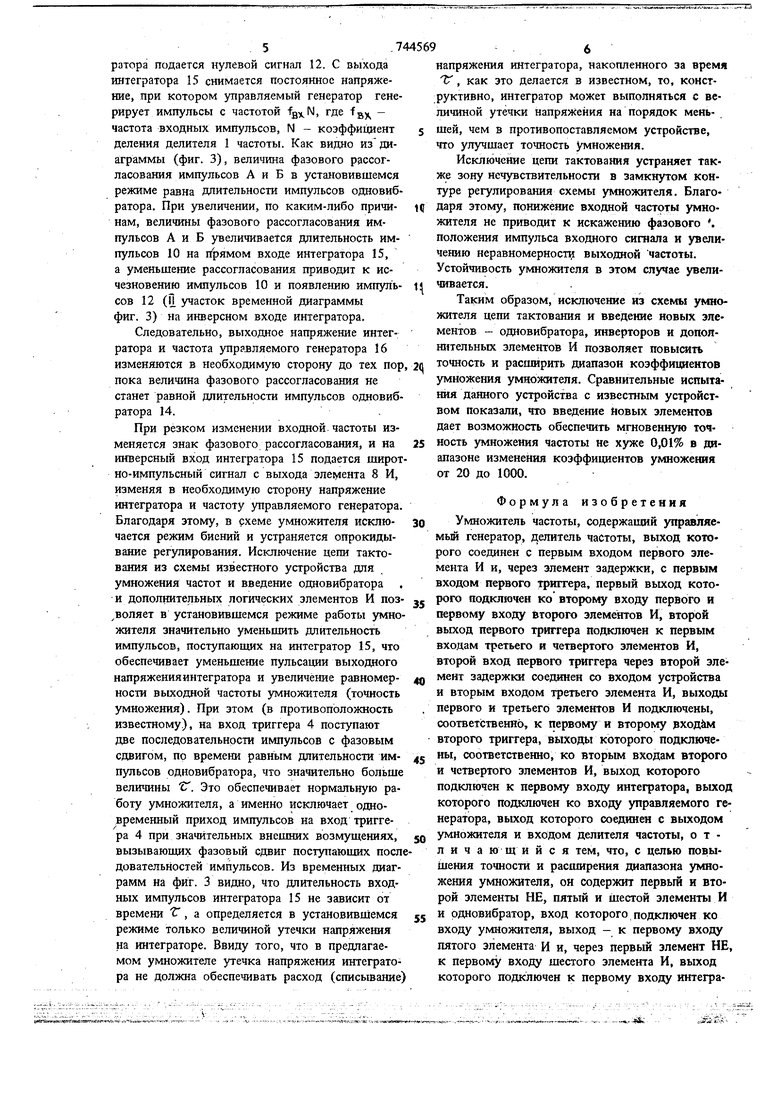

На фиг, 1 представлена блок-схема умножителя частоты; на фиг. 2 - направленный граф; на фиг. 3 - временная диаграмма работы эле ТйШтб5Гу1Й}ШаггёляГ Г

Умножитель частоты содержит делитель 1 частоты, выходом соединенный с первым входом элемента 2 И и, через элемент задержки 3 с первым входом триггера 4, второй вход которого связан через элемент 5 задержки с вхо дом умножителя и первым входом элемента 6 И. Первый вькод тржтера 4 подключая к ; вторым входам элементов 2 и 7 И, а второй

..вмход - ко вторым входам элементов 6 и 8 И. Выходы элементов 2 и 6 И подключены к входам триггера 9, первым выходом соеди. венного с первым входом элемента 7 И, а вторым выходом - с первым входом элемента 8 И. Выход элемента-7 И подключен ко второму входу элемента 10 И, и через инвертор 11, к второму входу элемента 12 И.

Первый вход элемента 12 И через инвертор 13 связан с первым входом элемента 10 И и выходом. одновибратора 14, вход которого подключен к входу умножителя. При этом, выход элемента 10 И соединен с прямым входом интегратора 15, а выходы элементов 8 и 12 И связаны с инверсным входом интегратора 15, выход которого подключен к входу управляемого генератора 16. Выход генератора 16 соединен с входом делителя 1 частоты.

Умножитель частоты работает следующим образом.

В исходном состоянии на первых выходах триггеров 4 и 9 присутствуют нулевые потент циалы. Эти состояния триггеров принимают за нулевые, а состояние, когда нулевые потенциалы присутствуют на вторых выходах эттис триггеров, принимают за единичные. На направленном графе (фиг. 2) эти состояния обозначены через 1 и О и показаны в кружках, а стрелками обозначены переходы из одного состояния в другое под действием :отдельных импульсов А или Б. Общее состояние схемы, когда оба триггера в нулевых состояниях, обозначено цифрой 17. В этом состоянии на элемент бис выхода триггера 4 подается сигнал запрета, поэтому импульс А входной частоты не Пропускается на вход триггера 9. Этот импульс через промежуток времени t, сформированный элементом 5 задержки, переключает триггер 4 в единичное состояние. На направленном графе это соответствует переходу из состояния 17 в состояние 18. В этом состоя1ши с выхода тригтера 4 подается сигнал запрета наэлемент 2 И, позтому импульс Б частоты обратной связи не проходит через элемент 2 И на вход триггера 9. Однако, через промежуток времени t, сформированный элементом задержки 3, он изменяет состояние триггера 4 (переход из состояния 18 в 17 на направленном графе), подготавливая Запрет импульсу А на прохождение через элемент 6 И. Таким образом, чередование входных А и обратной связи Б импульсов приводит к переключению триггера 4, состояние триггера 9 при этом не меняется. Приход подряд двух импульсов (например входных) приводит к такому состоянию, когда в момент появления входного импульса А на одаом из входов элемента 6 И, на другом присутствует разрешающий потенгщал. В этом случае триггер 9 переключается в еданичное состояние. Это соответствует переходу из состояния 18 в 19.

Величина широтно-импульсного сигнала с выхода триггера 4, когда он переходит из состояния 17 в состояние 18 и обратно, а также из состояния 19 в состояние 20 и обратно, пропорциональна фаговому рассогласованию частот Аи Б. Триггер 9 переключается с приходом подряд двух одноименных импульсов, т. е. с изменением знака фазового рассогласования. Таким образом, триггер 4 определяет величину, а триггер 9 выявляет знак фазового рассогласования.

В установившемся режиме широтно-импульсш.гй сигнал с выхода триггера 4 подается с помощью элемента 7 И на вход элемента 10 И, где суммируется с постоянным по длительности сигналом одновибратора 14, который запускается каждым импульсом А входной частоты. Кроме того, инверти{)ованныеШиротво-импульсный иодновибратора сигналы суммируются элементом 12 И. Суммарные сигналы с выхода элементов 10 И и 12 И подаются на прямой и инверсный входы интегратора 15 соответственно. Сложение этих сигналов поясняется временной диаграммой (фиг. 3), где цифралш обозначены сигналы с выходов соответствующих элементов блок-сх.емы, показанной на фиг. 1. На первом з астке диаграммы длительность широтно-импульсного сигнала 7 несколько больше длительности импульсов одновибратора 14 и на прямой вход интегратора 15 подаются узкие импульсы 10. При суммировании инвертированных широтяо-импульсного 11 и одновибратора 13 сигналов на инверсный вход mnrer5.7 ротора подается нулевой сигнал 12. С выхода интегратора 15 снимается постоянное напряжение, при котором управляемый генератор генерирует импульсы с частотой faxl ГЯ6 fftx частота входных импульсов, N - коэффициент деления делителя 1 частоты. Как видно из диаграммы (фиг. 3), величина фазового рассогласования импульсов А и Б в установившемся режиме равна длительности импульсов одновибратора. При увеличении, по каким-либо причинам, величины фазового рассогласования импульсов А и Б увеличивается длительность импульсов 10 на прямом входе интегратора 15, а уменьшение рассогласования приводит к исчезновению импульсов 10 и появлению импульсов 12 (П участок временной диаграммы фиг. 3) на инверсном входе интегратора. Следовательно, выходное напряжение интегратора и частота управляемого генератора 16 изменяются в необходимую сторону до тех пор, пока величина фазового рассогласования не станет равной длительности импульсов одновибратора 14., При резком изменении входной частоты изменяется знак фазового рассогласования, и на инверсный вход интегратора 15 подается широтно-импульсный сигнал с выхода элемента 8 И, изменяя в необходимую сторону напряжение интегратора и частоту управляемого генератора. Благодаря этому, в схеме умножителя исключается режим биений и устраняется опрокидывание регулирования. Исключение цепи тактования из схемы известного устройства для умножения частот и введение одновибратора и дополнительных логических элементов И поз воляет в установившемся режиме работы умножителя значительно уменьшить длительность импульсов, поступающих на интегратор 15, что обеспечивает уменьшение пульсации выходаого напряжения интегратора и увеличение равномерности выходной частоты умножителя (точность умножения). При этом (в противоположность известному), на вход триггера 4 поступают две последовательности импульсов с фазовым сдвигом, по времени равным длительности импульсов одновибратора, что значительно больше величины €. Это обеспечивает нормальную работу умножителя, а именно исключает одновременный приход импульсов на вход триггера 4 при значительных внешних возмущениях, вызывающих фазовый сдвиг поступающих после довательностей импульсов. Из временных диаграмм на фиг. 3 видно, что длительность входных импульсов интегратора 15 не зависит от времени Г, а определяется в установившемся режиме только величиной утечки напряжения на интеграторе. Ввиду того, что в предпагаемом умножителе утечка напряжения интегратора не должна обеспечивать расход (списывание) напряжения интегратора, накопленного за время Т, как это делается в известном, то, конструктивно, интегратор может выполняться с величиной утечки напряжения на порядок меньшей, чем в противопоставляемом устройстве, что улучшает точность умножения. Исключение цепи тактования устраняет также зону нечувствительности в замкнутом контуре регулирования схемы умножителя. Благодаря этому, понижение входной частоты умножителя не приводит к искажению фазового . положения импульса входного сигнала и увеличению неравномерности выходной частоты. Устойчивость умножителя в этом случае увели«швается. Таким образом, исключение из схемы умножителя цепи тактования и введение новых элементов - одновибратора, инверторов и дополнительных элементо в И позволяет повысить точность и расширить диапазон коэффициентов умножения умножителя. Сравнительные испытания данного устройства с известным устройством показали, что введение йовых элементов Дает возможность обеспечить мгновенную точность умножения частоты не хуже 0,01% в даапазоне изменения коэффициентов умножения от 20 до 1000. Формула изобретения Умножитель частоты, содержащий управляемый генератор, делитель частоты, выход которого соединен с первым входом первого элемента И и, через элемент задержки, с первым входом первого триггера, первый выход котороге подключен ко второму входу первого и первому входу второго элементов И, второй выход первого триггера подключен к первым входам третьего и четвертого элементов И, второй вход первого триггера через второй элемент задержки соедашен со входом устройства и вторым входом третьего элемента И, выходы первого и третьего элементов И подключены, соответственно, к первому и второму рходйм второго триггера, выходы которого подключеиы, соответственно, ко вторым входам второго и четвертого элементов И, выход которого подключен к первому входу интегратора, выход которого подключен ко входу управляемого генератора, выход которого соединен с выходом Умножителя и входом делителя частоты, о т л и ч а ю щи и с я тем, что, с целью повышения точности и расширения диапазона умноженин умножителя, он содержит первый н второй элементы НЕ, пятый и шестой элементы И рдновибратор, вход которого подключен ко входу умножителя, выход - к первому входу пятого элемента И и, через первый элемент НЕ, к первому входу шестого элемента И, выход которого подключен к первому входу интегратора, второй вход которого подключен к выходу пятого элемента И, второй вход которого подключен к выходу второго элемента И и входу второго элемента НЕ, выход которого подключен-КО второму входу шестого элемента И,

Ф«-г. /

Й7и.г. 2

ши,э. 5 445698 Источники информации, принятые во внимание при экспертнзе 1.Авторское свидетельство СССР №404085, кл. G 08 F 7/39, 1973. 2.Авторское свидетельство СССР по заявке N«2183038, кл. G 06 F 7/39, 20Л0.75.

Авторы

Даты

1980-06-30—Публикация

1977-03-16—Подача