(54) ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗСЖЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод постоянного тока | 1981 |

|

SU995247A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Цифровой частотный дискриминатор | 1979 |

|

SU849419A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| Цифровой частотный дискриминатор | 1980 |

|

SU907793A1 |

| Частотно-фазовый дискриминатор | 1977 |

|

SU699666A1 |

| Частотно-фазовый дискриминатор | 1984 |

|

SU1182625A1 |

| Цифровой фазовый детектор | 1979 |

|

SU886234A1 |

| Устройство для допускового контроля частоты | 1987 |

|

SU1499465A1 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

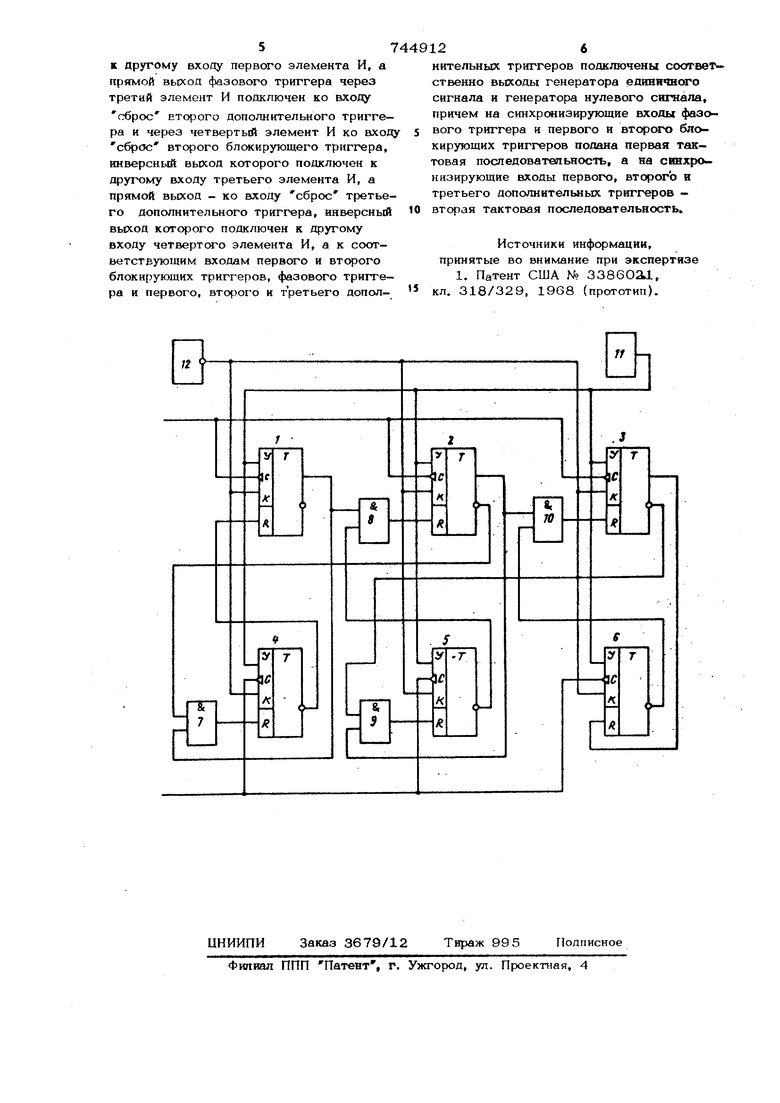

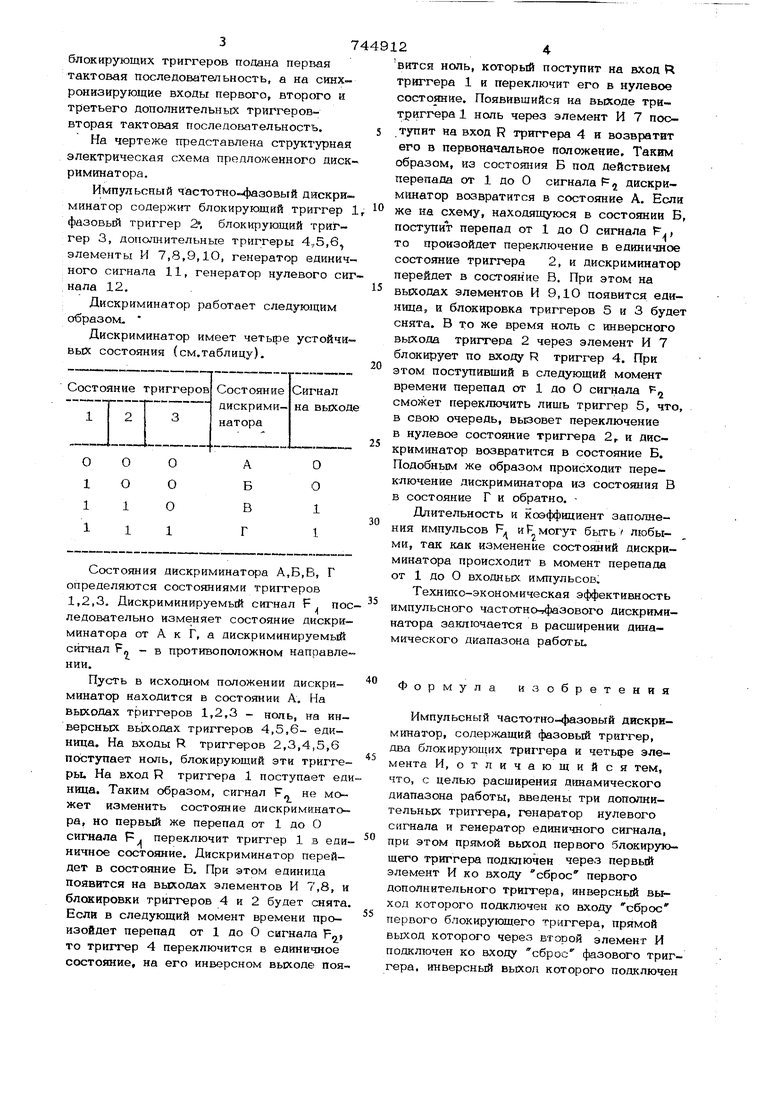

Изобретение относится к импульсной тезшике, в частности, к устройствам фазовой автопоястройки частоты. Известен импульсный частотно-фазовый дискриминатор, содержащий фазовый триггер, два блокирующих триггера и четыре элемента И l Однако известный импульсный частотно-фазовый дискриминатор не обладает необходимой шврин динамического диапазона работы.. Цель изобретения - расширение динамического диапазона работы. Для этого в импульсный частотно фазовый дискриминатор, содержащий фазовы триггер, два блокируюших триггера и четыре элемента И, введены три дополните ных триггера, генератор нулевого сигнал в генерат(ф единичного сигнала, при этом орямой выход первого блокирующего триг гера подключен шрез первый элемент И ко входу сброс первого дополнительного триггера, инверсный выход которого подключен ко входу сброс первого блокнрующего триггера, прямой выход которого через второй элемент И подключен .ко входу сброс фазового триггера, инверсный выход которого подключен к другому входу первого элемента И, а прямой выход фазового триггера через третий элемент И подключен ко входу сброс второго дополнительного триггера и через четвертый элемент И йо вхо.ду сброс второго блокирующего триггера, инверсный выход которого подключен к другому входу третьего элемента И, а прямой выход - ко входу сброс третьего дополнительного триггера, инверсный выход которого подключен к другому входу четвертого элемента И, а к соот ветствуюшкм входам первого и второго блсжирующих триггеров, фазового триггера и первого, второго и третьего дополнительных триггеров подключены соответственно выходы генератора единичного сигнала и генератс нулевого сигнала, причем на синхронизирующие входы фазового триггера и первого и второго блокирующих триггеров подана пергшя тактовая последовательность, а на синхронизирующие входы первого, второго и третьего дополнительных триггероввторая тактовая последовательность, На чертеже представлена структурная электрическая схема предложенного дискриминатора. Импульсный частотно-фааовый дискрй- минатор содержит блокирующий триггер 1 фазовый триггер 2, блокирующий триггер 3, дополнительные триггеры 4,,5,6, элементы И 7,8,9,1О, генератор единичного сигнала 11, генератор нулевого сиг нала 12. Дискриминатор работает следующим образом. Дискриминатор имеет четыре устойчивых состояния (см,таблицу). Состояния дискриминатора А,Б,В, Г определяются состояниями триггеров 1,2,3, Дискриминируемый сигнал F пос ледовательно изменяет состояние дискриминатора от А к Г, а дискриминируемый сигнал Fn - в противоположном направле нии. Пусть в исходном положении дискриминатор находится в состоянии А. На выходах триггеров 1,2,3 - ноль, на инверсных вь1ходах триггеров 4,5,6- единица. На входы R триггеров 2,3,4,5,6 псютупает ноль, блокирующий эти триггеры. На вход R триггера 1 поступает ед ница. Таким образом, сигнал F- не может изменить состо$шне дискриминатора, но первый же перепад от 1 до О сигнала F , переключит триггер 1 в еди ничное состо$шие. Дискриминатор перейдет в состояние Б. При этом единица появится на выходах элементов И 7,8, и блокировки триггеров 4 и 2 будет снята Если в следующий момент времени произойдет перепад от 1 до О сигнала F, то триггер 4 переключится в единичное состояние, на его инверсном выходе поя внтся ноль, который поступит на вход R триггера 1 и переключит его в нулевое состояние. Появившийся на выходе тритриггера 1 ноль через элемент И 7 поотупит на вход R триггера 4 и возвратит его в первоначальное положение. Таким образом, из состояния Б под действием перепада от 1 до О сигнала Pj дискриминатор возвратится в состояние А, Если же на схему, находящуюся в состоянии Б, поступит перепад от 1 до О сигнала F,, то произойдет переключение в единичное состояние триггера 2, и дискриминатор перейдет в состояние В, При этом на выходах элементов И 9,1О появится единица, и блокировка триггеров 5 и 3 будет снята. В то же время ноль с инверсного выхода триггера 2 через элемент И 7 блокирует по входу R триггер 4. При этом поступивший в следующий момент времени перепад от 1 до О сигнала P,j сможет переключить лишь триггер 5, что, в свою очередь, вызовет переключение в нулевое состояние триггера 2 и дискриминатор возвратится в состояние Б. Подобным же образом происходит переключение дискриминатора из состояния В в состояние Г и обратно. Длительность и коэффициент заполнения импульсов F. и F могут быть v любыми, так как изменение состояний дискриминатора происходит в момент перепада от 1 до О входньЕХ импульсов. Техншсо-экономическая эффективность импульсного частотночфазового дискриминатора заключается в расширении динамического диапазона работы. Формула изобретения Импульсный частотно-фазовый дискриминатор, содержащий фазовый триггер, два блокирующих триггера и четыре элемента И, отличающийся тем, что, с целью расширения динамического диапазона работы, введены три дополнительных триггера, генаратор нулевого сигнала и генератор единичного сигнала, при этом прямой выход первого блокирующего триггера подключен через первый элемент И ко входу сброс первого дополнительного триггера, инверсный выход которого подключен ко входу сброс первого блокирующего триггера, прямой выход которого через второй элемент И подключен ко входу сброс фазового триггера, инверсный выход которого подключен

к другому входу первого элемента И, а прямой выход фазового триггера через третий элемент И подключен ко входу

сброс Еторого дополнительного триггера к через четвертый элемент И ко входу сброс второго блокирующего триггера, инверсный выход которого подключен к другому входу третьего элемента И, а прямой вьсход - ко входу сброс третьего дополнительного триггера, инверсный выход которого подключен к другому входу четвертся о элемента И, а к соответствующим входам первого и второго блокирующих триггеров, фазового триггера и первого, второго и третьего допол-

нительных триггеров подключены соответственно выходы генератора единичного сигнала и генератора нулевого сигнала, причем на синхронизирующие входы фазового триггера н первого и вторсвч блокирующих триггеров подана первая тактовая последовательность, а на синхро низирующие входы первого, второго и третьего дополнительных триггеров вторая тактовая последовательность.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-06-30—Публикация

1978-03-22—Подача