1

.Изобретение относится к технике связи и может использоваться при построег НИИ систем передачи данных (СПД).

Известно устройство для приема дискретной информации в системах с решающей обратной связью, содержащее последовательно соединенные входной согласующий блок и декодер, выходы которого подключены ко входам решающего блока и накопителя, к дополнительному ъкору которого подключен Ьыход блока управления, входы которого соединены со входами передатчика обратного каналаЩ.

Однако данное устройство имеет н:евысокую скорость приема.

Цель изобретения - повышение быстродействия устройства.

Для этого в устройство для приема дискретной ин(}юрмации в системах с решающей обратной связью, содержащее последовательно соединенные входной согласующий блок и декодер, выходы которого подключены ко входам решающего блока и накопителя, к дополнительному

входу которого подключен выход блока управления, входы которого соединены с входами передатчика обратного канала, введен блок поиска ошибки, входы которого соединены с выходами решающего блока, накопителя и дополнительным выходом декодера, а выходы блока поиска ошибки подключены ко входам блока управления, блок поиска ошибки содержит два элемента ИЛИ, три элемента И, ре10гистр, блок сравнения, ключ и триггер, выходы которого подключены к первым входам первого и второго элементов И, выходы которых соединены соответственно с первыми входами блока сравнения

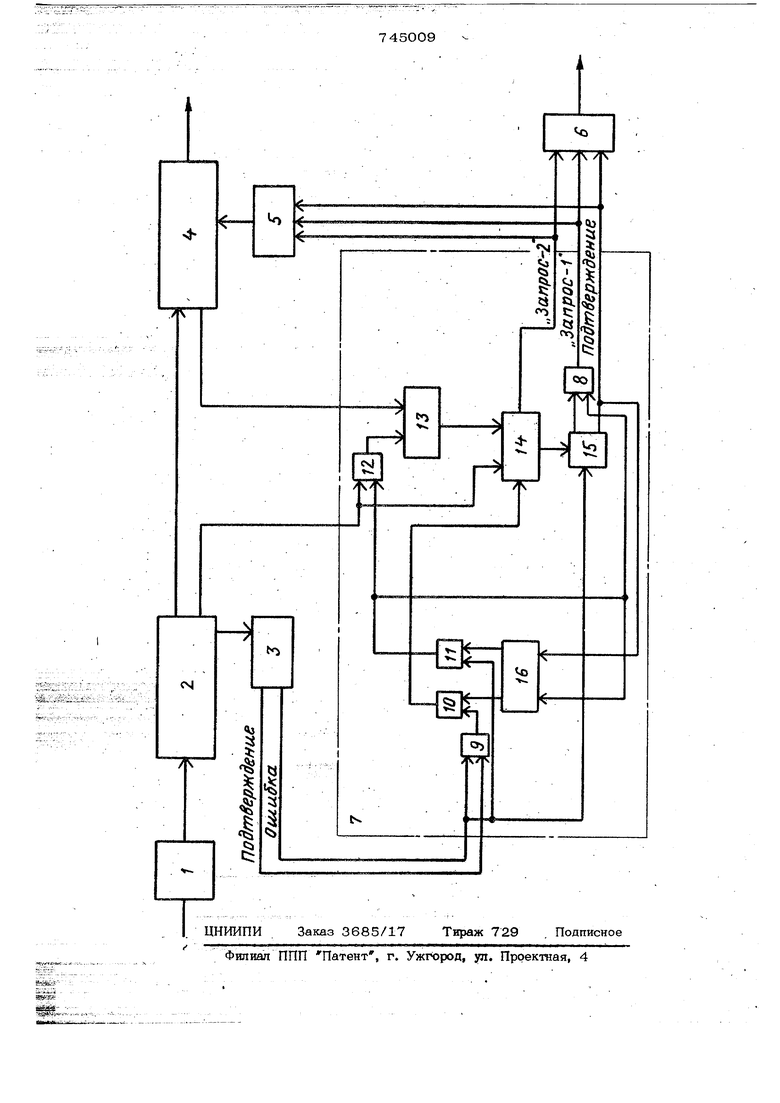

5 и третьего элемента И, второй вход которого соединен со вторым входом блока сравнения, к третьему входу которого подключен выход регистра, первый вход которого соединен с выходом тре20тьего элемента И, при этом выход блока сравнения подключен в первому входу ключа, выходы которого соединены соот ветственно с первыми входами первого элемеЕ1та ИЛИ и триггера, ко второму входу которого подключен выход второго элемента И, второй вход которого соединен со вторым входом ключа и пе|эвым входом второго элемента ИЛИ, выход которого подключен ко второму входу первого элемента И, а выход второго элемента И соединен со вторым вх дом первого элемента ИЛИ, причем вых ды блока сравнения и первого элемента ИЛИ являются выходами блока поиска ошибки, входами которого являются вход второго элемента ИЛИ, второй вход третьего элемента И и второй вход регистра. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство для приема дискретной информации в системах с решающей обра ной связью содержит входной согласующий блок 1, декодер 2, решающий блок .3, накопитель 4, блок управления 5, передатчик 6 обратногоканала, ёлок поиска ошибки 7, который состоит из элементов ИЛИ 8, 9, элементов И 10, 11, 12, регистра 13, блока сравнения 14, ключа 15 и триггера 16. Устройство работает следующим образом. . Принятые кодовые поступают из канала через входной согласующий блок 1 в декодер 2, откуда информацио ные символы записываются в накопител а проверочные - в решающий блок 3, В накопителе 4 хранятся X ранее приня тых блоков, очередной принятый кодовый блок через X тактов выдается потребите При первом обнаружении решающим блоком 3 ошибки в принимаемом блоке сигнал ошибка поступает на первый вход элемента И 11, на второй вход ко торого подается отпирающее нaпpяikeниe со второго выхода триггера 16. При этом с выхода элемента И 11 снимаетс сигнал, ошибка, подаваемый через вто рой вход элемента ИЛИ 8 на вход Запрос-1 блока управления 5 и пе редатчика 6, который посылает на передающую станцию сигнал Запрос-. Сигнал с выхода элемента И 11 подает ся акже на первый вход элемента И 1 ко второму входу которого подключен .выход декодера 2 и.на первый вход три гера 16, изменяя его состояние. В это случае информационная комбинация принятого кодового блока записывается в регистр 13. При получении сигнала Запрос- передающая сторона производит повторение / -го блока. При повторном обнаружении ошибки при декодировании / -го блока сигнал ошибка из решаюшего блока 3 через элемент ИЛИ 9, элемент И 10, на второй вход которого подается отпирающее напряжение с первого входа изменившего свое состояние триггера 16, подается на управляющий вход блока сравнения 14. В этом случае в блоке сравнения 14 производится сравнение информационных комбинаций повторенного с-го блока и записанного в регистр 13 При совпадении сравниваемых информацинных комбинаций, что свидетельствует о том, что ошибка проникла в глубь накопителя 4, с первого выхода блока сравнения 14 подается сигнал на вход Запрос-2 блока управления 5 и передатчика 6, который формирует сигнал Запрос-2.и посылает его на передающую сторону. В режиме поиска ошибки передающая сторона повторяет (/ -1)-й блок. Блок управления 5 заносит в регистр 13 (/ -1)-й блок из накопителя 4 для обеспечения возможности сравнения повторенного и первоначально принятого его значений. Если при вращении информацио1шые комбинации повторенного i -го блока и . t -го блока из накопителя; 4 не совпали, то :на ключ 15 подается сигнал со второго выхода блока сравнения 14 одновременно с сигналом ошибка, поступившим на второй вход ключа 15. В результате , этого с первого выхода ключа 15 через элемент ИЛИ 8 на вход Запрос-1 передатчика 6 поступит сигнал, по которому будет сформирован и передан на передающую сторону сигнйл Запрос-1. Повторение t -го блока будет осуществляться до тех пор, пока он не будет принят без ошибки, что свидетельствует о том, что обнаружение ошибки в блоке вызвано искажением в канале i -го блока, или инфо1 мационные комбинации повторенного / -го блока и записанного в регистр 13 совпадут, в результате чего передатчик 6 сформирует сигнал Запрос-2, при получении которого передающая сторона передаст ( / -1)-и блок. Предположим, что размножение ошибки вызвал (i -у)-и блок, находящийся в накопителе 4. Тогда повторенный а -1.)-й блок будет декодирован с необнаруженной ошибкой, так как условия приема, корреляционные связи ( i-l)-ro блока с пpeдыдyщиv и блоками не изменились, В этом случае с решающ го блока 3 по шине подтверждение через элементы ИЛИ 9 и И 10 на управляющий вход блока сравнения 14 пос тупит сигнал. Блок сравнения произведе сравнение декодированного ( / -1)-го блока, записанного в регистр 13, При совпадении сравниваемых блоков с первого выхода блока сравнения 14 на вход Запрос-2 передатчика 6 и блока управления 5 поступит сигнал, по котором передатчик 6 посылает на передающую сторону Запрос-2, а блок управления 5 заносит в регистр 13 (i -2)-й блок из накопителя 4 и т,д, Поиск необнаруженной ошибки прекращается, если при безошибочном приеме повторяемого (i -/)-го блока информа-г ционная комбинация декодированного блока и записанного в регистр 13 не совпадут. В этом случае после декодиро вания (L -у)-го блока сигнал подтверждение из решающего блока 3 через элементы ИЛИ 9, И 10 поступит на управляющий вход блока сравнения 14. Так как информационные комбинации сравниваемых (/ -(/ ) блоков, находящихся в декодере 2 и регистре 13 отличаются, то со второго выхода блока сравнения 14 на ключ 15 поступит сигнал. Поскольку на BTqpofl вход ключа 15 сиг нала ошибка не выдается, то со второ го выхода ключа 15 на вход подтверждение передатчика 6 блока управления 5и на второй вход триггера 16 поступит сигнал, по передатчик 6на передающую сторону передает сигнал подтверждение блок управления 5 стирает находящийся в регистре 13 блок и записывает в накопитель 4 блок из декодера, 2, опрокидывается триггер 16 блока поиска 7, прекращая поиск необнаруженной ошибки. В предложенном устройстве повышает ся быстродействие. Формула изобретения 1. Устройство для приема дискретной информации в системах с pemasoщей обратной связью, содержащее после довательно соединенные входной согласу щий блок и декодер, выходы которого подключены ко входам решающего блокаи . и накопителя, к дополнительному входу подключен выход блока управления, входы которого соединены со входами передатчика обратного канала, о т л и ч а ю щ е е с-я тем, что, с целью повьпиения быстродействия устройства, введен блок поиска ошибки, входы которого соединены с выходами решающего блока, накопителя и дополнительным выходом декодера, а выходы блока поиска ошибки подключены ко входам блока управления. 2. Устройство по п. 1, отличающееся тем, что блок поиска ошибки содержит два элемента ИЛИ, три элемента И, регистр, блок сравнения, ключ и триггер, выходы которого подключены к первым входам первого и второго элементов И, выходы которых соединены соответственно с первбГми входами блока сравнения и третьего элемента И, второй вход которого соединен со вторым входом блока сравнения, к третьему входу которого подключен выход регистра, вход которого соединен с выходом третьего элемента И, при этом выход блока сравнения подключен тс первому входу ключа, выходы которого соединены соответственно с первыми входами первого элемента ИЛИ н триггера, ко второму входу которого подключен выход второго элемента И второй вход -котсфого соединен со вторым входом ключа и первым входом второго элемента ИЛИ, выход которого подключен ко второму входу первого элемента И, а выход второго элемента И соединен со вторым входом первого элемента ИЛИ, причем выходы блока сравнения и первого элемента ИЛИ являются выходами блока поиска ошибки, входами которого являются входы второго элемента ИЛИ, второй вход третьего элемента И и второй вход регистра. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N9 478447, кл. Н О4 - 1/10, 1972 (прототип/..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1977 |

|

SU748895A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство защиты от ошибок | 1984 |

|

SU1197115A1 |

| Устройство для контроля канала передачи данных | 1981 |

|

SU1035811A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501296A1 |

| Система передачи данных по каналам с обратной связью | 1980 |

|

SU966923A1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1984 |

|

SU1197114A1 |

Авторы

Даты

1980-06-30—Публикация

1976-08-26—Подача