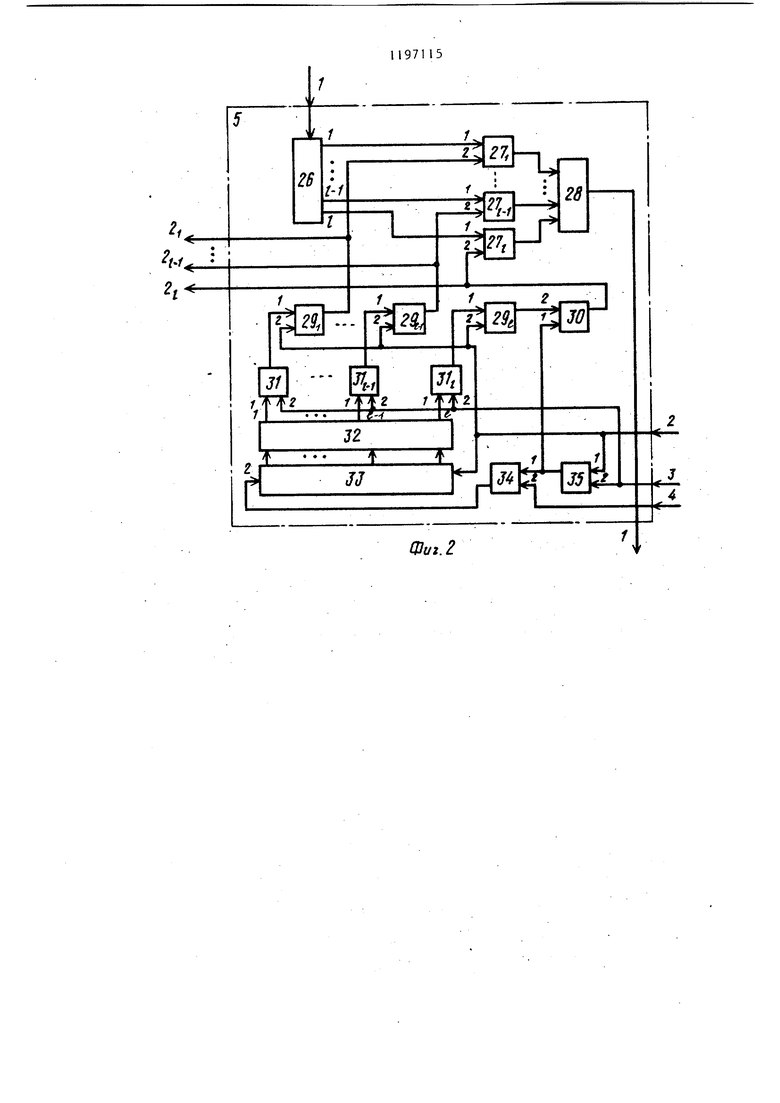

2. Устройство по п. 1, отличающееся тем, что буферный накопитель содержит регистр, выходы которого подключены к первым входам первых 2 элементов И,, выходы которых подключены к входу первого элемента ИЛИ, выход которого является первым выходом буферного накопителя, а также последовательно соединенные счетчик, дешифратор, вторые элементов И и триггеров, вторые входы которых объединены с первыми входами счетчика и (i+l)-ro триггера и являются вторьм входом буферного накопителя, третьим входом которого являются объединенные вторые входы вторых элементов И и (1+1)-го триггера, выход которого подключен к первым входам второго элемента ИЛИ и )-го элемента И, выход которого подключен к второму вхрду счетчика, а выход -го триггера подключе к второму входу второго элемента ИЛИ, выход которого, а также выходы t-l триггеров подключены к вторым входам первых элементов И- и являются 2 f выходами буферного накопителя, первым и четвертым входами которого являются соответственно вход регистра и второй вход ( )-го элемента И.

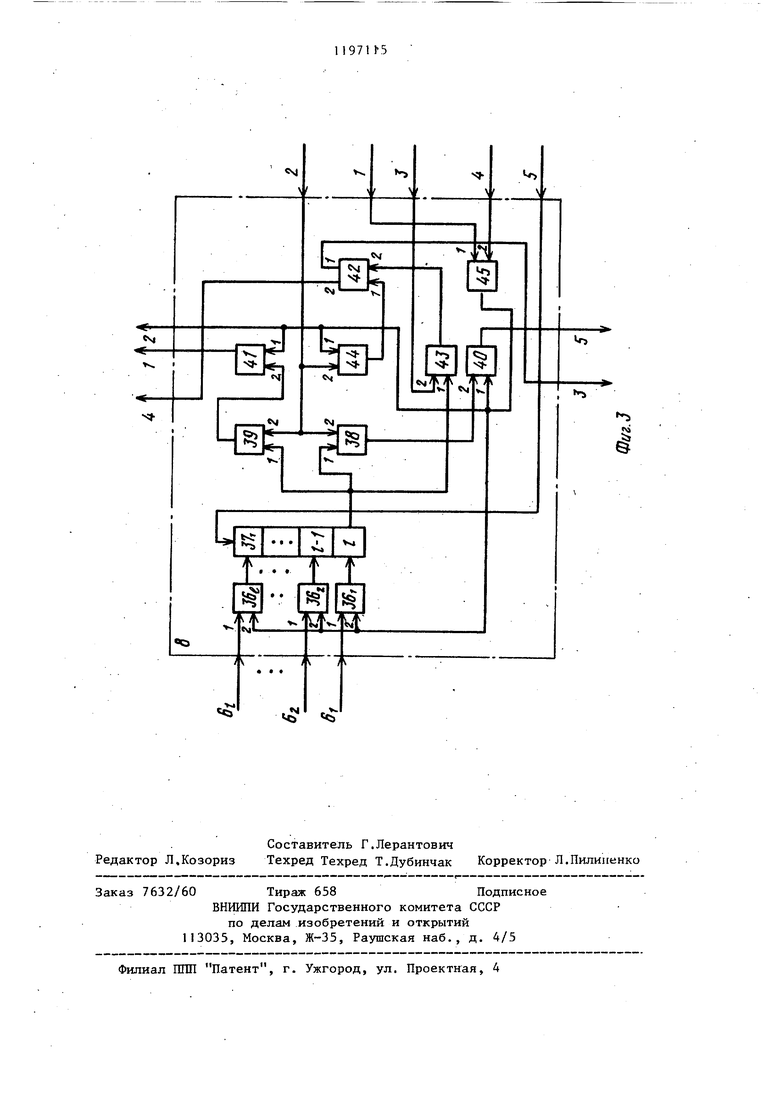

3. Устройство по п. 1, отличающееся тем, что блок управ5

1

ления содержит элементов И,первые входы которых являются 6 входами блока управления, а выходы Е элементов И подключены к входам линии задержки, выход которой подключен к первым входам первого, второго и третьего элементов ИЛИ, при этом к вторым входам В элементов И, а также к первым входам первого и второго триггеров и четвертого элементов ИЛИ подключен выход пятого элемента ИЛИ, а к вторым входам первого и второго триггеров подключены выходы соответственно первого и второго элементов ИЛИ, вторые входы которых объединены с вторым входом четвертого элемента ИЛИ и являются вторым входом блока управления, первым, третьим, четвертым и пятым входами которого являются соответственно первый вход пятого элемента ИЖ, второй вход третьего элемента ИЛИ, второй вход пятого элемента ИЛИ и вход линии задержки, а выходы четвертого и третьего элементов ИЛИ подключены соответственно к первому и второму входам третьего триггера, первый и второй выходы которого являются соответственно третьим и четвертым выходами блока управления, первым, вторым и пятым выходами которого являются соответственно выходы второго триггера,пятого элемента ШШ и первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| Устройство для передачи и приема информации | 1982 |

|

SU1048580A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1693732A1 |

| Устройство для выделения команд в телеграфной стартстопно-синхронной системе | 1991 |

|

SU1764178A2 |

| Устройство передачи и приема дискретной информации | 1989 |

|

SU1646066A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство защиты от ошибок | 1983 |

|

SU1272514A1 |

| Устройство для регистрации и передачи информации | 1976 |

|

SU658592A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

1, УСТРОЙСТВО ЗАЩТЫ ОТ ОШИБОК, содержащее на передаче входной накопитель, задающий генератор, кодер и последовательно соединенные буферный накопитель и ключ, а на приеме - блокиратор, выход которого подключен к входам декодирующего блока и дешифратора запросной комбинации, выход которого подключен к первому входу блока управления, первый, второй итретий выходы которого подключены соответственно к управляющему входу ключа, входу датчика запросной комбинации и управляющему входу приемного Накопителя, а выход датчика запросной комбинации объединен с выходом кодера и является первым выходом устройства, вторым и дополнительным выходами ко торого являются соответственно выход приемного накопителя и четвер- тый выход блока управления, а первым и вторым входами устройства являются соответственно входы входного накопителя и блокиратора, о тличающееся тем, что, с целью повьшения помехозащищенности дискретной информации, в него введены на передаче датчик служебной команды и последовательно соеди-. ненные блок элементов ИЛИ и анали- затор служебных команд, первьй вы- ход которого подключен к входу кодера, при этом к первому, второму, третьему и.четвертому входам блока элементов ИЛИ подключены соответственно выходы входного накопителя, ключа и датчика служебных команд, первый вход которого объединен с вторым входом блока управления и является дополнительным входом уст-ройства, причем вторые входы блока элементов ИЛИ и анализатора служеб(Л ной команды подклюнены соответственно к первому и второму входам буферного накопителя, а на приеме анализатор служебных команд, к входу которого подключен первый выход декодирующего блока, при этом к входу приемного накопителя подключен ю первый выход анализатора служебной команды, второй выход которого sj подключен к третьим входам буферного накопителя и блока управления, 01 к четвертому входу которого подключен второй выход декодирующего блока, а третий выход анализатора служебной команды подключен к второму входу датчика служебных команд, причем выход задающего генератора подключен к четвертому входу буферного, накопителя и пятому входу блока управления, пятый выход которого подключен к управляющему входу блоки- ратора, а 21 (где 1,2,... ,1)выходов буферного накопителя подключены к 6t входам-блока управления.

1

Изобретение относится к технике связи и может использова:ться в аппаратуре передачи дискретной информации с решающей обратной связью.

Цель изобретения - повышение помехозащищенности дискретной информации.

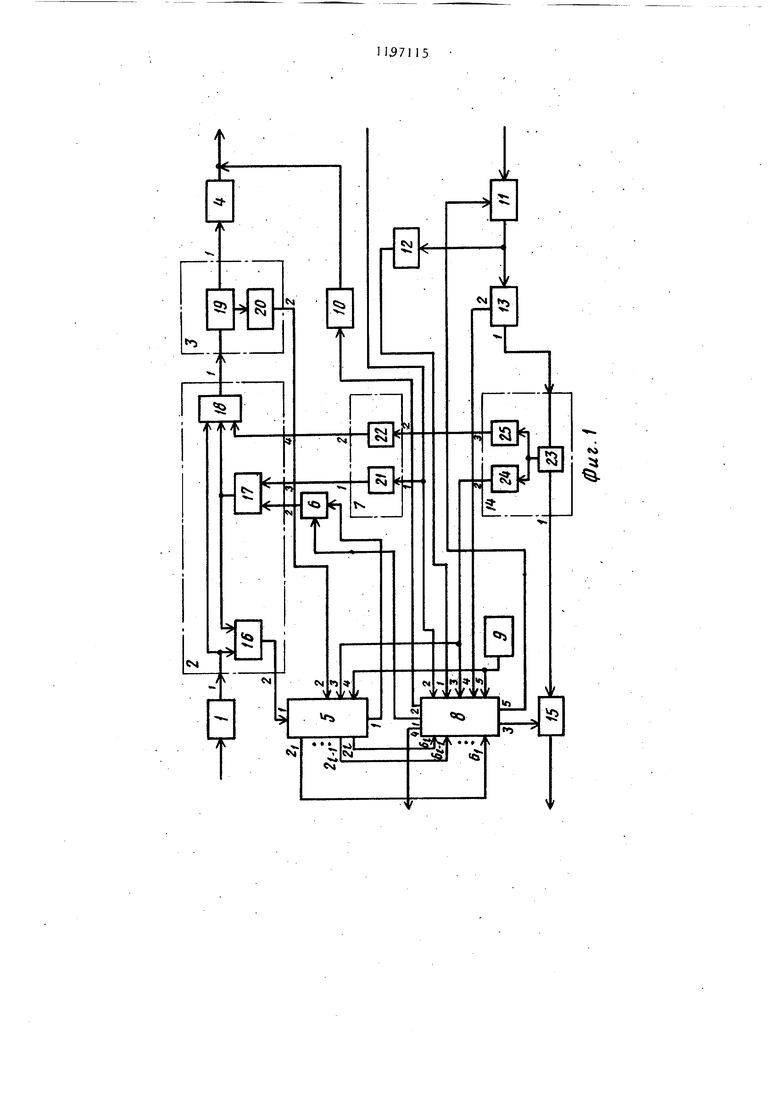

На фиг. 1 представлены структурные электрические схемы устройства защиты от ошибок, буферного накопителя и блока управления соответственно.

Устройство для защиты от ошибок содержит входной накопитель 1, блок 2 элементов ИЛИ, анализатор 3 служеб ной команды, кодер 4, буферный накопитель 5, ключ 6, датчик 7 служебных команд, блок 8 управления, вьщающий генератор 9, датчик 10 запросной комбинации, блокиратор 11, дешифратор 12 запросной комбинации, декодирующий блок 13, анализатор 14 служебной команды, приемный накопитель 15. Блок 2 элементов ШШ содержит элементы ИЛИ 16-18, анализатор 3 служебной команды содержит регистр 19, дешифратор 20, датчик 7 служебных команд содержит датчики 21 и 22, анализатор 14 служебной команды содержит регистр 23, дешифраторы 24 и 25,-буферньм накопитель 5 содерзкит регистр 26, первые элементы И , первый элемент ШШ 28, триггеры , второй элемент

3

ИЛИ 30, вторые элементы И ЗЦ -З , дешифратор 32, счетчик 33, элемент И 34, триггер 35, блок 8 управления содержит элементы И 36,-Збр, линию 37 задержки, первый 38 и второй 39 элементы ИЛИ, первый 40, второй 41 и третий 42 триггеры, третий 43 четэертый 44 и пятый 45 элементы ИЛИ

Устройство защиты от ошибок работает следующим образом.

По окончании процесса фазирования от аппаратуры с рещающей обратной связью (РОС ) поступает сигнал об окончании фазирования на второй вход блока 8 управления и первый вход датчика 7 служебных команд.По этому сигналу через элементы ИЛИ 38, 39 и 44 срабатывают соответственно триггеры 40-42 блока 8 управления. При этом управляющий сигнал с первого выхода третьего триггера 42 через третий выход блока 8 управления поступает на управляющий вход приемного накопителя 15 и стирает в нем информацию. Сигнал с второго выхода третьего триггера 42 через четвертый выход блока 8 управления запрещает ввод информации во входной накопитель 1. Управляющий сигнал с выхода второго триггера 41 через пер вый выход блока 8 управления закрьюает ключ 6, а управляющий сигнал с выхода первого триггера 40 через пятьш выход блока 8 управления открьшает блокиратор 11 .Сигналом обокон чании фазирования на инициирующей станции запускается датчик 21 датчика 7 служебных команд, который вырабатывает команду, условно назьшаемую далее СК-1, представляющую собой последовательность из К элементов,не используемую при передаче oneративной информации от источника информации. Команда СК-1 через элементы ИЛИ 17 и 16 блока 2 элементов ИЛИ поступает на первый вход буферного накопителя 5 и записывается в его регистр 26, а через элементы ИЛИ 17 18 блока 2 элементов ИЛИ, анализатор 3 служебной команды, кодер 4, где она перекодируется в помехозащищенный код,.поступает на выход устройства. При прохождении команды СКчерез анализатор 3 служебной команды наего втором выходе появляется сигнал, который поступает на второй вход буферного накопителя 5. По этому сиг налу срабатывает триггер 35 буферног

1154

накопителя 5, а счетчик 33 и тригге 29, 29j устанавливаются в исходное нулевое состояние. Управляющий сигн с выхода триггера 35 поступает на первьй вход элемента И 34, а через второй элемент ИЛИ 30 - на второй вход элемента И 27j и на выход 2р буферного накопителя 5, далее на вход 6р, первый вход элементаИ 36g блока 8 управления. При этом разрешется прохождение импульсов цикловой частоты через четвертый вход буфернго накопителя 5 от задающего генератора 9 на второй вход счетчика 28, выход Р регистра 26 соответствующи максимальной емкости буферного накопителя 5, подключается через элемент И 27 , первый элемент ИЛИ 23, через первый выход буферного накопителя 5 к выходу ключа 6. Команда СК-1, поступающая из канала связи на вход устройства противоположной станции, через блокиратор 11 записьтается в Декодирующий блок 13, где она декодируется, а затем переписьшается-в р егистр 23 анализатора 14 служебной команды, в результате на выходе дешифратора 25 появляется сигнал, который подается на третий выход датчика 7 служебных команд. Под действием этого сигнала запускается датчик 22, который вырабатьшает.вторую команду, условно называемую далее СК-2, представляющую собой последовательность из К элементов, т.акже не используемую при передаче оперативной информации от источника информации и отличную от служебной команды СК-1. Команда СК-1 переписьшаетея из регистра 23 в приемный накопитель 15, в котором она стирается сигналом, поступающим с третьего выхода блока 8 управления . Команда СЖ-2 через элемент ИЛИ 18, анализатор 3 служебной команды, кодер 4, где она перекодируется в помехозащищенный код, поступает На выход устройства в канал связи. На инициирующей станции принятая команда СК-2 через открытый блокиратор 11 записьшается в декоДИРУЮ1ЦИЙ блок 13, где она декодируется, а затем переписывается в регистр 23 анализатор 14 сл жебной команды, в результате на выходе дешифратора 24 появляется сигнал, который подается на третьи входы буферного накбпителя 5 и блока 8 управления. Команда СК-2 переписьшается из регистра 23 в приемньй накопитель 15, в котором она стирается сигналом, поступающим с третьего выхода блока 8 управления. Под действием сигнала, поступившего на тре тий вход буферного накопителя 5,сра батывают триггер 35 и один из триггеров 29 через соответствую щий элемент И ЗЦ-31 в зависимости от сигнала на соответствующем выходе дешифратора 32,определяемого коли чеством импульсов цикловой частоты, подсчитанных счетчиков 33:с момента передачи команды СК-1 на противоположную станцию .до момента приема от нее команды СК-2. После срабатывания триггера 35 снимается разреша ющий сигнал с первого входа элемента И 34, запрещая прохождение на второй вход счетчика 33 импульсов цикловой частоты от задающего генератора 9, и снимается разрешающий сигнал с второго входа элемента И 2 через первьй вход второго элемента ИЛИ 30. Пусть, для определённости, с момента передачи командь СК-1 на противоположную станцию до момента приема от нее команды СК-2 с.четчик ЗЗ насчитал такое количество импульсов цикловой частоты, при котором в.момент поступления сигнала с выхода дешифратора 24 на третий вход буферного накопителя 5 появляется импульс на (1-1) вькоде дешифратора 32. В- результате на выходе элемента И 31. появляется импульс, под действием которого срабатьшает триггер 29р-. Управляющий импульс с выхода триггера 29.) поступает на второй вход элемента И 27., тем. самым создается возможность для съе информации с (1-1) выхода регистра 26, т.е. выбирается определенная, емкость буферного накопителя 5, и, следовательно, определяется цикл по вторения дискретной информации. Кро ме того, управляющий импульс с выхода триггера 29f-i через 2. выход буферного накопителя 5 поступает на 6f. вход блока 8 управления и далее на первьй вход элемента И В то же время под действием сигнала с выхода дешифратора 24, поступившего на третий вход блока 8 управлени третий элемент ИЛИ 43, срабатывает триггер 42. В результате с третьего выхода блока 8 управления поступает сигнал, разрешающий считьгоание информации из приемного накопителя 15, а с четвертого выхода поступает сигнал, разрешающий ввод информации от источника во входной накопитель 1. В случае обнаружения ошибки при приеме команды СК-1 на втором выходе декодирующего блока 13 появляется управляющий сигнал, который поступает через четвертьй вход блока 8 управления на второй вход пятого элемента ИЛИ 45. С выхода пятого элемента ИЛИ 45 управляющий сигнал через элемент И 36 записьшается на первый вход .линии 37 задержки, для которой продвигающими сигналами являются импульсы цикловой частоты, поступающие на пятый вход блока управления от задающего генератора 9. Кроме того, под действием управляющего сигнала с выхода пятого элемента ИЛИ 45 срабатыва.ют первьй 40 и второй 4Г триггеры,, запускается (по . второму выходу блока 8 управления) датчик 10 запросной комбинации, который выдает в канал связи запросную комбинацию, а через четвертьй элемент ИЛИ -44 срабатывает третий триггер 42. В результате переключения первого триггера 40 блокируется прием информации из канала связи на Е тактов цикловой частоты, сигналом с первого выхода третьего триггера 42 стирается информация в приемном накопителе 15 и запрещается считывание информации от датчика во входной накопитель 1, а сигналом с .выхода второго триггера 41 разрешается считывание информации из регистра 26 буферного накопителя 5 .через ключ 6, элемент ИЛИ 17 блока 2 элементов ИЛИ, анализатор 3 служебной команды, кодер 4 в канал связи, а также с выхода элемента ИЛИ 17 через элемент ИЛИ I6 на первьй вход буферного накопителя 5. Принятая инициирующей станцией запросная комбинация через блокиратор 11 поступает на дешифратор 12 запросной комбинации, где она вьщеляется.- В результате на выходе дешифратора 12 запросной комбинации появляется сигнал,которьй поступает на первьй вход блока 8 управления и далее через пятый элемент ИЛИ 45, элемент И 36g Записывается на первьй вход линии 37 задержки. Кроме того, под действием уп7равляющего сигнала с выхода пятого элемента РШИ 45 срабатывают первый 40 и .второй 41 триггеры, запускается (по второму выкоду блока 8 управления) датчик 10 запросной комбинации, который вьдает в канал связи запросную комбинацию, а через четвертьй элемент ИЛИ 44 срабатьшает третий триггер 42. В результате переключения первого триггера 40 блокируется прием информации из канала связи на f тактов цикловой частоты, сигналом с выхода третьего триггера 42 стирается информация в приемном накопителе 15 и запрещается считывание информации от источника информации во входной накопитель 1, а сигналом с выхода втброго триггера 41 разрешается перезапись и считывание с регистра 26 буферного накопителя 5 команды CK-I через ключ 6, блок 2 элементов ИЛИ, анализатор 3 служебной комбинации, кодер 4 в канал связи. К моменту приема команды СК-1 противоположной станцией на выходе линии задержки 37 блока 8 управления появляется управляющий сигнал, который через элементы ИЛИ 39, 43 и 38 воздействует соответственно на триггеры 41, 42 и 40. В результате переключения третьего триггера 42 с его первого выхода поступает разрешающий сигнал на управляющий вход приемного накопителя 15, ас второго выхода третьего триггера 42 поступает сигнал, разрешающий считьшание информации от источника информации во входной накопитель 1. Сигнал с выхода второго триггера 41 разрешает перезапись и считывание информации из буферного накопителя 5 через ключ 6, а в результате переключения первого триггера 40 открывается блокиратор 11, разрешая прием информации из канала связи. В случае искажения команды СК-1 в канале

971158

связи ошибка обнаружится декоди- рующим блоком 13 и процесс запроса повторится вновь

При искажении команды СК-2 в канаJ ле связи ошибка обнаруживается на инициирующей станции декодирующим блоком 13 и процесс определения цикла повторения начинается вновь как описано вьш1е с передачи команды

10 СК-1. Процесс определения цикла повторения начинается вновь также с передачи команды СК-1. Процесс определения цикла повторения происходит до тех пор, пока команда СК-2,

15 передаваемая в ответ на полученную команду СК-1, будет принята без искажений . .

После определения цикла повторе2Q ния разрешается передача информации от источника, которая поступает через входной накопитель 1, элемент ИЛИ 18 блока 2 элементов ИЛИ, анализатор 3 служебной комбинации, кодер

5 , в котором она перекодируется в помехозащищенный код, в канал связи. Одновременно через элемент ИЛИ 16 блока 2 элементов ИЛИ передаваемая информация поступает на первый вход буферного накопителя 5, в котором

0 записывается в регистр 26.. Информация, поступающая на вход устройства из канала связи через открытый блокиратор 11, записывается в декодирующий блок I3, где она декодируется, а затем переписьшается через

анализатор 14 служебных команд в приемный накопитель 15 и далее на приемник информации . При искажении информации в канале связи ошибка об0наруживается декодирующим блоком 13 , приемной станции. В результате устройство обеспечивает исправление ошибки путем запроса и повторения принимаемой информации как описано

при искажении команды СК-1.

4a

M A

| Устройство защиты от ошибок аппаратуры с решающей обратной связью | 1975 |

|

SU568179A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Гуров B.C., Емельянов Г.А., Етрухин Н.Н | |||

| Передача дискретной информации и телеграфии, М.: Связь, 1969, с, 452. | |||

Авторы

Даты

1985-12-07—Публикация

1984-07-03—Подача