ного. регистра и регистра, вход которого является вторым выходом, а выход - третьим выходом входного накопителя, второй выход буферного регистра являетря первым выходом, а входвходом входного накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Устройство защиты от ошибок | 1983 |

|

SU1272514A1 |

| Устройство для регистрации и передачи информации | 1976 |

|

SU658592A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для передачи и приема информации | 1985 |

|

SU1338089A1 |

| Устройство для регистрации и передачи информации | 1979 |

|

SU781873A2 |

| Устройство обнаружения вставок и выпадений информации в системах передачи данных с решающей обратной связью | 1971 |

|

SU468381A1 |

| Устройство защиты от ошибок | 1984 |

|

SU1197115A1 |

| Адаптивное устройство для анализаКОдОВыХ КОМбиНАций B СиСТЕМАХ пЕРЕ-дАчи диСКРЕТНыХ СООбщЕНий C РЕшАю-щЕй ОбРАТНОй СВязью | 1979 |

|

SU809613A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СОСТОЯНИЯ И УПРАВЛЕНИЯ КАНАЛАМИ И ТЕХНИЧЕСКИМИ СРЕДСТВАМИ В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1991 |

|

RU2007878C1 |

1. УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ОШИБОК, содержащее на передаче последовательно соединенные входной накопитель, перек.шочатель и кодер, последовательно соединенные счетчик блокировки и блок памчтк, первый выход которого подсоединен к второму входу переключателя, к третьему входу которого подключен второй выход блока памяти, второй вход которого объединен с четвертым входом .. переключателя и подключен к второму выходу счетчика блоккровки, первый выход которого подсоединен к пятому входу переключателя, а также после-довательно соединенные датчик команд и датчик сигнсшоз обмена при этом- второй вход блока памяти обьединен с первым входом входного накопителя и является информационным входом, а к второму входу входного накопителя подключен выход датчика команд, а на приеме - последовательно соединенные счетчик блокировки, выходной накопитель к датчик сигналов обмена, к второму входу которого подключен второй выход счетчика блокировки, третий выход которого подсоединен к первому входу первого элемента НЕТ, последовательно соединенные входной накопитель и дешифратор служебных команд, а также декодер и первый элемент -ИЛИ, выход которого подсоединён к входу Запрос датчика команд и входу счетчика блокировкн, второй выход входного накопителя подсоединен к второму входу выходного накопи-теля / а вход входного накопителя объединен с входом декодера и является входом канала связи, отличающееся тем, что, с целью повышения вероятност обнаружения ошибок путем снижения вставок и выпадений комбинадяи, в него введены на приеме последовательно соединенные блок сравнения, счетчик совпадений и элемент И и последовательно соединенные блок элементов ИЛИ и второй jg элемент НЕТ, выход которого подсоет динен к первому входу элемента ИЛИ и второму входу элемента И, выход которого подсоединен к третьему входу выходного накопителя и перво(му входу - счетчика блокировки на передаче, к второму входу первого элемента ИЛИ подключен выход первого элемента HETj гс второму входу (Которого подключен второй выход бло ка элементов ИЛИ, первый вход которого подключен к выходу счетчика сово падений, второй вход подключен квыхо: ду дешифратора служебных команд, а третий вход блока элементов ИЛИ подключен к вьаходу декодера, первый выход счбтчика блокировки подсоединен к второму входу второго элемента НЕТ, третий выход входного накопителя подсоединен к первому входу блока сравнения, второй вход которого объединен с входом входного накопителя, а на передаче выход датчика сигналов, обмена подсоединен к второму входу счетчика блокировки. 2, Устройство по п. 1, отличающееся тем, что входной накопитель на приеме выполнен в виде последовательно соединенных 5уфер

Изобретение относится к технике связи и может быть использовано для зашиты аппаратуры передачи данных с решающей обратной связью от вставок и выпаданий информации.

Известно устройство обнаружения вставок и выпадений информации в си темах передачи данных, содержащее последовательно соединенные накопитель, дешифратор, первый ключ, блок сравнения и пересчетный блок, други входы которого соединены соответственно с выходом блока обнаружения и входом первого ключа, другой выхЬ которого подключен к первому входу накопителя, второй вход которого подключен к другому входу блока сранения, причем на вход блока обнаружения и другой вход первого ключа подан входной сигнал, последовательно соединенные дополнительный накопитель, элемент Пирса и первый элемент И, а также второй и третий ключи, второй элемент И и элемент ИЛИ, причем выход блока обнаружени подключен к входу дополнительного Накопителя и другому входу элемента Пирса, а выход первого элемента И подключен к второму входу накопителя j третий выход которого через второй ключ подключен к входу элемента ИЛИ, другой вход которого через третий ключ соединен соответсвенно с вторым выходом накопителя и первым выходом пересчетного блока, второй выход которого подключен к другому входу второго ключа и третьему входу накопителя, четвертый вход Которого соединен с первым входом пересчетного блока, третий выход которого подключен через второй элемент И к пятому входу накопи|теля, причем другой вход первого элемента И соединен с другим выходом блока сравнения, а другой вход второго элемента И соединен с выходом дешифратора ill.

Данное устройство обнаружения вставок и выпадений информации в системах передачи данных с высокой точностью обнаруживает вставки и выпсщения на одной из станций, однако на другой станции ложная фиксация выпадений и вставок повышается за счет трансформации комбинации

Запрос в запрещенную по коду при передаче по обратному каналу.

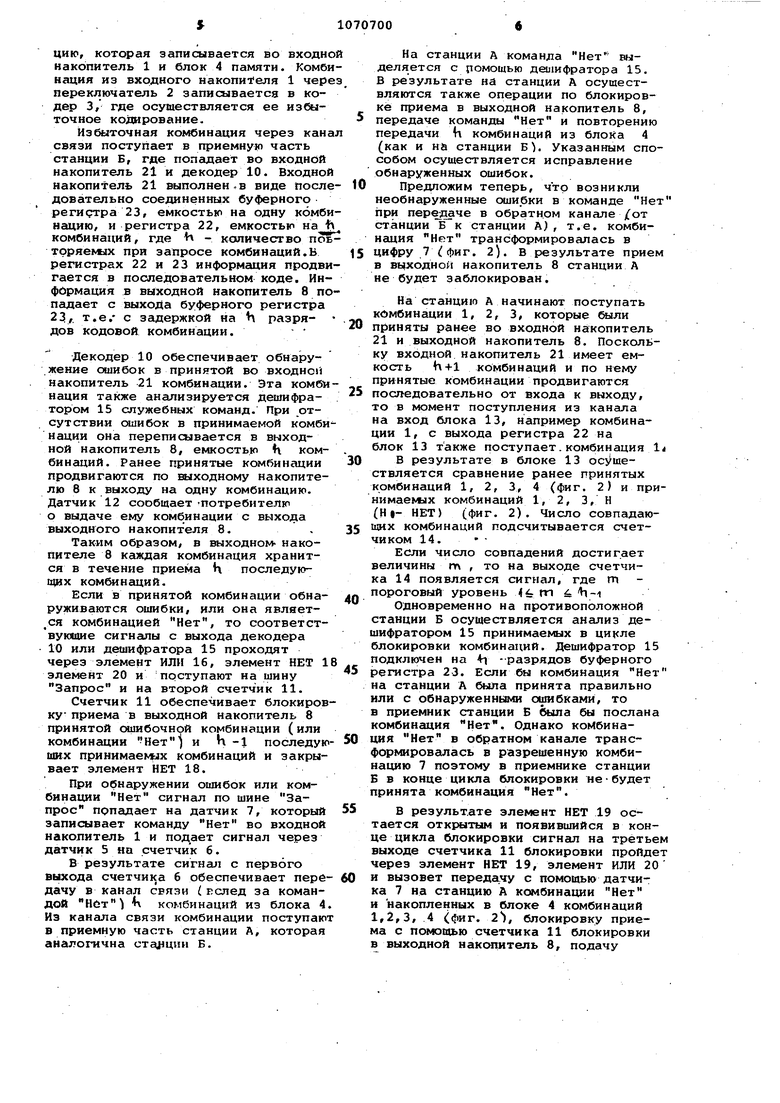

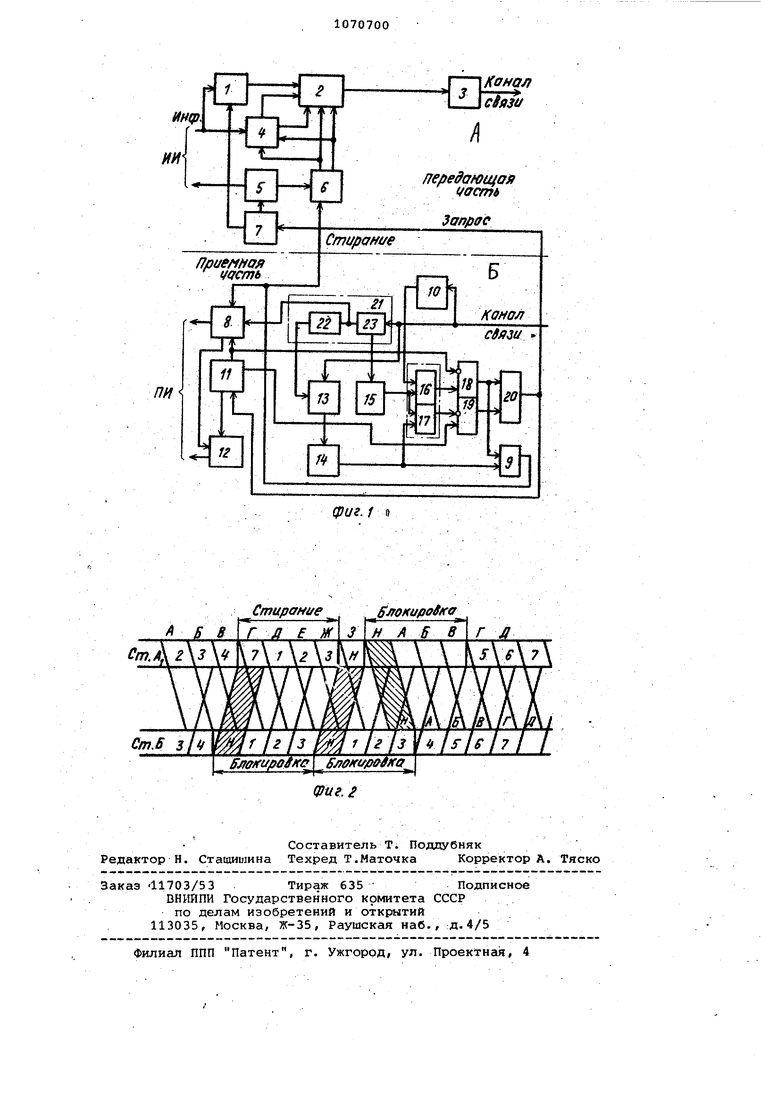

Наиболее близким к предлагаемому является устройство для защиты от ошибок, содержащее на передаче последовательно соединенные входной накопитель, переключатель и кодер, последовательно соединенные счетчик блокировки и блок памяти, первы выход которого подсоединен к второму входу переключателя, к третьему входу которого подключен второй выход блока памяти, второй вход которого объединен с четвертым входом переключателя и подключен к второму выходу счетчика блокировки, первый выход которого подсоединен к пятому входу переключателя, а также последовательно соединенные датчик команд и датчик сигналов обмена, при этом второй вход блока памя.ти объединен с первым- входом входного накопителя и является информациЛнным входом, а к второму входу входного накопителя подключен выход датчика команд, а на приеме-последовательно соединенные счетчик блокировки, выходной накопитель и датчик сигналов обмена, к второму входу которого подключен второй-выход счетчика блокировки, третий выход которого подсоединен к первому входу первого элемента НЕТ, последовательно соединенные входной накопитель и дешифратор служебных команд, а также декодер и первый элемент ИЛИ, выход которого подсоединен к входу Запрос датчика команд и входу счетчика блокировки, второй выход входного накопителя подсоединен к второму входу выходного накопителя, а вход входного накопителя объединен с входом декодера и является входом канала связи, выход декодера подсоединен к второму входу счетчика блокировки и входу Ошибка датчика команд, выход дешифратора служебных команд подсоединен к первому входу первого элемента ИЛИ, первому входу первого элемента НЕТ и через счетчик подсоединен к третьему входу выходного накопителя и первому входу элемента И на передаче, к второму входу которого подключен вход Запрос датчика команд, а выход подсоединен к йервому входу счетчика ,блокировки, к второму входу которог подключен третий выход датчика команд, при этом на приеме третий выход счетчика блокировки через :пос ледовательно соединенные первый элемент НЕТ и элемент задержки подсоединен к второму входу.первого элемента ИЛИ, к третьему входу кото рого подключен выход первого элемен та НЕТ. В устройстве для защиты от ошибо происходит Испрачление искажений ти па вставок и выпадений комбинаций при правильном приеме двух следующих подряд комбинаций Нет С21. Однако недостатком известного устройства для защиты от ошибок является появление вставок и выпадени комбинации при трансформации команды Нет в разрешенную комбинацию и при искажении хотя бы одной коман ды Нет из двух- посылаемых. Цель изобретения - повышение ве роятности обнаружения ошибок путем снижения вставок.и выпадений комби наций. i Поставленная цель достигается тем, что в устройство для заищты от ошибок, содержащее на передаче последовательно соединенные входной накопитель, переключатель и кодер, последовательно соединенные счетчик блоки 5б1йи и блок памяти, первый выход которого подсоединен к второму входу переключателя, к третьему входу которого подключен второй выход блока памяти, второй вход котор го объединен с четвертым входом переключателя и подключен к второму выходу счетчика блокировки, nejpвый выход которого подсоединен к пя тому входу переключателя, а также последовательно соединенные датчик команд и датчик сигналов обмена, при этом второй вход блока памяти объединен с первым входом входного накопителя и является информационны входом, а к второму входу входного накопителя подключен выход датчика команд, а на приеме - последователь но соединенные счетчик блокировки, выходной накопитель и датчик сигналов обмена, к второму входу которог подключен второй выход счетчика бло кировки, третий выход которого подсоединен к первому входу первого элемента НЕТ, последовательно соеди ненные входной накопитель и дешифра тор служебных команд, а такяне декодер и первый элемент ИЛИ, выход которого подсоединен к входу Запро датчика команд и входу счетчика блокировки, второй выход входного накопителя подсоединен к второму входу выходного накопителя, а вход входного накопителя объединен с входом декодера и является входом канала связи, в&едены на приеме последовательно соединенные блок сравнения, счетчик совпадений и элемент И и последовательно соединенные блок элементов ИЛИ и второй элемент НЕТ, выход которого подсоединен к первому зходу элемента ИЛИ и второму входу элемента И, выход которого подсоединен к третьему входу выходного накопителя « первому входу счетчика блокировки на передаче, к второму входу первого элемента ИЛИ подключен выход первого элемента НЕТ, к второму входу которого подключен второй выход блока элементов ИЛИ, первый вход которого подключен к выходу счетчика совпадения, второй вход подключен к вцходу дешифратора служебных команд, а третий вход блока элементов ИЛИ подключен к выходу декодера, первый выход счетчика блокировки подсоединен к второму входу второго элемента НЕТ, третий выход входного накопителя подсоединен к первому входу блока сравнения второй вход которого объединен с входом входного накопителя, а на передаче выход датчика сигналов обмена подсоединен к второму входу счетчика блокировки. Входной накопитель на приеме выполнен в виде последовательно соединенных буферного регистра и регистра, вход которого является вторым выходом, а выход - третьим выходом входного накопителя, второй выход буферного регистра является первым выходом, а вход - входом входного накопителя. На фиг. 1 представлена структурно-электрическая схема устройства для защиты от ошибок; на фиг. 2 пояснение логики работы устройства для защиты от ошибок. Устройство для защиты от ошибок содержит на передаче входной накопитель 1, переключатель 2, кодер 3, блок 4 пгшяти, датчик 5 сигналов обмена, счетчик 6 блокировки, датчик 7 команд, на приеме, выходной накопитель 8, элемент И 9, декодер 10, счетчик 11 блокировки, датчик 12 сигналов обмена, блок 13 сравнения, счетчик 14 совпадений, дешифратор 15 служебных, команд, блок элементов ИЛИ 16 и 17, элементы НЕТ 18 и 19, элемент ИЛИ 20, входной накопитель 21, содержащий регистр 22 и буферный регистр 23. Усзгройство для э.ащиты от ошибок работает следующим образом. При отсутствии искажений в принимаемой информации датчик 5 сигналов обмена станции А посылает, источнику информации (W) сигнал о готовности принять от него очередную комбинацию, которая записывается во входной Накопитель 1 и блок 4 памяти. КомбиНсщия из входного накопителя 1 через переключатель 2 записывается в кодер 3, где осуществляется ее избыточное кодирование.

Избыточная комбинация через канал связи поступает в приемную часть станции Б, где попгщает во входной накопитель 21 и декодер 10. Входной накопитель 21 выполнен.в виде последовательно соединенных буферного регис тра 23, емкостью на одну комбинацию, и регистра 22, емкостью на t. комбинаций, где - количество ПОБтрряеких при запросе комбинаций.Б регистрах 22 и 23 информация продвигается в последовательном коде. Информация в выходной накопитель 8 попадает с выхода буферного регистра 23/. т.е.- с задержкой на h разря- дов кодовой комбинации.

Декодер 10 обеспечивает обнаружение ошибок в принятой во входной накопитель 21 комбинации. Эта комбинация также анализируется дешифратором 15 служебных команд. При отсутствии сяиибок в принимаемой комби Нации она переписывается в внходной накопитель 8, емкостью Н ком- . бинаций. Ранее принятые комбинации 30 продвигаются по выходному накопителю 8 к выходу на одну комбинацию. Датчик 12 сообщает -потребителю о выдаче ему комбинации с выхода выходного накопителя 8. 35

Таким образом, в выходном- накопителе 8 каждая комбинация хранится в течение приема h последуюоц х комбинаций.

Если в принятой комбинации обна- дд руживаются ошибки, или она является комбинацией Нет, то соответствующие сигналы с выхода декодера 10 или дешифратора 15 проходят через элемент ИЛИ 16, элемент НЕТ 18 . элемент 20 и поступают на шину Запрос и на второй счетчик 11.

Счетчик 11 обеспечивает блокировку приема в выходной накопитель 8 принятой сииибочной комбинации (или комбинации и Н -1 последую- ших принимаемых комбинаций и закрывает элемент НЕТ 18.

При обнаружении ошибок или комбинации Нет сигнал по шине Запрос попадает на датчик 7, который 55 записывает команду Нет во входной накопитель 1 и подает сигнал через датчик 5 на счетчик 6.

В результате сигнал с первого выхода счетчика 6 обеспечивает пере- 60 дачу в канал связи { Еслед за команой HdT комбинаций из блока 4. Из канала связи комбинации поступают в приемную часть станции А, которая аналогична Б.

На станции А команда Нет выделяется с помощью деишфратора 15. В результате на станции А осуществляются также операции по блокировке приема в выходной накопитель 8, передаче команды Нет и повторению передачи Ц комбинаций из блока 4 (как и на станции Б. Указанным способом осуществляется исправление обнаруженных ошибок.

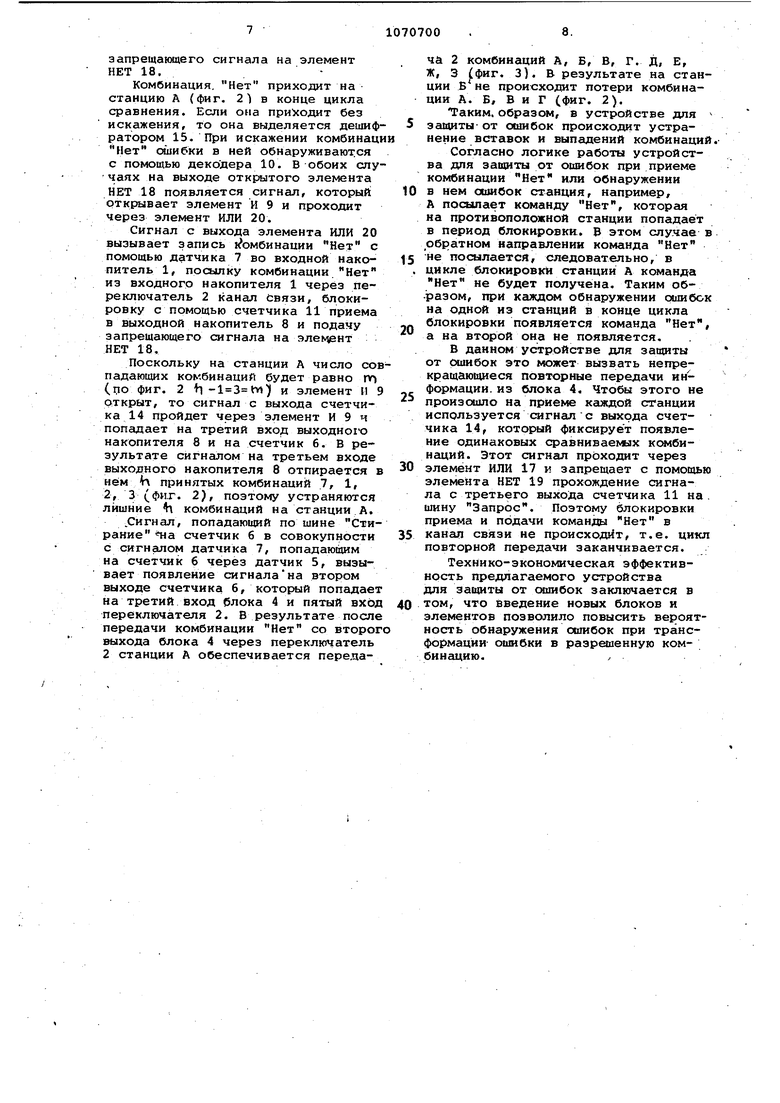

Предложим теперь, что возникли необнаруженные ошибки в команде Не при передаче в обратном канале станции Б к станции А), т.е. комбинация Нет трансформировалась в цифру . 2). В результате прием в выходной накопитель 8 станции А не будет заблокирован.

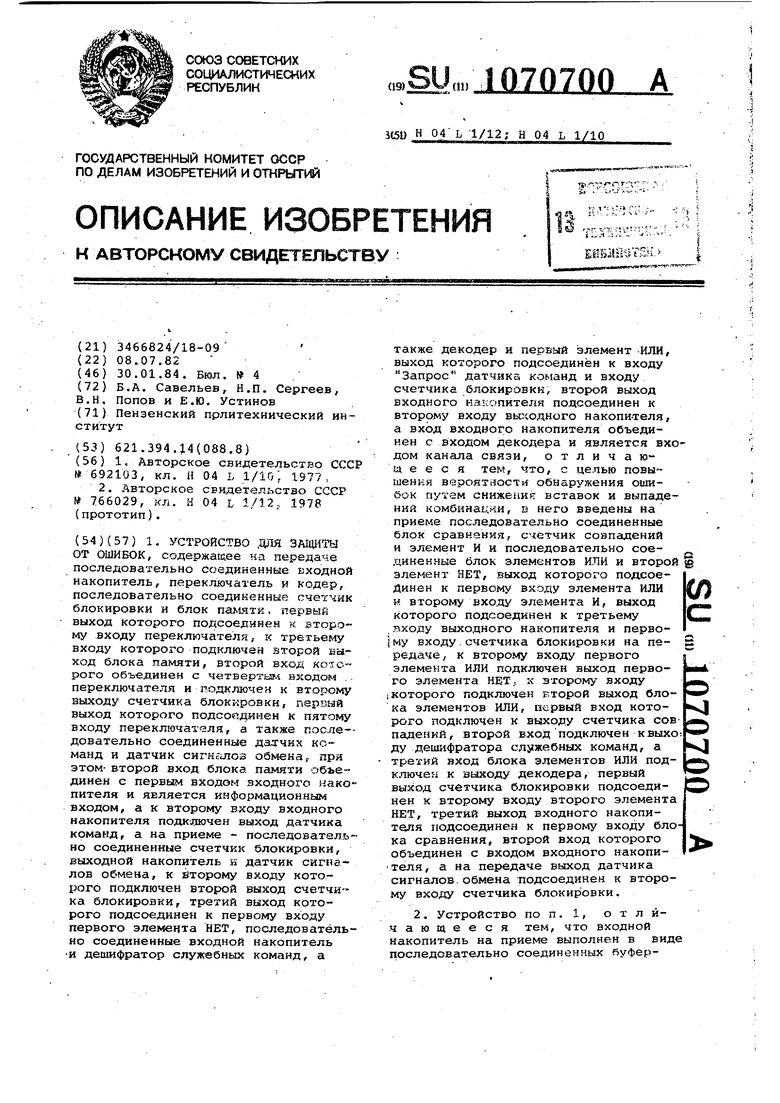

На станцию А начинают поступать комбинации 1, 2, 3, которые балк приняты ранее во входной накопитель 21 и выходной накопитель 8. Поскольку входной накопитель 21 имеет емкость h+l комбинаций и по нему принятые комбинации продвигаются последовательно от входа к выходу, то в момент поступления из канала на вход блока 13, например комбинации 1, с выхода регистра 22 на блок 13 также поступает.комбинация 1

Б результате в блоке 13 ос ществляется сравнение ранее принятых комбинаций 1, 2, 3, 4 (фиг. 2) и принимаемых комбинаций 1, 2, 3, Н (HI- НЕТ) (фиг. 2). Число совпадающих комбинаций подсчитывается счетчиком 14.

ЕСЛИ число совпадений достигает величины m , то на выходе счетчика 14 появляется сигнал, где m пороговый уровень t m 6 ii-i

Одновременно на противоположной станции Б осуществляется анализ дешифратором 15 принимаемых в цикле блокировки комбинаций. Дешифратор 15 подключен на 4i -разрядов буферного регистра 23. Если бы комбинация Нет на станции А была принята правильно или с обнаруженными ошибками, то в приемник станции Б была бы послана комбинация Нет. Однако комбинация Нет в обратном канале трансформировалась в разрешенную комбинацию 7 поэтому в приемнике станции Б в конце цикла блокировки не-будет принята комбинация Нет.

В результате элемент НЕТ 19 остается открытым и появившийся в конце цикла блокировки сигнал на третье выходе счетчика 11 блокировки пройде через элемент НЕТ 19, элемент ИЛИ 20 и вызовет передачу с помощью датчика 7 на станцию А комбинации Нет и накопленных в блоке 4 комбинаций 1,2,3, 4 (фиг. 2), блокировку приема с помощью счетчика 11 блокировки в выходной накопитель 8, подачу

запрещающего сигнала на элемент НЕТ 18.

Комбинация. Нет приходит на станцию А (фиг. 2} в конце цикла сравнения. Если она приходит без искажения, то она выделяется дешифратором 15. При искажении комбинаци Нет сшибки в ней обнаруживаются с помощью декодера 10. В-обоих случаях на выходе открытого элемента НЕТ 18 появляется сигнал, который открывает элемент И 9 и проходит через элемент ИЛИ 20.

Сигнал с выхода элемента ИЛИ 20 вызывает запись омбинации Нет с помощью датчика 7 во входной накопитель 1, посылку комбинации Нет из входного накопителя 1 через переключатель 2 канал Связи, блокировку с помощью счетчика 11 приема в выходной накопитель 8 и подачу запрещающего сигнала на эленцент НЕТ 18,

Поскольку на станции А число совпадающих комбинаций будет равно го (rio фиг. 2 ii-l и элемент И 9 открыт, то сигнал с выхода счетчика 14 пройдет через элемент И 9 ч попадает на третий вход выходнох-о накопителя 8 и на счетчик 6. В результате сигналом на третьем входе выходного накопителя 8 отпирается в нём V принятых комбинаций 1, 1, 2, 3 (фи.г. 2), поэтому устраняются лишние 4i комбинаций на станции А.

.Сигнал, попадающий по шине Стирание на счетчик б в совокупности с сигналом датчика 7, попадающим на счетчик 6 через датчик 5, вызывает появление сигналана втором выходе счетчика 6, который попадает на третий вход блока 4 и пятый вход переключателя 2. В результате после передачи комбинации Нет со второг выхода блока 4 через переключатель 2 станции А обеспечивается передача 2 комбинаций А, Б, В, Г. Д, Е, Ж, 3 (фиг. 3). В результате на станции Б не происходит потери комбинации А. Б, В и Г (фиг. 2).

Таким, образом, в устройстве для . защиты-от сшибок происходаст устранение вставок и выпадений комбинаций.

Согласно логике работы устройства для защиты от ошибок при приеме комбинации Нет или обнаружении

0 в нем ошибок станция, например, А посылает команду Нет, которгш на противоположной станции попадает в период блокировки. В этом случае в обратном направлении команда Нет не посылается, следовательно, в

5 цикле блокировки станции А команда Нет не будет получена. Таким образом, при каждом обнаружении сялибок на одной из станций в конце цикла блокировки появляется команда Нет,

0 а на второй она не появля ется.

В данном устройстве для защиты от сяиибок это может вызвать непрекращающиеся повторные передачи информации, из блока 4. Чтобы этого не

5 произошло на приеме каждой станции используется сигнал с выхода счетчика 14, который фиксирует появление одинаковых cpaвнивae 4ыx ксялб наций. Этот сигнал проходит через

0 элемент ИЛИ 17 и запрещает с помощью элемента НЕТ 19 прохождение сигнала с третьего выхода счетчика 11 на. шину Запрос. Поэтому блокировки приема и подачи команды Нет в канал связи ие происходит, т.е. цикл

5 повторной передачи заканчивается.

Технико-экономическая эффективность предлагаемого устройства для защиты от сшшбок заключается в том, что введение новых блоков и

0 элементов позволило повысить вероятность обнаружения ошибок при трансфо мации ошибки в разрешенную комбинацию.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство обнаружения вставок и выпадений информации в системах передачи данных | 1977 |

|

SU692103A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-01-30—Публикация

1982-07-08—Подача