. ,1

Изобретение относится к вычислительной технике, может быть использовано для обработки информации от частотных датчиков или в составе/ цйфро-частотных вычислительных устройств ,

Известно устройство для вычитания неравномерных частотно-импульсных последовательностей i, содержащее реверсивный счетчик, схему функциоНсшьной синхронизации, триггер и многовходовые логические элементы,

Известно также устройство для вычитания неравномерных частотно-импульсных последовательностей , содержа11|1её раверсивный счетчик, элементы запрета, двухвходовые и многовходовые элементы И.

Общим недостатком этих устройств является сложность конструктивной реализации.

Прототипом изобретения является устройство для вычитания неравномерных частотно- импульсных последовательностей з, содержащее реверсивный счетчик, входы которого соединены со входными шинами устройства, а выходы стараего разряда через форлшрователи импульсов соответственно

подк.шочены к выхолам устройства, единичным и нулевым установочным входам всех разрядов реверсивного счетчика.

Прототип при правильном выборе числа разрядов ликвидирует дифференциальный характер выходного сигнала, т.е. исключает возможность одновременного формирования импульсных последовательностей на обоих выходах

10 устройства. Однако выходная частота устройства

fb

в среднем равная разности средbtXних значений F и F входных частот, сама является существенно неравномер15ной, т.е. отдельные периоды выходной частоты мЬгут быть как больше, так и значительно меньше среднего значения вЫХ-р -Ра

Целью изобретения является уменьше20ние неравномерности выходной импульсной последовательности.

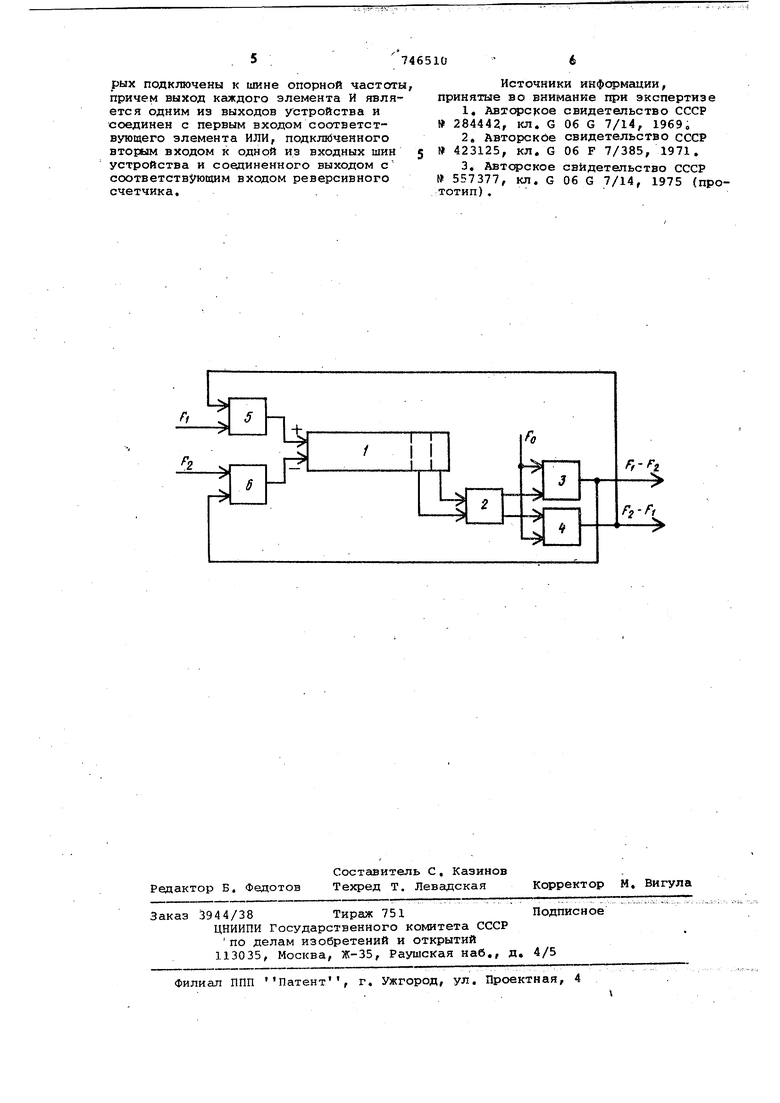

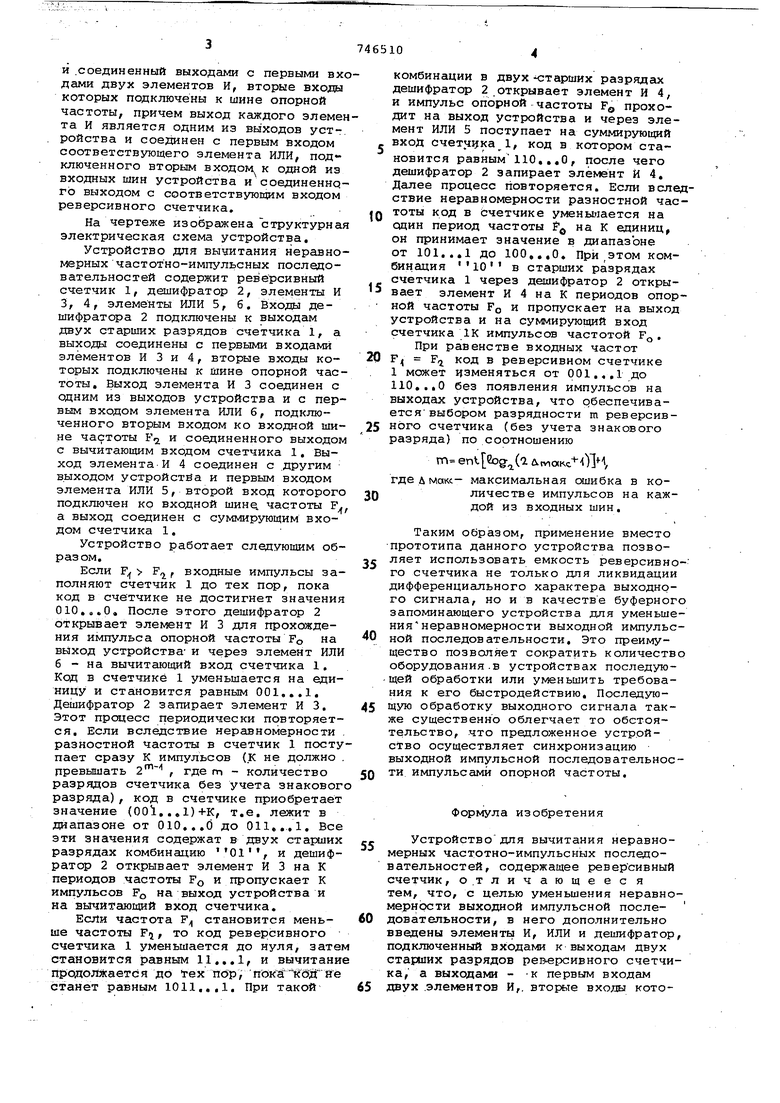

Эта цель достигается гем, что в устройство для вычитания неравномерных частотно-импульсных последовательностей, содержащее реверсивный счетчик, дополнительно введены эле- менты И и ИЛИ и дешифратор, подключенный входами к выходам двух старших разрядов реверсивного счетчика и .соединенный выходами с первыми вх дами двух элементов И, вторые входы которых пояключёны к шине опорной частоты, причем выход каждого элеме та И является одним из выходов устройства и соединен с первым входом соответствующего элемента ИЛИ, подключенного вторым входом к одной из входных шин устройства и соединенного выходом с соответствующим входом реверсивного счетчика. На чертеже изображена структурна электрическая схема устройства. Устройство для вычитания неравно мерных частотно-импульсных последовательностей содержит реверсивный счетчик 1, дешифратор 2, элементы И 3, 4, элементы ИЛИ 5, 6. Входда дешифратора 2 подключены к выходам двух старших разрядов счетчика 1, а выходы соединены с первыми входами элементов И 3 и 4, вторые входы которых подключены к шине опорной час тоты. Выход элемента И 3 соединен с синим из выходов устройства и с первым входом элемента ИЛИ б, подключенного вторым входом ко входной шине частоты и соединенного выходом с вычитающим входом счетчика 1, Выход элемента-И 4 соединен с другим выходом устройства и первым входом элемента ИЛИ 5, второй вход которого подключен ко входной шин. частоты F а выход соединен с суммирующим входом счетчика 1, Устройство работает следующим образом. Если F F f входные импульсы заполняют счетчик 1 до тех пор, пока код в счетчике не достигнет значения 010,а.О, После этого дешифратор 2 открывает элемент И 3 для прохождения импульса опорной частоты FO на выход устройства и через элемент ИЛИ б - на вычитающий вход счетчика 1, Кся в счетчике 1 уменьшается на единицу и становится равным 001,.,, Дешифратор 2 запирает элемент И 3, Этот процесс периодически повторяется, ЕСЛИ вследствие неравномерности разностной частоты в счетчик 1 посту пает сразу К импульсов (К не должно превышать 2 , где m - количество разрядов счетчика без учета знаковог разряда), код в счетчике приобретает значение (001,,.1)+К, т,е, лежит в диапазоне от 010,.,О до 011,,.,, Все эти значения содержат в двух стариих разрядах комбинацию 01, и дешифратор 2 открывает элемент И 3 на К периодов частоты F и пропускает К импульсов FO на выход устройства и на вычитающий вход счетчика, Если частота F становится меньше частоты F/J, то код реверсивного счетчика 1 уменьшается до нуля, зате становится равным 1,,,, и вычитани продолжается до тех пор, ( станет равным 1011,,,, При такой комбинации в двух ч;тарших разрядах дешифратор 2 открывает элемент И 4, и импульс опорной частоты F проходит на выход устройства и через элемент ИЛИ 5 поступает на суммирующий вход счетчцка, код в котором становится равным110,.,0, после чего дешифратор 2 запирает элемент И 4, Далее процесс повторяется. Если вследствие неравномерности разностной частоты код в счетчике уменьшается на один период частоты Р на К единиц, он принимает значение в диапазоне от 101,,. до 100,,,О, Приватом комбинация 10 в старших разрядах счетчика 1 через дешифратор 2 открывает элемент И 4 на К периодов опорной частоты FO и пропускает на выход устройства и на суммирующий вход счетчика 1К импульсов частотой FQ, При равенстве входных частот F F код в реверсивном счетчике 1 может изменяться от 001,,, до 110,,,О без появления импульсов на выходах устройства, что обеспечивается выбором разрядности m реверсивного счетчика (без учета знакового разряда) по соотношению т (a Лмакс ОЗм, где д Макс- максимальная ошибка в количестве импульсов на каждой из входных шин. Таким образом, применение вместо прототипа данного устройства позволяет использовать емкость реверсивного счетчика не только для ликвидации дифференциашьного характера выходного сигнала, но и в качестве буферного запоминающего устройства для уменьшения неравномерности выходной импульсной последовательности. Это преимущество позволяет сократить количество оборудования.в устройствах последующей обработки или уменьшить требования к его быстродействию. Последующую обработку выходного сигнала также существенно облегчает то обстоятельство, что предложенное устр.ойство осуществляет синхронизацию выходной импульсной последовательности импульсами опорной частоты. Формула изобретения Устройство для вычитания неравномерных частотно-импульсных последовательностей, содержащее реверсивный счетчик, о.тличающеес я тем, что, с целью уменьшения неравномернсэсти выходной импульсной последовательности, в него дополнительно введены элементы И, ИЛИ и дешифратор, подключенный входами к выходам двух старших разрядов реверсивного счетчика, а выходами - К первым входам двух .элементов И,, вторые входы которых подключены к шине опорной частоты, причем выход каждого элемента И является одним из выходов устройства и соединен с первым входом соответствующего элемента ИЛИ, подключенного вторлм входом к одной из входных шин устройства и соециненного выходом с соответствующим входом реверсивного счетчика,.

Источники информации, принятые во внимание при экспертизе

1,Автсчрское свидетельство СССР 284442, кл. G Об G 7/14, 1969,

2,Авторское свидетельство СССР 423125, кл, G 06 F 7/385, 1971.

3,Авторское свидетельство СССР

557377, кл. G 06 G 7/14, 1975 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный аналого-цифровой преобразователь | 1989 |

|

SU1702528A1 |

| ПАТЕНТКО-ТЕХ;1И'!ЕСНАеБИБЛИОТЕКА | 1971 |

|

SU306473A1 |

| Преобразователь кода в частоту | 2023 |

|

RU2805259C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ | 1973 |

|

SU389517A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Преобразователь частоты в код | 1971 |

|

SU443482A1 |

| Частотно-импульсное вычитающее устройство | 1977 |

|

SU708350A1 |

| Частотно-импульсное диференцирующее устройство | 1977 |

|

SU640315A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

Авторы

Даты

1980-07-05—Публикация

1977-12-19—Подача