ла пуска-останова соединен с соответствующим входом регнстра микрокоманд

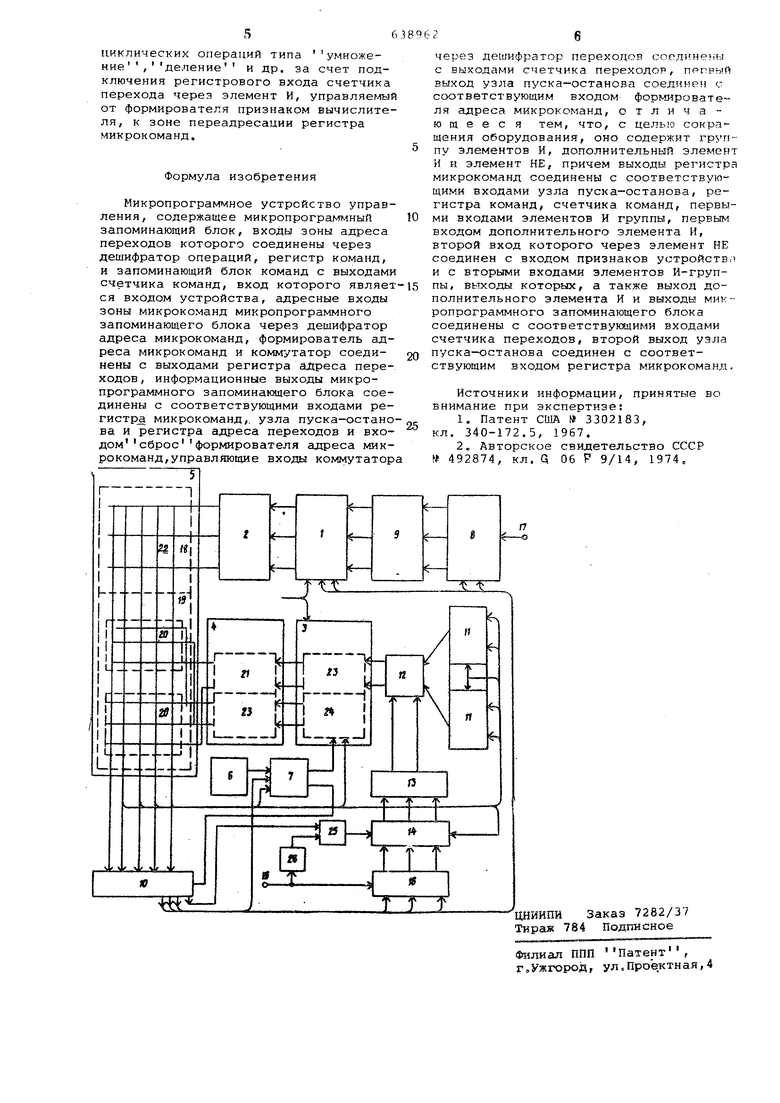

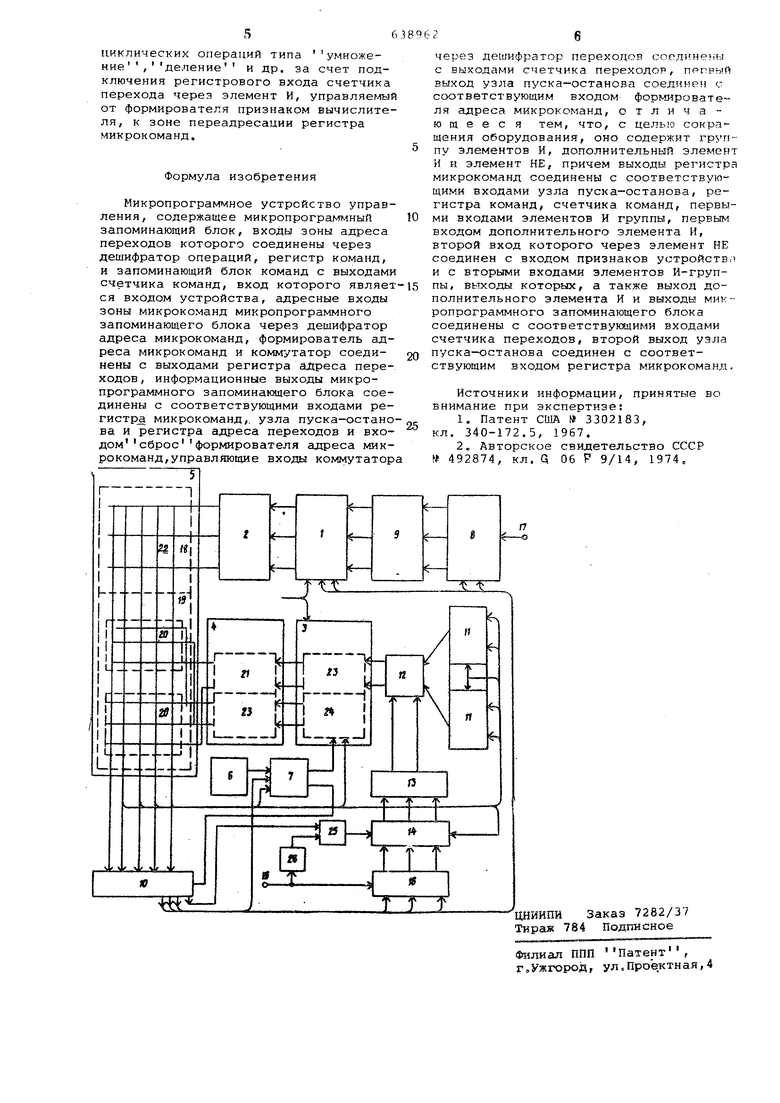

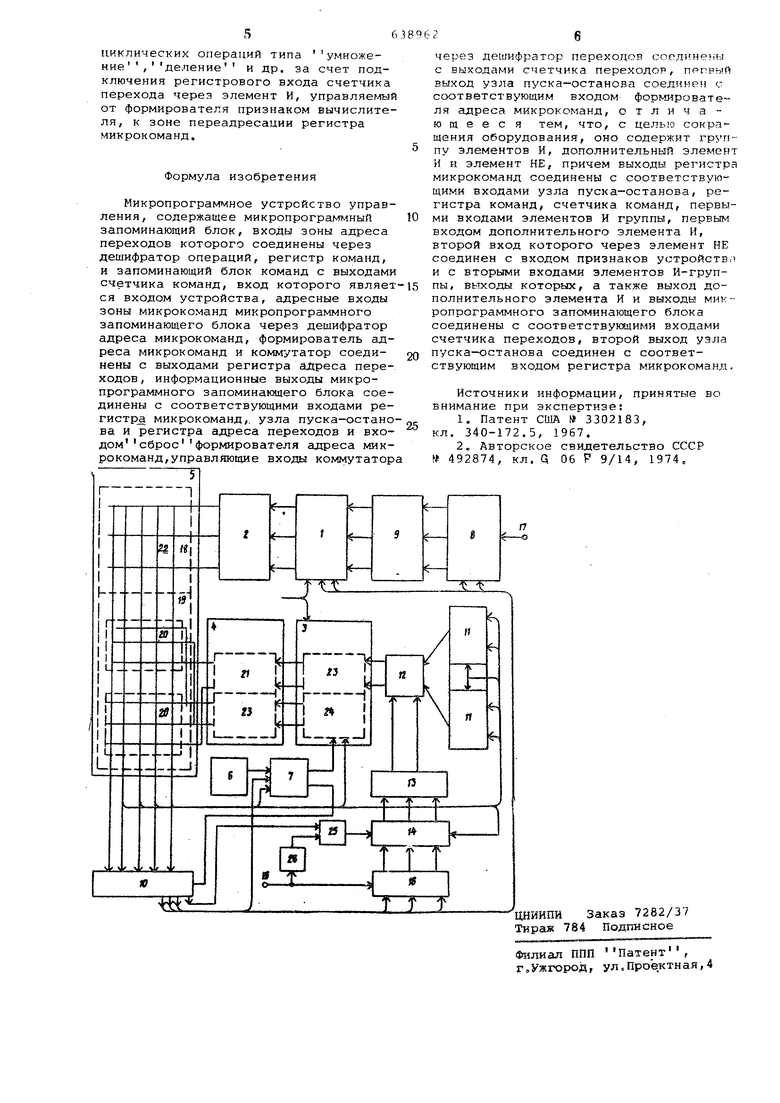

На чертеже дана функциональ ая схема микpoпpoгpa лмнoгo устройства.

Оно содержит регистр 1 команд., дешифратор 2 операций, формирователь 3 адреса микрокоманд, дешифратор 4 адреса микрокоманд, микропрограммный запоминающий блок 5, генератор б, узел 7 пуска-останова счетчик 8 команд, запоминающий блок 9 команд, регистр 10 микрокоманд, регистры 11 адреса переходов J Koivff.iyTaTop 12,дешифратор 13 переходов, счетчик переходов 14, вход 15 признаков устройства, группу элементов И 16, вход 17 устройства, зону 18 адресов переходов и зону 19 микрокоманд с микропрограммами 20 запоминающего блока 5, узел 21 выборки микропрогра -1м, узел 22 выборки микрокоманд MHKponporpaN.ffl3j, регистр 23 адреса микропрограмг-1Ы, счетчик 24 адреса микрокоманд .микропрогра лмы,дополнительный элемент И 25 и элемент НЕ 26,

Mйкpoпppгpa a нoe устройство управления работает следующим образом.

В последнем такте операции на выкоде регистра 10 микрокоманд формируются управляюйще сигналы, отключгнощие узел 7 пуска-останова и Подключающие выход -I регистра команд. При зтом один из вгАчодов дешифратора 2 операций возбуждают соответствующую адресную шину зоны 18 переходов запоминающего устройства 5 со словом, содержащим все началььлле адреса микропрогpaMMj используемых в данной операции и ряд признаков, например выбор команды, выбор операнда , сложеформирование адреса

ние

.-)то

слово переписывается в регистры 11 адреса переходов, сигналы управления этого слова обеспечивают сброс счетчика 14 переходов и счетчика 24 адpeCci микрокоманд микропрограм / Ы формирователя 3 адреса микрокоманд, а также., признс1ки этого слова частично переписыза.ются в регистр 10 микрокоманд и сохраняются в нем на протяжени выполнения операции При этом ко вхо дам регистра 23 адреса микропрограмм формирователя 3 адреса микрокоманд с помощью коммутатора 12, управляемого дешифратором 13 переходов, подклю чаются выходы регистра 11 адреса перехода с начальным адресом микропрограммы выборки операнда, по которому на соответствующей микропрограмме 20 зоны 19 микрокоманд запоминающего блока 5 в регистр микрокоманды 10 записывается первая микрокоманда данзюй микройрограмг ш. При этом подключаетс узел 7 пуска-останова, и на вход счет чика 24 адреса микрокоманд мнкропрограг-оды формирователя 3 адреса микрокоманд подаются импульсы из генератора 6 J что приводит к последовательной выборке Bcej{ микрокоманд этой микропрограммы 20 из зоны микрокоманд 19 запоминающего блока 5, которые переписываются в регистр 10 микрокоманд. В последней микрокоманде этой микропрограмг формируется импульс сброса счетчика 24 адреса микрокоманд микропрограммы формирователя 3 адреса микрокоманд, импульс блокировки узла 7 пуска-останова и импульс, переводящий счетчик 14 переходов в следующее по порядку состояние. При этом ко входам регистра 23 адреса микропрограмм формирователя 3 адреса микрокоманд с помощью ког 1мутатора 12, управляемого дешифратором 13 переходов, подключаются выходы регистра 11 адресов переходов с начальным адресом микропрограм /гы, например сложение, по которому из соответствующей микропрограг4мы 20 зоны 1Э микрокоманд запоминающего блока 5 в регистр 10 микрокоманд последовательно переписываются для исполнения все микрокоманды данной микропрограммы, т.е. устройство работает так же,как и при выполнении предыдущей микропрограммы.

Умножение , деление и другие циклические операции выполняются как микропрограммы сложения и сдвига с возвратом по адресу, записанному в регистр 10 микрокоманд, которые зацикливаются на столько циклов, сколько потребуется для того, чтобы из формирователя признаков вычислителя пришел сигнал об окончании выполнения данной операции, только после этого микропрограммное устройство управления сможет перейти на выполнение следующей по порядку микропрограммы ,

В таком микропрограмл ном устройств управления зона микрокоманд запоминающего блока разбита на микропрограммы элементарных операций типа формирование адреса , выборка команды , выборка операнда , сложение, сдвиг и т.д., которых будет не более 15, а число микрокоманд в каждо микропрограмме не более 4, что приводит к необходимости разбить дешифрато адреса микрокоманд на узел выборки микропрограмм и узел выборки микрокоманд микропрограммы, а формирователь адреса гл-гкрокоманд - на регистр адреса микропрограммы и счетчик адреса .микрокоманд микропрограммы, а также к необходимости введения ряда новых связей, что позволяет исключить многоразрядный регистр позиционного алреса перехода с элементами И и ИЛИ за счет введения одноразрядной связи счетчика перехода с выходом регистра микрокоманды, уменьшить разрядность регистро адреса переходов и их количество, так как количество микропрограмм элементарных операций значительно меньше ко личества микроког-инд, отличающихся друг от друга управляЕоадими сигналами, а также облегчить исполнение

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Микропрограммное устройство управления | 1977 |

|

SU746516A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1978 |

|

SU742937A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Авторы

Даты

1978-12-25—Публикация

1976-01-23—Подача