Изобретение относится к вычислительной технике и может быть использовано при создании надежных быстродействующих систем памяти на базе больших интегральных микросхем со словной организацией.

Цель изобретения - повышение надежности за счет фиксации ошибок, возникающих в двух модулях памяти одновременно.

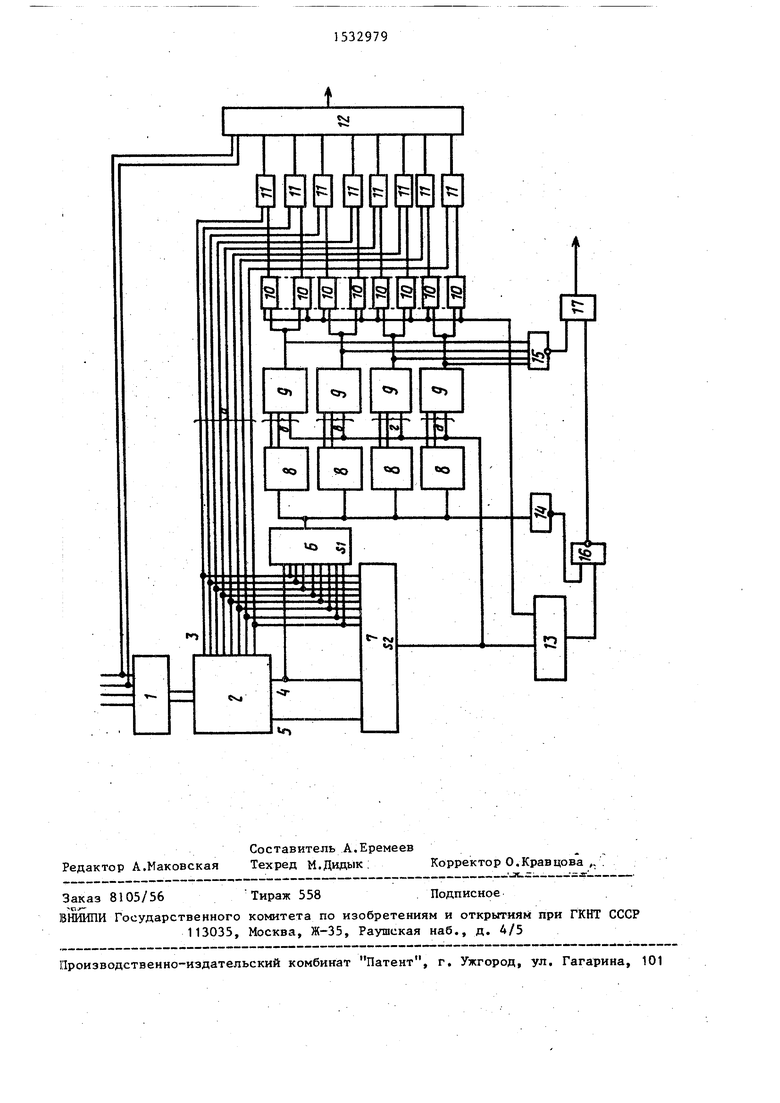

На чертеже представлена структурная схема постоянного запоминающего устройства с самоконтролем.

Устройство содержит адресный блок 1, накопитель 2, выходы 3 информационных разрядов, выходы 4 и 5 контрольных разрядов, первый сумматор 6, второй сумматор 7, блоки 8 вычисления частных синдромов, блоки U сравнения, группу элементов И 10, группу сумматоров П по модулю два, коммутатор 12, дополнительный блок 13 сравнения, первый J4, второй 15, третий 16 элементы ИЛИ-НЕ, элемент И 17.

Устройство использует для обнаружения и исправления ошибок модульные коды. Память строится на полупроводниковых приборах с многоразрядной (В-разрядной) организацией. Слово, хранимое в накопителе, делится на N групп символов (модулей) по В символов в каждой группе. Для обнаружения

ел

со

N9

0 J

СО

31532979

и исправления одиночного отказа ИМП в слове требуется В + N дополнительных разрядов .

Проверочная матрица имеет виц

ум

2 ни но

Ч

О

s В + 2;

- единичная матрица порядка В;

- нулевая матрица порядка В;

- матрица, полученная из L

циклическим сдвигом всех В + + 1 ее строк на i строк вниз и отбрасыванием последней строки, а

Г 0000...0 1 I П J

Устройство позволяет исправить любые одиночные отказы ИМП в каждом слове накопителя и обнаруживает ошибки, вызванные двумя и более отказами ИШ в слове. Обнаружение ошибок,вызванных двумя и более отказами ИМП в слове накопителя, производится путем анализа состояний сумматоров первого и второго и выходных сигналов блоков сравнения.

Устройство работает следующим образом .

Пример 1. Пусть в накопителе 2 хранится сообщение длины К

16 бит, а В

/XT16

4, тогда N --,-

4. Проверочная матрица будет иметь

вид

Н

24,6

контрольные разряды хранятся в двух дополнительных модулях накопителя 2. Сообщение 0000 0000 1000 0001 будет храниться в накопителе 2 с учетом контрольных разрядов в виде 0000 000

10000001 1001 1010.

Пусть информация исказилась в 1-м модуле, т.е. 1100 0000 1000 0001

10011010.

На выходе первого сумматора 6 - состояние (синдром S), равное 1100; на выходе второго сумматора 7 (синдром S2) - состояние, равное 0110.

Члпки 8 вычисления частных синдромов (умножители) производят операцию

5

0

умножения S S, L, , где ,

2, 3, 4, и на выходе блоков вычисления частных синдромов 8 соответственно появляются коды:

S 0110

S 001 1

S 1001

ч &

1000

На вторых входах первого блока 9

сравнения-код ОНО, тогда на выходе первого блока 9 сравнения устанавливается логическая единица, поскольку коды совпадают.

5Следовательно, на вторых выходах

соответствующих элементов V 10, соединенных с выходом первого блока 9 сравнения, формируется рятрешающий . сигнал и код синдрома 5 через эле0 менты И 10 передается на первые входы сумматоров 11 по модулю два, на вторые входы которых поступает искаженная информация с накопителя 2. В результате сложения по модулю два с

5 кодом синдрома S, информация восстанавливается и через коммутауор 12 при наличии сигнала на его управляющих входах поступает на информационный выход устройства.

0Так как на-первом и втором выходах

дополнительного блока 13 сравнения информация различна (код синдрома Р 1100 и код синдрома S2 0110), на его выходе формируется нулевой сигнал. Одновременно на выходе первого элемента ИПИ-НЕ 14 устанавливается нулевой сигнал, так как на его входы поступает код синдрома S , отличный от нуля. На выходе третьего элемента ИЛИ-НЕ 16 устанавливается логическая единица (сигнал, фиксирующий ошибку), но вследствие того, что на выходе второго элемента ИЛИ-НЕ 15 формируется логический нуль, сигнал ошибки устройством не формируется.

Пример 2. Пусть для приведенного выше примера информация исказилась в первом и втором модулях, то есть 1100 0010 1000 0001 1001 1010, тогда синдром S, 1J10 - выход первого сумматора 6, синдром S2 0110 - выход второго сумматора 7.

5

0

5

На выходах блоков 8 вычисления частных синдромов Формируются коды:

sr

S

с

ъъ

ч а +

01 11 ООН 1001 1100,

которые поступают на первые входы

блоков 9 сравнения, на вторые входы которых при этом поступает код синдустройства,выходы адресного блока

соединены садресными входами нако

рома S - 0110. На выходах всех бло-теля, первый и второй Ь-разрядныр

ков 9 сравнения устанавливается логический нуль, так как код синдрома 0110 не совпадает ни с одним из кодов частных синдромов.

Так как на первых и вторых входах дополнительного блока 13 сравнения коды синдромов St - 1110 и Б - 0110 различны, на его выходе формируется логический нуль. Одновременно на выходе первого элемента ИЛИ-НЕ 14 формируется нулевой сигнал, так как код синдрома S. отличен от нуля. На втором входе элемента И 17 устанавливается при этом логическая единица v (сигнал, фиксирующий ошибки в двух модулях).

На первом входе элемента И 17 также устанавливается логическая единица, так как на входах второго элемента ИЛИ-НЕ 15 зафиксированы нулевые сигналы. На выходе постоянного запоминающего устройства с самоконтролем - выходе элемента И 17 - появля- ется сигнал ошибки, которую устройство не может исправить. Так как передача синдрома S на сумматоры 11 по модулю два блокирована элементами И 10, на вторых входах которых сформирован логический нуль, коррекция ин- Аормации в этом случае не происходит, и на выходе коммутатора 12 присутствует информация, переданная из накопителя 2.

По сравнению с прототипом надежность запоминающего устройства с самоконтролем выше за счет обеспечения возможности регистрации ошибок, возникающих в двух модулях памяти одновременно, путем сравнения кодов двух синдромов, а также анализа результатов сравнения частных синдромов с кодом одного из синдромов. При этом быстродействие устройства сохраняется.

Формула изобретения

Постоянное запоминающее устройство с самоконтролем, содержащее накопитель, состоящий из запоминающих элементов разрядностью Ь, адресный

10

20

25

30

сумматоры, блоки вычисления частны синдромов, блоки сравнения, элемен И, сумматоры по модулю два, коммут тор, причем входы первого и второг сумматоров соединены с выходами ин формационных и контрольных разрядо накопителя, выходы первого суммато соединены с входами блоков вычисле частных синдромов, выход т-го блок 15 вычисления частных синдромов (где l...b) соединен с первыми входам т-го блока сравнения, вторые входы блоков сравнения соединены с выход второго сумматора, выход m-го блок сравнения соединен с первыми входа Ь(т - 1) + i элементов И (где i l...b), вторые входы элементов И соединены с соответствующими выход первого сумматора, выходы элементо соединены с первыми входами суммат ров по модулю два, вторые входы ко рых соединены с соответствующими и формационными выходами накопителя, выходы сумматоров по модулю два со динены с информационными входами к мутатора, управляющие входы которо соединены с входами адресного блок выходы коммутатора являются информ ционными выходами устройства, от личающееся тем, что, с ц лью повышения надежности устройств в него введены элемент И, дополнительный блок сравнения, первый, вто рой и третий элементы ИЛИ-НЕ, приче входы первого элемента ИЛИ-НЕ соеди нены с первой группой входов дополнительного блока сравнения и выхода ми первого сумматора, входы второго элемента ИЛИ-НЕ соединены с выходам блоков сравнения, вторая группа вхо дов дополнительного блока сравнения соединена с выходами второго суммат ра, первый вход третьего элемента ИЛИ-НЕ соединен с выходом дополните ного блока сравнения, второй вход третьего элемента ИЛИ-НЕ соединен с выходом первого элемента ИЛИ-НЕ, а выход соединен с первым входом элемента И, второй вход которого соеди нен с выходом второго элемента ИЛИ- НЕ, а выход является выходом сигнал ошибки устройства.

35

40

45

50

55

15329796

блок, входыкоторого являются входами

устройства,выходы адресного блока

соединены садресными входами накопи0

0

5

0

сумматоры, блоки вычисления частных синдромов, блоки сравнения, элементы И, сумматоры по модулю два, коммутатор, причем входы первого и второго сумматоров соединены с выходами информационных и контрольных разрядов накопителя, выходы первого сумматора соединены с входами блоков вычисления частных синдромов, выход т-го блока 5 вычисления частных синдромов (где га l...b) соединен с первыми входами т-го блока сравнения, вторые входы блоков сравнения соединены с выходами второго сумматора, выход m-го блока сравнения соединен с первыми входами Ь(т - 1) + i элементов И (где i l...b), вторые входы элементов И соединены с соответствующими выходами первого сумматора, выходы элементов И соединены с первыми входами сумматоров по модулю два, вторые входы которых соединены с соответствующими информационными выходами накопителя, выходы сумматоров по модулю два соединены с информационными входами коммутатора, управляющие входы которого соединены с входами адресного блока, выходы коммутатора являются информационными выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены элемент И, дополнительный блок сравнения, первый, второй и третий элементы ИЛИ-НЕ, причем входы первого элемента ИЛИ-НЕ соединены с первой группой входов дополнительного блока сравнения и выходами первого сумматора, входы второго элемента ИЛИ-НЕ соединены с выходами блоков сравнения, вторая группа входов дополнительного блока сравнения соединена с выходами второго сумматора, первый вход третьего элемента ИЛИ-НЕ соединен с выходом дополнительного блока сравнения, второй вход третьего элемента ИЛИ-НЕ соединен с выходом первого элемента ИЛИ-НЕ, а выход соединен с первым входом элемента И, второй вход которого соединен с выходом второго элемента ИЛИ- НЕ, а выход является выходом сигнала ошибки устройства.

5

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU964736A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1297120A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

| Устройство для защиты от ошибок в памяти | 1982 |

|

SU1151969A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании надежных быстродействующих систем памяти на базе больших интегральных микросхем памяти со словной организацией. Цель изобретения - повышение надежности за счет фиксации ошибок, возникающих в двух модулях памяти одновременно. Устройство содержит адресный блок, накопитель, первый и второй сумматоры, блоки вычисления частных синдромов, блоки сравнения, группу элементов И, группу сумматоров по модулю два, коммутатор, дополнительный блок сравнения, первый, второй, третий элементы ИЛИ-НЕ, элемент И. Введение в устройство дополнительного блока сравнения, элементов ИЛИ-НЕ и элемента И позволяет исправить любые одиночные отказы интегральных микросхем памяти в каждом слове накопителя и обнаруживать ошибки, вызванные двумя и более отказами ИМП, в слове путем анализа состояний первого и второго сумматоров и выходных сигналов блоков сравнения. 2 ил.

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1005193A1 |

| Солесос | 1922 |

|

SU29A1 |

| Конопельке В.К., Лосев В.В | |||

| Надежное хранение информации в полупроводниковых запоминающих устройствах | |||

| М.: Радио и связь, 1986, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

Авторы

Даты

1989-12-30—Публикация

1988-02-29—Подача