(54) УСТРОЙСТВО ДЛЯ АНАЛИЗА ИНФОРМАЦИОННОЙ ПОСЛЕДОВATE ЛЬНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Генератор символов | 1988 |

|

SU1525724A1 |

| Устройство для индикации | 1979 |

|

SU798921A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство телемеханики | 1984 |

|

SU1179414A1 |

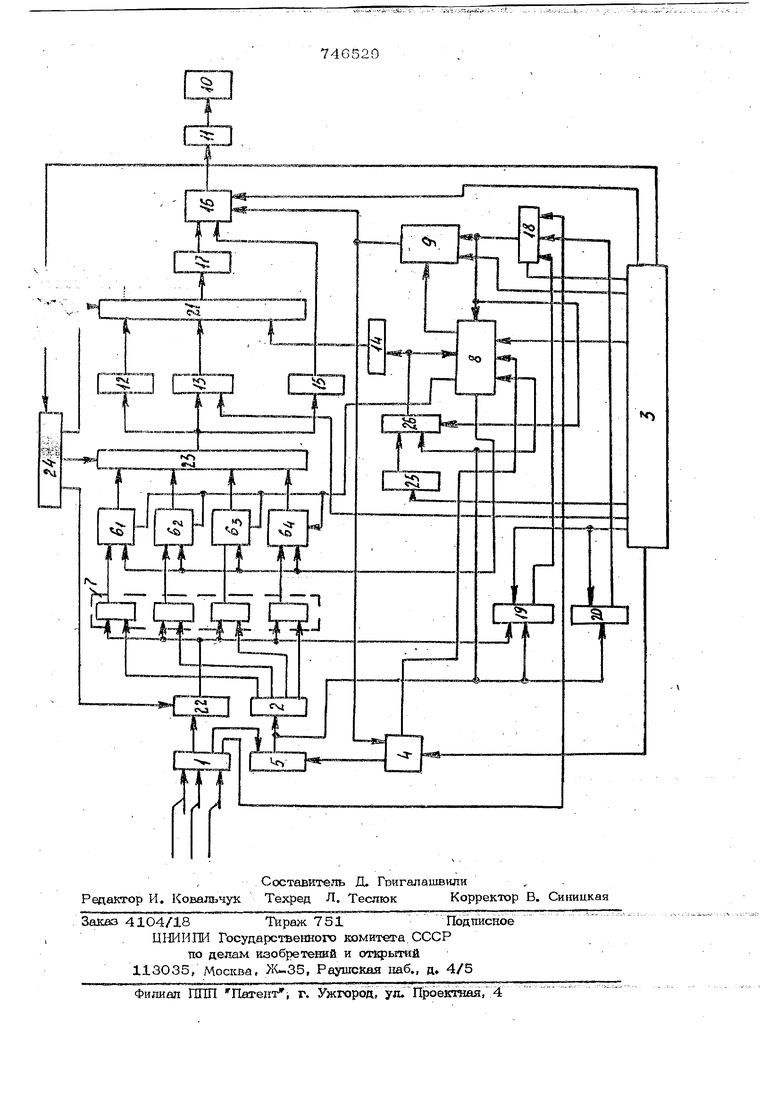

Изобретение относится к вычиспительной технике и может быть использовано для поиска неисправностей и ошибок в аппаратах и программных средствах алект ровного цифровотх) оборудования. Известно устройств, содержащее входной регистр, память, блок отображения, гешратор, схему сравнения, блок задерж« W Производительность известного устройства недостаточна. Наиболее близким к предлагаемому является устройство,, содержащее генератор, входной регистр, выход которого соединен с входами памяти, управляющий вход которой соединен с выходом блока управления йамятью, схему сравнения, блок задержки, кодовые преобразователи, блок отображения, индикатор знаков, блок управления индикацией 2 . Недостатком известного устройства является низкий коэффициент использования оборудования. Цель изобретения - повышение кЬэффициента использования оборудования. Поставпенйая цель достигается тем, что в устройство для анализа игфэрмадшонной последовательности, содержащее входной регистр, выходы которого соединены с информационными входами памяти, схему сравшния, блок задержки, блок , равления памятью, выходы которого соедн нены с первым и вторым управлякмдими входами памяти и первым входом блока управления индикацией, три кодовых преобразователя информации, генератор знаков, генератор вспомогательных импульсов, выход которого соединен с т ервым входом блока формирования временной диаграммы, выход которого соединён через узел управления блоком отображения с блоком отобрахсения, блок свнхронизадии, первый вход которого соединен с первым выходом гешратора, введены два распределители, входной.коммутатор, выходной коммутатор; управляющий коммутатор, счетчик, блок задания начального адреса, блок запуска, блок задания pejKmvioB, Коммутатор, тфичем входы первого распределите/ш являются входами устройства, первый выход растгредепителя через входной ко гмутатор соединен с первой группой входов входного регистра и первым входом схемы сравнения, второй выход первого рйспределителя соединен со вторым входом блока синхронизации, выхОд которого соединен с первыми входами блока аадёрлски, блока задания начального адреса, блока управления памятью, вторым входом схемы сравнения и входом второго распределителя, выходы которого соедиЕю-. ны со второй группой выходов входного регистра, выходы памяти через выходной коммутатор соединеда с входами первого КОДОВ.ОГО преобразователя и генератора встюмогательных импульсов и первым вхо дом второго кодового преобразователя, вы ходы первого, второго и третьего КОда-. вых преобразователей через последователь но соединенные коммутатор и генератор знаков с оединены со вторым входом -блока формирования временной диаграммы, трети вход которого соединен с выходом блока управления индикадии и вторым входом ге нератора, выход которого соединен со вто рым входом блока управления памятью, третий вход которого соединен с вьгходом блока запуска, вторыми входами блоков управления индикацией и задания начально го адреса, выход которого соединен с чет вертым входом управления памятью и входом третьего кодового преобразователя, выход блока задержки соединен с первым входом блока запуска, второй вход которого соединен с выходом схемы сравнения, третий выход первого распределителя соединен с третьим входом блока запуска выходы управляющего коммутатора соединены с управляющими входами колшутатора, входного и выходного коммутаторов, выход счетчика соединен с третьим входо блока задания начального адреса, выходы блойа задания режимов соедийёнй С соот« ветствуквдими входами блока управления памятью, блока запуска блока упраЬйейия ивдикад.ией, счетчика, ут1равл51Ю1цеГо KOI мутатора, блока формирования временной диаграммы, геввратора, схемы сравнения, блока задержки, второго кодового преобразователя. ЬлоКг-схема устройства присведена на чертеже.;.„, .„ Устрсйстао содержит распределители 1,2, блок 3 задания режимов, генератор 4, .блок 5 синхроннзадви, память 6 ходной регистр 7, блок 8 управления памятью, блок 9 управления индикацией, блок 10 отображения, узел 11 управления блоком отобрахсения, кодовые преобразова телн информации, герератор 15 вспомогательных импульсов, блок Ifci ормирования временной диаграммы, генератор 17 знаков, блок 18 запуска, схему 19 сравнения, блок 20 задержки, кол глутатор 21, входной 1юммутатор 22, выходной коммутатор 23, управляющий коммутатор 24, счетчик 25, блок 26 задания начального адреса. Устройство работает следующим обра зом, Устройство работает в двух основных режимах: анализу лопгческих состояний н анализа логических временных соотношений. В каждом режиме 1гмеется возможность анализировать обласаъ данных до прихода пускового си1гВвла, после прихода пускового сигнала или в районе пускового сигнала. В каждом режиме имеется возможность наблюдать временные диаграммы, а также двоичную и восьмиричную или двоичную и шестнадцатиричную информации, эквивалентные желаемому исследуемому слову из области данных, В общем случае работа устройства разделяется на два этапа: на ггервом этапе происходит выборка информации, а на втором - отображение этой информации на экране блока 10.. Рассмотрим работу ycTpolteiBa ва первом этапе при авализо вдестнадцат иразряддых слов в- первом режиме, т.е. при анализе логических временных состояний. При проверке шестнадцатиричного обо рудования информация через распределитель 1, вхорной коммутатор 22 и входной регистр 7 подается в память 6, . Генератор 4 в этом случае не функцио нирует и поэтому работа устройства син- гсронизируется с помощью внешнего (про веряемого) синхросигнала. Это означает, что на выходе блока 5 имеются импульсы внешнего синхросигнала. После этого работа устройства управляется блоком 18. Имеютс я следующие способы aatiycKa устройства. Внешний запуск. При этом погявлвние сигнала на соответствутощем входе уст ройства через растфеделитель 1 вызывает срабатывание блока 18. Ручной зат|уск. В этом случае оператор с помощью блока 3 вызывает срабатывание блока 18. Запуск по ключевому слову. В этом случае в блоке 3 набирается какое-либо ключевое слово. Это слово поступает в схему 19, куда также постукает входная информация через распределитель 1 и входной коммутатор 22, При сравнении срабатывает блок 18. Запуск по количеству сиюфоимпульсов или тактов. В этом случае в блоке 3 3i даетхгя количество тактов. Эта информаци задерживается в блоке 2О, После прихода аадандаго числа си хрокмпульсов срабаты вает блок 18. Все эти способы залтусгш увеличивают ги,бкость и эффестквЕюсть шюкска ненсправ ностей, так как имеется возможность ис- адшдовать любые промежутки работы объек та или любой участок программы. Во входном регистре 22 информация задерживается на время, необходимое для записи В память 6 Синхроимпульсы поступайэт также в блок 26, содержимое которого поступает в блок 8, где выра тывается текущий адрес памяти . После форми рования импульса пуска на выходе блока 18 счет импульсов в блоке 25 и выработ ка адресатов is блоке 8 прекращается и управление передается блоку 9, Если требуется исследование области данных после пускового сигнала, то в этом сдучае запнсь в память начинается после прихода пускового сигиала до заполнения памяти. В блоке 25 счета «мцульсов в этом случае вовсе не происходит, а это означает, что начальный адрес, который соо-гаетствует пусковому сигналу, опрюделяется нулевой ячейкой памяти G.. Посв бяоке 8 ле эйполнения паг-яти 6 Бырабатывается сагнал, по которому упpaвлe шe передае1ся блоку 9, А если требуется исследовать область данных в раионе пускового сигнала , то в этом случае тоже осуществляется непрерывная запись и счет синхроимпульсов в памяти и в блоке 25. После прихода пускового сигнала из блока 18 счет импульсов в блоке 25 прекращается, этим обеспечивается сохранение начального йдреса памяти Q - , соответствующего приходу пускового сиг нала, а запись в память продолжается Таким образом, в памяти 6 ,. остается. 64 слова до прихода пускового сигнала, и: 64 слова после него н обеспечивается, таким образом, возможность исс юдивать слова, окружающие пусковой сигнал, в качестве коториого может быть какоэ- ибо ключевое слово, определенное количеством тактов с начала работы устройства, какой-либо единичный сигнал .

образом, что оно разделяется на две части по разрядности, 6 и 6 составляют одну часть, а 6 и 6, - вторую. .

При откларке программы возможность логического анализатора запускаться по нулсному ключевому слову, по количеству тактов или по какому- ибо единичному сигналу и возможность исследовать ойласть данных до прихода пускового сигт апа, а также в окружентг или после него, кроме того возмоншость отображения информации в удобной для оператора форпроверяемого объекта или рунной сипгал оператора. Рассмотрим работу устройства на втором этапе. Выработка импульсов, управляющих лучом в блоке 10, осуществляется в бло ке 11. После осуществления выборки ин формации и соответственно записи этой информации в память 6, . , управление передается блоку 9. В зависимости от режима выборки информации (до, средний, после), который задается блоком 3 по сигналам блоков 8 и 18, в блоке 9 определяется момент Начала индикации в блоке 1О. После определения этого момента на выходе блока 9 вырабатывается сигнал, который запускает генератор 4, импульсы которого поступают в блок 8. Сюда же поступает информация о началь- ном адресе памяти 6, соответствующем пусковому сигналу от блока 25. По этому начальному адресу считывается первое слово и затем восемнадцать слов, посдюдующих этому слову. Темп считывания информации задается генератором 4. В каждом кадре повторяется один цикл считывания информации из памяти 6,, с начального адреса. Считанная информация через выходной коммутатор 23 подается на кодовые преобразователи 12-14 и на блок 15. Информгщия из кодовых преобразоватэлей 12-14 подается через коммутатор 21 на генератор 17. Опр геление тех разверток, в которых требуется размацение знаковой информации, а также отобажение вспомогательных импульсов осуествляется в блоке 16. При работе с восьмиразрядЕпым и четыехразрядным цифровым оборудованием абота известиотх) устройства не эффектива, так КйК в первом случае 1/2 часть и о втором случае 3/4 части объема ЗУ е используются. В предлагаемом устройтве при работе с восьмиразрядным оборуованием работа ЗУ организуется таким Me, обеспечивает исследование любого участка программы. Длительность отлад.ки программ уменьшается примерно в три раза, но это не является пределом, Орие Е1тировочный экономический эффект от применения логического анализатора составит примерно 80 тыс, руб, в год. Формула изобретения Устройство для анализа информациовьной последовательности, содержащее входной регистр, выходы которого соединены с информационными входами памяти, схе му сравнения, блок задергкки, блок управления памятью, выходы которого соединены с первым и вторым управляющими входами памяти и первым входом блока управления индикацией, три кодовых преобразователя информации, генератор аНаков, генератор вспомогательных импульсов, вы ход которого соединен с первым входом блока формирования временной диаграммы выход которого соединен через узел увравлеНия блоком отображения с блоком отображения, блок синхронизации, первый вход которого соединен с первым выходом генератора, отличающееся тем что, с целью повышения коэффициента ис- пользования оборудования, в него введены два распределителя, входной коммутатор, выходной коммутатор, управляющий комму татор, счетчик, блок задания начального адреса, бпок запуска, блок задания режи мов, коммутатор, причем входы первого распределителя являются входами устройства, первый выход распределителя через входной коммутатор соединены с первой груттаой входов входного регистра и первым входом схемы сравнения, второй выход первого распределителя соединен со вторым входом блока синхронизации, выход которого соединен в первыми-входами блока задержки, блоке, задания начального адреса, блока управления памятью, вторы входом схз1ъа 1 сравнения 0 входом второг распределителя, выходы которого соедине ны со второй группой выходов входного регистра, выходы памяти через выходной коммутатор соединены с входами первого кодового преобразователя и генератора вспомогательных импульсов и первым входом второго кодовош преобразователя, выходы первого, второго и третьего кодовых преобразователей через пос;юдова тельно соединенные коммутатор и генератор знаков соединены со вторым вхо- дом блока формирования временной диаграммы , третий вход которого соединен с выходом блока управления индикации и вторым входом генератора, выход которого соединен со вторым входом блока yttравления памятью, третий вход которого соединен с выходом блока запуска, вторыми входами блоков управления индикацией и задания начального адреса, выход которого соединен с четвертым входом управления памятью и входом третьего кодового преобразователя, выход блока задержки соединен с первым входом бдока запуска, второй вход которого соединен с выходом схемы сравнения, выход первого распределителя соединен с третьим входом блока г апуска, выходы управляющего коммутатора соединены с управляющими входами коммутатора входного я выходного коммутаторов, выход счетчйка соединен с третьим входом блока задания начального ащзеса, выходы блока задания режимЬв соединены с соответствукицими входами блока управления памятью, блока запуска, блока управления индикацией, счетчика, утеравляющегх) коммутатора, блока формирования временной диаграммы, генератора, схемы сравнения, блока задержки, второго кодового преобразователя, Источнюоа информации, принятые во внимание при экспертизе 1.ЗШ Тгсип9action Dnsirunnents апсэ( MeaCs .1975,т, 24, М 4, , 353-366. 2,Авторское свидетельство СССР до заявке М 2596308/24, 27.03,78,

Авторы

Даты

1980-07-05—Публикация

1978-04-04—Подача