(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ

СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU726561A2 |

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU726560A1 |

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU720465A2 |

| Устройство для передачи и приема дискретных сигналов | 1975 |

|

SU557403A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для защиты от ошибок в системе передачи с решающей обратной связью | 1976 |

|

SU728153A1 |

| Устройство для декодирования двоичного кода | 1984 |

|

SU1220128A1 |

| Устройство для защиты от ошибокВ СиСТЕМЕ пЕРЕдАчи C РЕшАющЕйОбРАТНОй СВязью | 1978 |

|

SU809306A2 |

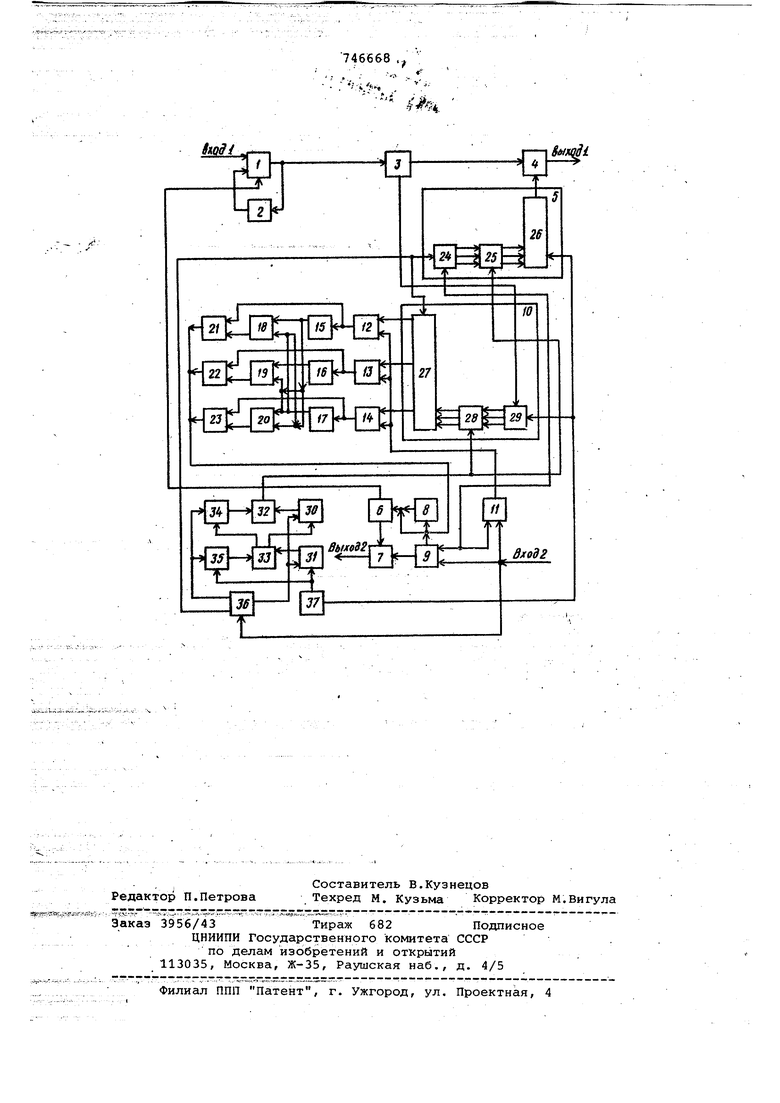

ЙзобЬетение относится к технике передачи дискретных сигналов, предназначено для повышения достовернос ти передачи дискретной информации по дуплексным каналам связи в условиях воздействия помех. ilo основному авт. свид. №557403 известно устройство для передачи и приема дискретных сигналов, содержащее переключатель, первый вход которого подключен к первому входу устройства, выход соединен с входом кодирующего блока и входом первого накопителя - повторителя, выход которого подключен ко второму входу переключателя, первый выход кодирующего блока соединен с в:«одом первого блока сложения, выход которого подключен к первому выходу устройства, ; второй вход кодирующего блока соединен с входом первого элемента задерж ки, второй вход устройства подключен к первому входу второго блока сложения и к входу декодирующего блока, первый выход которого соединен с пер вым входом второго накопителя - повторителя, второй выход - с вторым входом второго блока сложения и через второй элемент задержки - с вторым входом первого блока сложения. третий выход - с первым входом и выходом элемента памяти и входом счетчика, первый выход которого соединен с вторым входом элемента памяти, второй выход - с вторым входом второго накопителя-повторителя, выход которого подключен к второму выходу устройства, а третий выход счетчика соединен с третьим входом переключателя , первые входы каждого блока сравнения подключены к соответствующим выходам первого элемента задержки, вторые входы объединены и соединены с выходом второго блока сложения, выход каждого блока сравнения подключен к входу соответствующего регистра и к первому входу соответствующего элемента управления, выход каждого регистра соединен с входами блоков памяти, йыход каждого блока памяти подключен к второму входу соответствующего элемента управления, выходы элементов управления объединены и ссЗединены с третьим выходом декодирующего блока 1. Устройство обладает недостаточно высокой надежностью и осуществляет помехозащищенную передачу и прием дискретных сигналов лишь при условии согласования величины задержки сигнаЛОВ в первом элементе задержки с величиной аппаратурных и каналбных запаздываний в прохождении сигналов по прямому и обратному каналам связи Целью изобретения является повыше нне н адезкности устройства. Поставленная цель достигается тем что в устройство.введены элемент ИЛИ элементы И, триггер, хронизатор передачи и хрониэ тор приема, вход которого соединен с канальным входом устройства, первый и второй выходы хронизатора приема соединены соответ ственно с первыми входами первоговторого элементов И и третьего-четве того элементбв И, первый выход хронизатора передачи соединен с вторыми входамивторого и четвертого элементов И, выходал которых соединены с входами Триггера, выходы триггера подключены к вторым входам первого и третьего элементов И, выходы кото рыхсоединены с входами эле;мента ИЛИ первый и второй элементы задержки выполнены в виде последовательно соёхда ненных входного регистра, блока элементов И и выходного регистра входы входных регистров соединены с входами элементов задержки, выходы выходных регистров подключены к выходам элементов задержки, управляющие входы блока элементов И подключены к выходу элемента ИЛИ, тактоBrie йходы входного регистра первого элемента задержки и выходного регистра второго элемента задержки соединены с вторым выходом хронизатор передачи, тактовые входы выходного р5ёшетра первого элемента задержки и входного регистра второго элемента задержки соединены с третьим выходом хронизатора приема. На чертеже изображено предлагаемое устройство. Устройство содержит переключател 1, первый накопитель-повторитель 2, кодирующий блок 3, первый блок 4 сложения, второй элемент задержки 5, счетчик 6, второй накопительповторитель 7, элемент 8 памяти, де кодир ующий блок 9, первый элемент 10 задержки, второй блок 11 сложени блрк 12-14 сравнения, регистры 15блоки 18-20 памяти, элементы 21-23 управления; элемент 5 задержки состоит из входного регистра 24, блока элементов И 25, выходногорегистра .лемент 10 задержки состоит из выходного регистра 27, блока элемен тов И 28, входного регистра 29. В состав устройства также входят -первый элемент И 30, второй элемент И 31, элемент ИЛИ 32, триггер 33, третий элемент И 3-4, четвертый элемент И 35, хронизатор 36 приема и Хронизатор 37 передачи. Устройство работает следугопфим об разом. По сигналам,поступающим с канального входа 2, хронизатор 36 приема определяет границы кодовых комбинаций на приеме и за каждую кодовую комбинацию выдает: по третьему выходу - последовательность импульсов тактовой частоты для продвижения проверочных символов во входном регистре 24 второго элементу задержки 5 и выходном регистре 27 первого элемента задержки 10, по первому и второму выходам - управляющие сигналы с цикловой частотой, которые сдвинуты по отношению друг к fspyry на время, не меньшее времени вывода Проверочных символов иэ декодирующего блока 9, и не совпадающие с моментом их вывода. Хронизатор 37 передачи опр1еделяет границы кодовых комбинаций на передачи и за каждую кодовую комбинацию выдает: со второго выхода - после- . довательностьтактовых импульсов для продвижения проверочных символов во входном регистре 29 первого элемента задержки 10 и выходном регистре 26 второго элемента задержки 5, с пер-. вого выхода - управляющий сигнал, перекрывающий по длительности последовательность тактовых и тульсов со второго выхода хронизатора передачи. На выходах четвертого элемента И 35 и второго элемента И 31 сигнал появляется в случае совпадения управляющего сигнала с хронизатора передачи, поступающего на их вторые входы, и соответствующих управляющих сигналов с хронизатора приема, поступающих на их первые входы. Выходные сигналы элементов И 31 и 35 управляют триггером 33, выходы которого подключены к первому элементу И 30 и третьему элементу И 34 таким образом, что при наличии сигнала на выходе элемента И 35 разреша- . ющий сигнал с триггера поступает на вход 2 элемента И 30, а при наличии сигнала на выходе элемента И 31 - разрешающий сигнал поступит на вход 2 третьего элемента И 34. В результате этого на выходе одного из элементов И 34 или 30 будет присутствовать сигнал, совпадающий с тем из двух управляющих сигналов хронизатора приема, который в данный момент не совпадает с управляющим сигналом хронизатора передачи. Через элемент ИЛИ 32 этот сигнал поступает на вторые входы блоков элементов Ипервого и второго элементов задержки, т.е. на управляющие входы блоков-элементов И будет поступать сигнал на каждую кодовую комбинацию, не совпадающий с моментами поступления проверочных символов как с кодирующего, так и с декодирующего блоков. На параллельные входы блоков И периодически поступают проверочные символы с входнйх регистров, соответственно первого и второго элементов задержки. Смена проверочных символов во вхо ных регистрах происходит, соответственно в первом элементе задержки моменты поступления проверочных сим волов с кодируквдего узла, во втором элементе згщержки - в моменты вывод проверочных символов из декодирующег устройства. Между моментами ввода и вывода проверочные символы хранятся во вход ных регистрах и происходит их перез пись в выходные регистры. Вывод проверочных символов из выходного регистра 26 второго элемент задержки происходит в моменты йывода проверочных символов из кодирующего блока 3. Вывод проверочных символов из выходного регистра 27 первого элемента задержки происходит в моменты поступления проверочных символов из декддирующего блока 9. При смещении выходных сигналов. хронизаторов приема и передачи друг относительно друга сигнал хронизатора приема, по которому осуществляется перезапись проверочных символов, входит в зону управляющего сигнала хронизатора передачи, при этом проис ходит Срабатывание триггера и перезапись контрольных символов будет осуществляться другим сигналом хронизатора приема. . В этом случае возможно изменение временных отношений в пределах после довательности кодовых комбинаций и будет подключен другой отвод первого Элемента задержки. Пусть, например, в устройстве используется код (п,к) с длиной кодошой комбинации п двоичных символов при п-к проверочных символах. При таком коде основное устройство будет иметь большую нерабочую зону, которая составляет-- -ifl- от длительности цикла, В предлагаемом устройстве нерабочая, зона в фазовом состоянии между циклами передачи исключена, а переключение емкости элементов задержки из-за изменения фазового .состояния между циклами передачи и приема, приводящее к переводу устройства в режим запроса, определяемое относительной величиной стабильности задаю щих генераторов и запаздывания сигналов связи, будет происходить достаточно редко. Таким образом, в предлагаемом устройстве значительно реже появляется необходимость перевода устройства в режим запроса при определенных фазовых соотношениях между циклами передачи и приема и тем самым повышена надежность связи. Формула изобретения Устройство для передачи и приема дискретных сигналов по авт, свид. №557403, отличающееся тем, что, с целью повышения надежности устройства, в него введены элемент ИЛИ, элементы И, триггер, хронизатор передачи .и хронизатор лриема, вход которого соединен с канальным входом устройства, первый и второй выходы хронизатора приема соединены соответственно с первыми входами первого-второго элементов И и третьего-четвертого элементов И, первый выход хронизатора переда и соединен с вторыми входами второго и четвертого элементов И, выхода которых соединены с входами триггера, выходы триггера подключены к вторым входам первого и третьего элементов И, выхода которых соединены с входами элемента ИЛИ, первый и второй элементы задержки выполнены в виде последовательно соединенных входного регистра, блока элементов И и выходного регистра, входы.входных регистров соединены с входами элементов задержки, выходы выходных регистров, подключены к выходам элементов задержки , управля ощие входы блока элементов И подключены к выходу элемента ИЛИ, тактовые входы входного регистра первого элемента задержки и выходного регистра второго элемента задержки соединены с вторым выходом хронизатора передачи, тактовые входы выходного регистра первого элемента задержки и входного регистра второго элемента задержки соединены с третьим выходом хронизатора приема. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №557403, кл. G 08 С 19/28, 13.10.75 (прототип) ;.

hoSi

ж . ii,,

4-/«4

Авторы

Даты

1980-07-05—Публикация

1978-02-13—Подача