... : 1 Изобретение относится к вьгаиспитепь-ной технике, в частности, к запоминающим устройствам (ЗУ) электронных вььчислитепьных машин (ЭВМ). Известно оперативное запоминающее устройство типа 2,5fl/2W, содержащее накопитель, соответствующие кходы которого подключены к выходам адресных и разрядных коммутаторов тока . Недостатки известного устройства большое потребление по питанию и малое бьгстродействие. Наиболее близким техническим решением к данному изобретению является запоминающее устройство типа 2Д/2 , содержащее накопитель, коммутаторы адреснык токов, выходы которык соединены с соответствующими аходами накопителя, вькоды которого соединены с соответству ющими входами коммутаторов разрядных токов, вькод каждого из которык соединен со входом усилителя считывания и ге нератора тока записи Х1 Недостатками известного устройства является то, что при увеличении его емкости резко увеличивается количество электронного оборудования как в адресном, так и в разрядном устройствах. Б разрядном устройстве на каждыедве разрядные линии свой усилитель считывания и два геHepiaTopa тока. Считанные сигнш1ы единицы двухполярные, что существенно затрудняет дискриминацию сигналов, устройство работает без разрушения информации при считьшании информации. Целью настоящего изобретения является расширение функциональных возможностей за счет считьтания информации без ее разрушения. Указанная цель достигается тем, что устройство содержит генераторы тока смешения по количеству разрядов накопителя, при этом аход каждого генератора тока смещения соединен с вькодоМ соответствующего коммутатора разрядного тока.

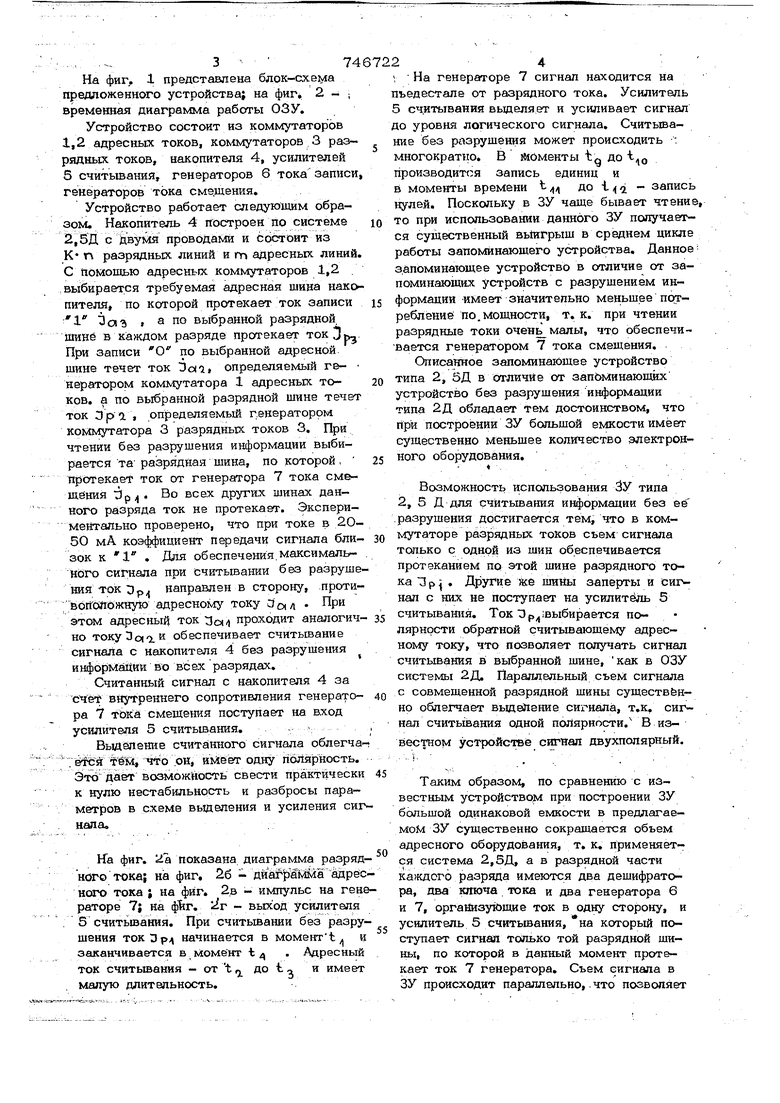

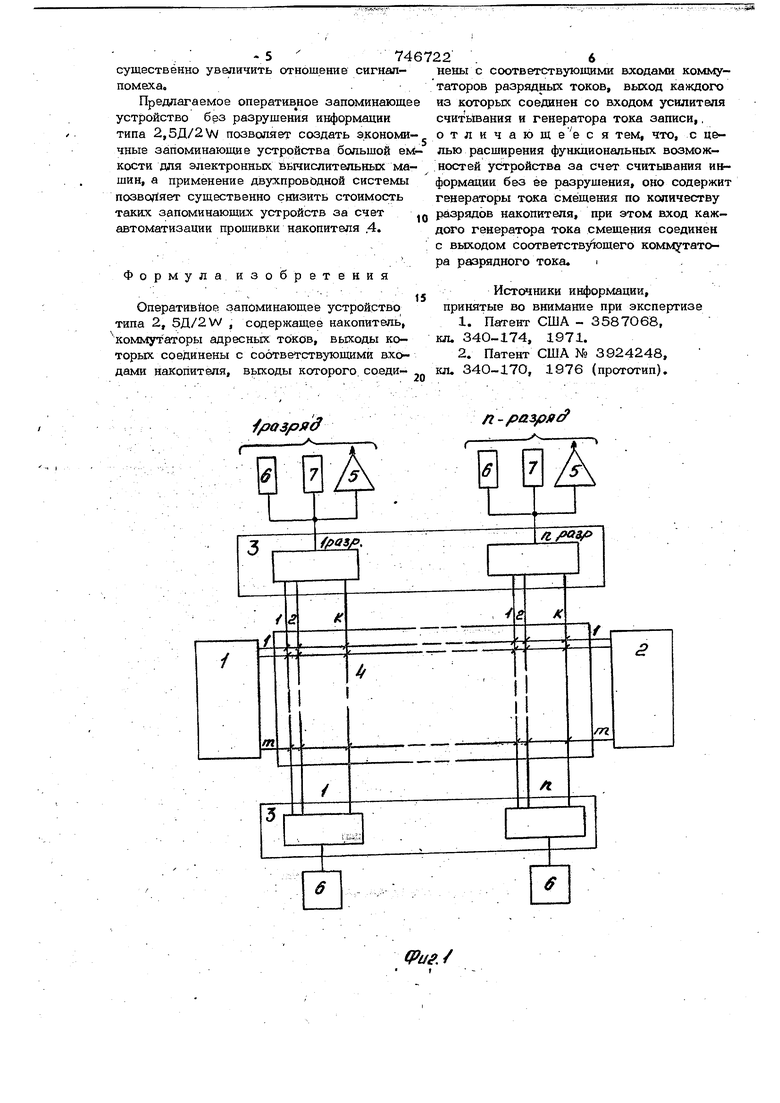

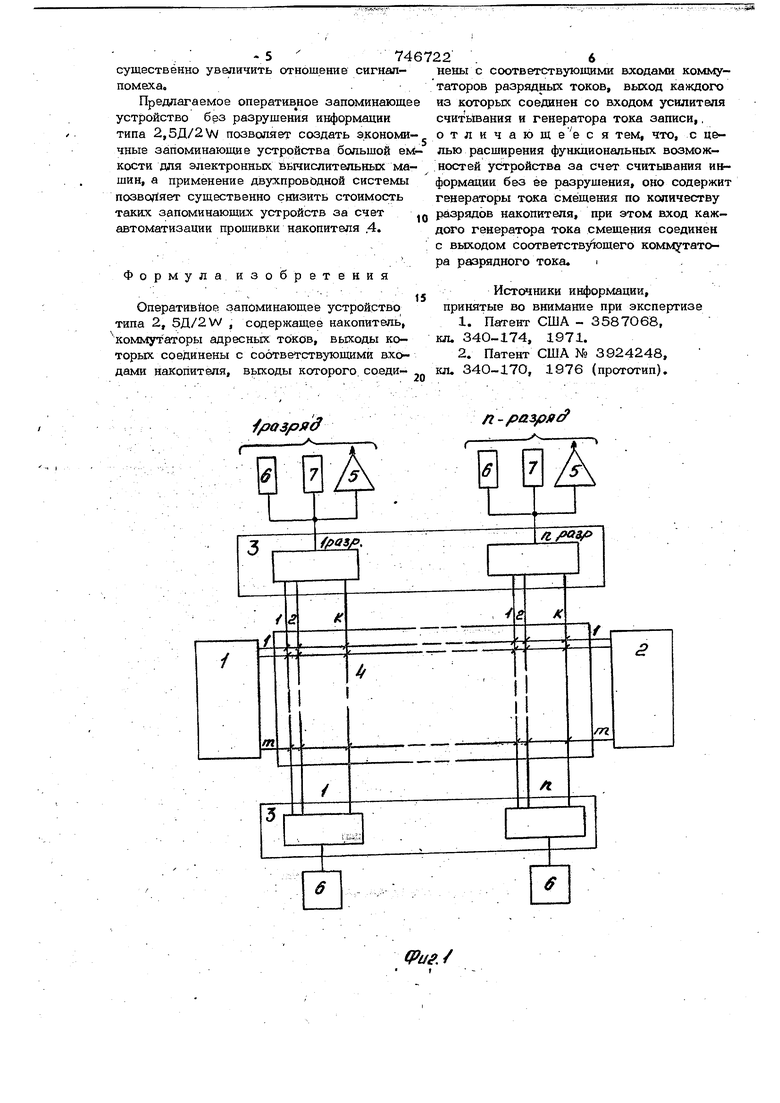

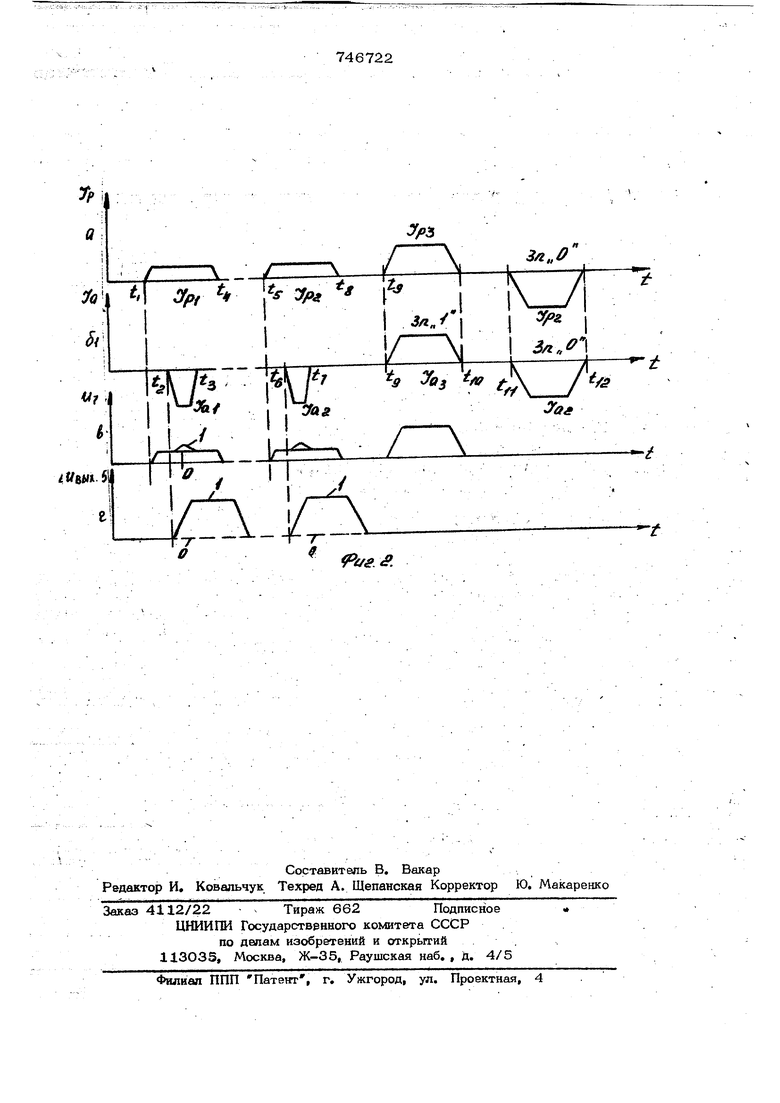

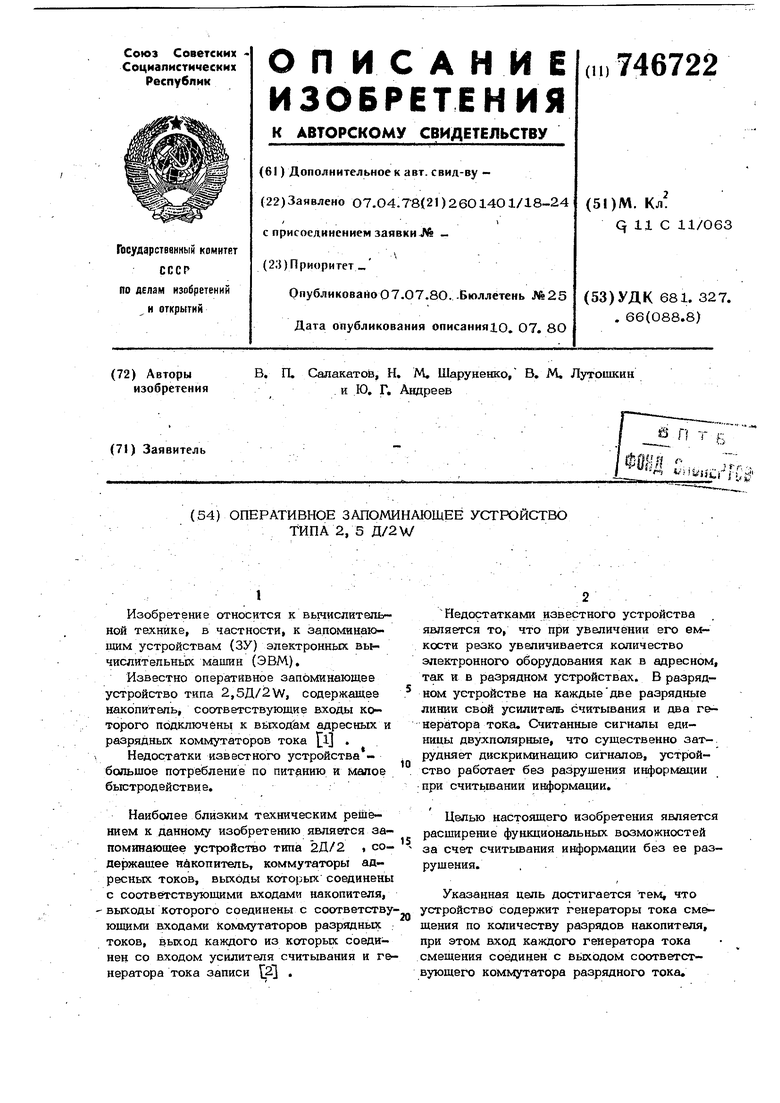

На фиг, 1 представлена блок-схэгла предложенного устройства; на фиг 2 - ; временная диаграмма работы ОЗУ.

Устройство состоит из коммутаторов 1,2 адресных токов, коммутаторов 3 разрядных токов, накопителя 4, усилителей 5 считьюания, генераторов 6 тока записи, генераторов тока сме.щения.

Устройство работает следующим образом. Накопитель 4 построен по системе 2,5Д, с 1а,вумя проводами и состоит из К п разрядных линий и m адресных линий. С помощью адресных коммутаторов 1,2 , выбирается требуемая адресная шина накопителя, по которой протекает ток записи Зсиэ , а по выбранной разрядной. ШиНё в каждом разряде протекает При Записи О по выбранной адресной, шине течет ток , определяемый ге- нератором коммутатора 1 адресных токов, а по выбранной разрядной шине течет ток Эра . определяемый г.енератором коммутатора 3 разрядных, токов 3, При чтении без разрушения информации выбираетсятаразрядйая щина, по которой, UpoTeKaet ток от генератора 7 тока смещбния Эр;, . Во всех других шинах данного разряда ток не протекает. Экспериментально проверено, что при токе в 2О50 мА коэффициент передачи сигнала близок к . Лля обеспечения.максималького сигнала при считьтании без разрушения ток о р направлен в сторону, протиуьопсйОЖйую адресному току Зсхл Ри этом адресный ток з0,1 проходит анапогично току 301 а обеспечивает считывание сигнала с накопителя 4 без разрушения инфб{)Мации во всах разрядах.

Считанный сигнал с накопителя 4 за счёт внутреннего сопротивления генерато- ра 7 ТОКИ смешения поступает на вход усилителя 5 считывания. . ... ,.

Выделение считанного сигнала облегча. ётСй WSI, он, имеет одну полярность. возможность свести практически к нулю нестабильность и разбросы параметров в схеме выделения и усиления сигнала.

На фиг. iia показана диаграмма разрядноге тока; т фиг, 26 - дйаграмйа адресного тока ; на фиг. 2.в - импульс на генераторе 7; на фТ1г. - выход усилителя . 5 считьша1ния. При считьшании без разрушения токЭр; начинается в моментЧ, и заканчивается в момент t/, . Адресный ток считьтания - от t ,j 3 имеет малую длительность.

V На генераторе 7 сигнал находится на пьедестале от разрядного тока. Усилитель 5 считывания вьщеляет и усиливает сигнал до уровня логического сигнала. Считьюание без разрушения может происходить : многократно. В моменты tg до производится запись единиц и в моменты времени t /| до i /j - запис нулей. Поскольку в ЗУ чаще бывает чтени то при использовании данного ЗУ получается существенный вьшгрыш в среднем цикл работы запоминающего устройства. Данно запоминающее устройство в отличие от запоминающих устройств с разрушением информации -имеет значительно меньшее потребление по, мощности, т. к. при чтении разрядные токи очень малы, что обеспечи-вается генератором 7 тока смешения.

Описанное запоминающее устройство типа 2, 5Д в отличие от запоминающих устройство без разрушения информации типа 2Д обладает Тем достоинством, что при построении ЗУ большой емкости имеет существенно меньшее количество электронного оборудования.

.. . . .

Возможность использования ЗУ типа 2, S Д для считьтания информации без ее .разрушения достигается тем, что в коммутаторе разрядных токов съем сигнала только с одной из шин обеспечивается протеканием по этой шине разрядного тока 3 р . Другие иге шиНы заперты и сигнал с Ш1Х не поступает на усилитель 5 считывания. Ток ТЭр шыбирается полярности обратной считывающему адресному току, что позволяет получать сигнал считывания в выбранной шине, как в ОЗУ системы 2Д. Параллельный съем сигнала с совмещенной разрядной шины существенно облегчает выделение сигнала, т.к. сигнал считывания одной полярности. В известном устройстве сигнал двухполярный,

).

Таким образом, по сравнению с известным устройством при построении ЗУ большой одинаковой емкости в предлагаемом ЗУ существенно сокращается объем адресного оборудования, т. к. применяется система 2,5Д, а в разрядной части ка кдог6 разряда имеются два дешифратора, два ключа тока и два генератора 6 и 7, организующие ток в одну сторону, и усилитель 5 считьюания, на который поступает сигнал только той разрядной шины, по которой в данный момент протекает ток 7 генератора. Съем сигнала в ЗУ происходит параллельно, что позволяет 74 существенно увеличить отношение сигналпомаха.отношение сигнал.с.гг.::г 4-типа 2,5fl/2 w позволяет создать экономичные запоминающие устройства большой ем кости для электронных ьычислительных машин, а применение двухпроводной Системы позво 1яет существенно снизить стоимость таких запоминающи.х устройств за счет автоматизации прошивки накопителя .4. Формула изобретения Оперативное запоминающее устройство типа 2, 5n/2W , содержащее накопитель, коммутаторы адресных тсжов, выходы которых соединены с соответствующими вхо J . O.VV дами накопителя, вьгкоды которого, соеди разря

П-разр е t « fui-T .йены с соответствующими входами комму - - - .- ч, --rt.wMVMl jl iUiUTE считьюания и генератора тока записи,, отличающеес я тем, что, с целью расширения функциональных возможностей устройства за счет считывания информации без ее разрушения, оно содержит генераторы тока смещения по количеству разрядов накопителя, при этом вход каждого генератора тока смещения соединен с выходом соответствующего коммутатора разрядного тока. Источники информации, принятые во внимание при экспертизе 1.Патент США - 3587068, кл. 340-174, 1971. 2.Патент США № 3924248, . НаТеНТ ША№ «24248 л. 340-17О, 1976 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Запоминающее устройство типа 2,5 д | 1976 |

|

SU607278A1 |

| Программируемое постоянное запоминающее устройство | 1980 |

|

SU886055A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСГКО | 1970 |

|

SU273284A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Полупостоянное запоминающее устройство | 1982 |

|

SU1049976A1 |

| Запоминающее устройство | 1971 |

|

SU479151A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 :1 Т ВФОН]] Я-И;ф'РТГЩ <" t- J J^^ '^ • i .• f S .„ J i, is i* | 1972 |

|

SU433541A1 |

(PufJ

Авторы

Даты

1980-07-05—Публикация

1978-04-07—Подача