1049976J

Изобретение относится к вычислитель-Поставленная цель достигается тем,

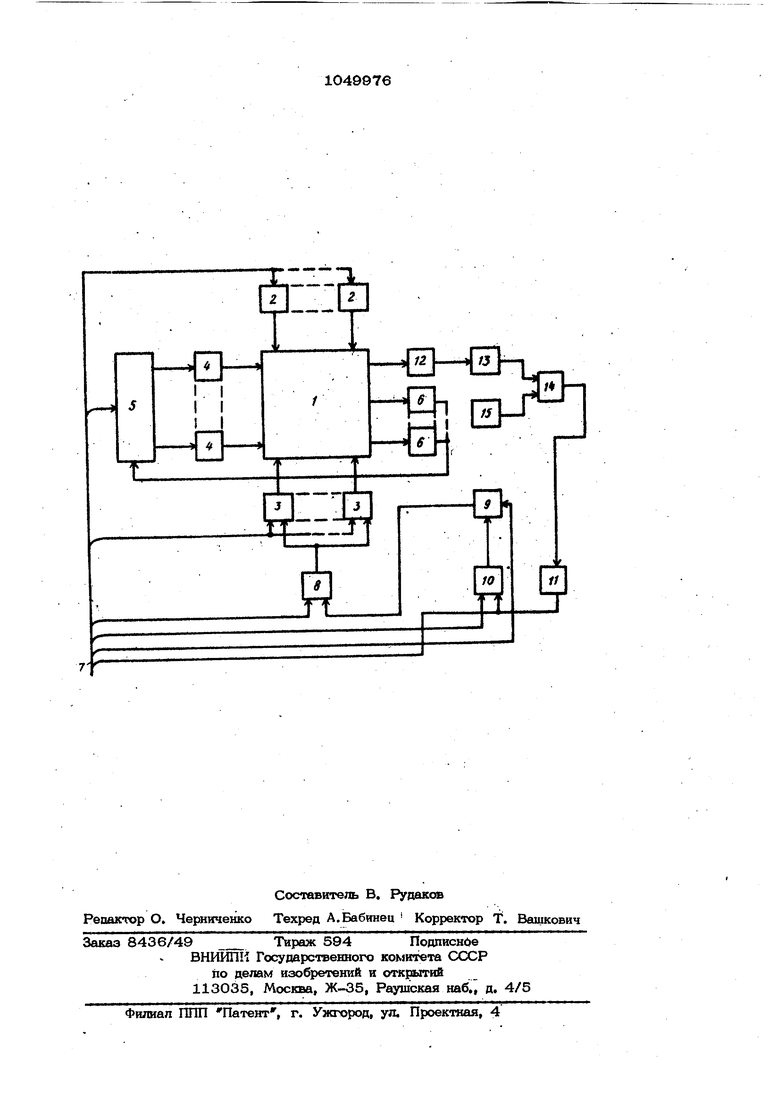

ной технике и предназначено для исполь что в полупостоянное зшюминаюшее уст эования в цифровых вычислительных машиг ройство, содержащее наксятитель, входы нах с повышенными требованиями к быстро- которого подключегал к выходам формиродействию в качестве устройства хранения эалисн и считъюания сменной информации. Известно полупостоянное запоминающее устройство, содержащее накоп:г: ль на Многоотверстных ферритовых элеме1ета формирователи линейных токов записи и считывания, числовой регистр, соединена ный с выходами усилителей считывания, подключенных к раэряпно-считывающим линиям наксшителя l . Недостатком этого устройства является то, что в нем не предусмотрено повышение быстродействия при считывании при одновременном сохранении высокой информационной надежности за счет считьшания после предварительного разрушения. Наиболее близким к изобретению по технической сущности является полупос то5шное запоминающее устройство, содер жащее накопитель, выполненный на эле ментах типа микробиакс, формирователи линейных токов и считъшания, усилители считывания, подключенные к числовой части накопителя 21 . Недостатком известного полупостоянного запоминающего устройства с электри ческой сменой информации является отсут ствие возможности подготовки числовых . линеек накопителя для считывания непосредственно после записи в них информации. Подготовка числовых линеек в таком устройстве может осуществляться с помощью разрушения только непосредственно перед счИтьтанием для получения стабильных импу;1ьсов сигнала чтения, что необходимо для создания оптимальньхх режимов работы усилителей считывания. Учитывая то, что в больщинстве случаев одна и та же информация считъгоается многократно и что к быстродействию записи информации в подобных устройствах предъявляются значительно меньшие, требования (информация может быть записа1Ш только однажды), такая организация устройств, т,е, устройств без разрушения после записи нецелесообразна, так как это можег привести не только к снижению быстродействия, но и к снижению общего быстродействия. Цель изобретения - повьш1ение быстродействия полупостоянного запоминающего устройства и его информационной надеж1их:ти при считывании, вателей числовых токов записи и считывания и к выходам формирователей разрядных токов записи, входы которых соединены с выходами регистра числа, одни из входов которого подключены к выходам усилителей считывания, входы которых подключены к одним из выходов накопителя, причем входы формирователей числовых токов, записи, оцни из входов фор мирователей числовых токов считывания и другие входы регистра числа являются одними из входов устройства, введены элемент ИЛИ, триггер, ключ, формирователь сигналов, элемент НЕ, сумматор, генератор импульсов и дополнительный усилитель считьтания, вход которого подключен к другому выходу накопителя, а выход через элемент НЕ соединен с первым входом сумматора, второй вход которого подключен к выходу генератора импульсов, а выход соединен со входом формирователя сигналов,. выход которого подключен к одному из входов триггера, вьисод которого соединен со входом ключа, выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с другими входами формирователей числовых токов считьтания, причем управляющий вход ключа, входь триггера и второй вход элементе ИЛИ являются другими входами, устройства. На чертеже изображена структурная схема полупостоя1шого запоминающего устройства. Устройство содержит накопитель 1, формирователи 2 числовых токов записи, формирователи 3 числовых токов считывания, формирователи 4 разрядных токе записи, .регистр 5 числа, усилители 6 считьгоания, входы 7 устройства, элемент ИЛИ 8, ключ 9, триггер 10, формирователь 11 сигналов, дополнительный усилитель 12 считывания, элемент НЕ 13, сумматор 14 и генератор 15 импульсов. Устройство работает следующим образом, В режиме записи по сигналу, поступившему на одиниз. входов 7, происходит анализ кода числа, предварительно запи санного в регистр 5, В зависимости от кода числа, т,е. от кода 1 или О, запускаются формиррватели положитель-. ных или отрицательных разрядных токов записи и по разрядно-считывающим линиям накопителя 1 протекают соответствую щие токн разрядной записи, которые аолжны начинаться по времени несколько раньше токов записи формирователей 2, а заканчиваться несколько позпнее их, что требует условие надежной записи информации. Таким образом, с некоторой задержкой во времени относительно запускаформирователей 4 запускается соответствующий формирователь 2, который вырабатывает разнополярные токи записи. В результате этого в накопи тель 1 по соответствующему адресу згшисы&ается необходимая информация, причём в контрольный разряд данного адреса Bce да записывается 1 После окончания записи запускается соответствующий фо1 мирователь 3. Запуск формирователя 3 осуществляется за счет того, что поступает управляющий сигнал на разрушение, который устанавливает триггер 10 в то положение, которое соответствует открытому ключу 9. С этого времени через ключ 9 тактовые импульсы поступают на элемент ИЛИ 8, а следовательно, и на запуск формирователей 3. За-счет этого происходит разрушение 1 в контрольном разряде данного адреса, а следовательно, и в каждом разряде числовой линейки. Этот процесс продолжается до тех пор, пока 1 в контрольном разряде не достигнет по амплитуде необходимой величины.

Тактовый импульс проходит через ключ 9 и запускает формирователь 3

до тех пор, пока проинвертированный сигнал чтения с усилителя 12 не достигнет

такой величины, которая по абсолютной величине станет меньше опорного импульса генератора 15. Если суммарный импульс напряжения достигает заранее установленного порога срабатывания формирователя 11, происходит формирование управляющего сигнала на выходе формировате ля 11, который поступает на выход устройства и служит сигналом конца рйзрушения. Этот же сигнал поступает на вход триггера 10, который опрокидывается в исходное состояние, ключ 9 закрывается, и тактовые импульсы далее не поступают через элемент ИЛИ 8 на запуск формирователя 3.

Режим считьшания в предлагаемом устройств;е протекает как в известном. По одному из входов 7 поступает управляющий сигнал на вход элемента ИЛИ 8. Сигнал с выхода элемента ИЛИ 8 запускает соответствующий формирователь 3, вырабатывается один однополярный ток считъгоания На усилители 6 поступают соответствующие сигналы чтения, которые после усиления подаются на регистр 5. Таким образом, время считывания не , включает в себя необходимое время paalA рушения, в течение которого усилители считывания должны быть- закрыты, а сигналы чтения не воспринимаются, что предотвращает вькод из нормальных режимов работы усилителей 6 считывания.

Технико-экономическое преимущество предлагаемого устройства по сравнению с известным, заключается в его более высоком быстродействии.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Полупостоянное запоминающее устройство | 1983 |

|

SU1108505A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Устройство для считывания информации из накопителя | 1980 |

|

SU864334A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU746733A1 |

ПОЛУПСХГГОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, входь которого подключены к выходам формирователей числовых токов записи и считывания к к выходам формирователей разрядных токов записи, входы которых соединены с выходами регистра числа, одни из входов которого подключены к выходам усилителей считывания, .входы которых подключены к одним из выходов накопителя, причем входы формиy:f -f f -.-.r,.,... -....:...Л, sg кля-L:-.-.. .,I iS .-. /11-- V.- - - оf - I SS.,; рователей числовых токов записи, одни из входов формирователей числовых токов считьтания и другие входы регистра числа являются одними из входов устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены элемент ИЛИ, триггер, ключ, формирователь сигналов, эяе мент НЕ, сумматор, генератор импульсов и дополнительный усилитель считывания, вход которого подключен к другому выходу накопителя, а выход через элемент НЕ соединен с первым входом сумматора, второй вход которого подключен к выхс ду генератора импульсов, а выход соедиi нен со входом формирователя сигналов, выход которого подключен к одному из (Л входов триггера, выход которого соединен со входом ключа, выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с другими входами формирователей числовых токов считьшания, причем управляющий вход ключа, входы триггера и второй вход элемента : ИЛИ являются другими входами устрой4 ства. СО со Од

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Петерс€ н М | |||

| Бортовая память на элементе микробиакс со считыванием без разрушения информации | |||

| Приспособление для независимой установки углов, в целях прицела, при стрельбе из орудий и пулеметов | 1925 |

|

SU2433A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-10-23—Публикация

1982-03-26—Подача