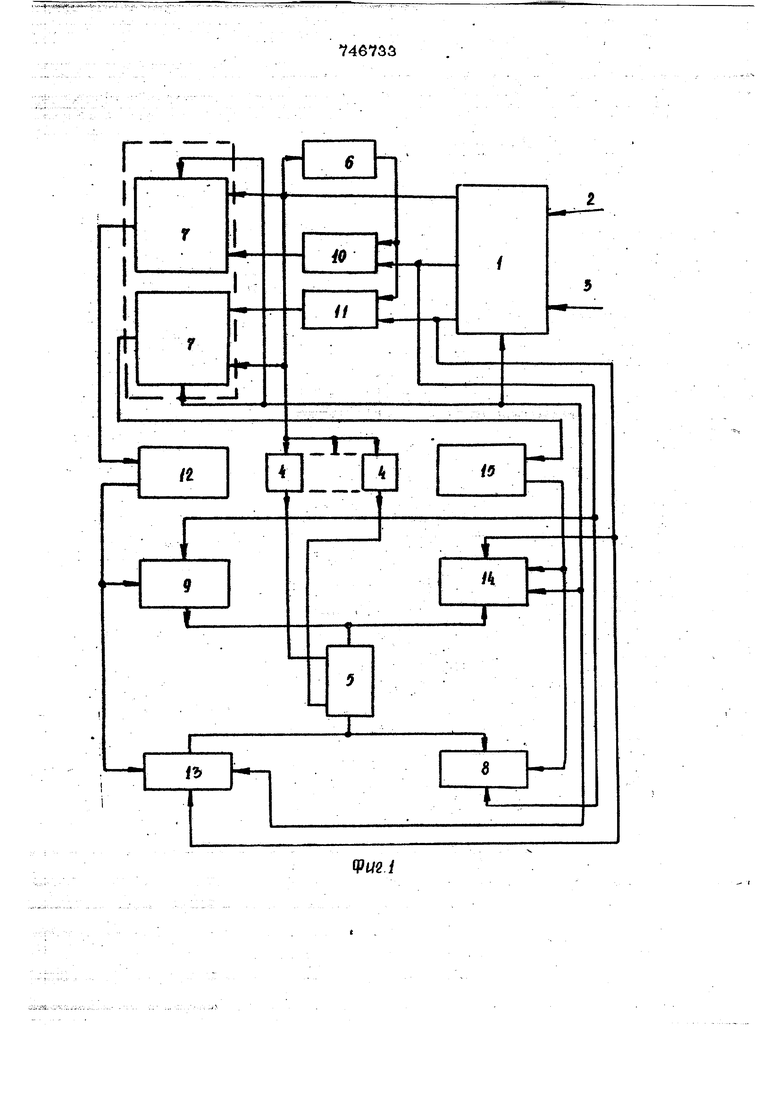

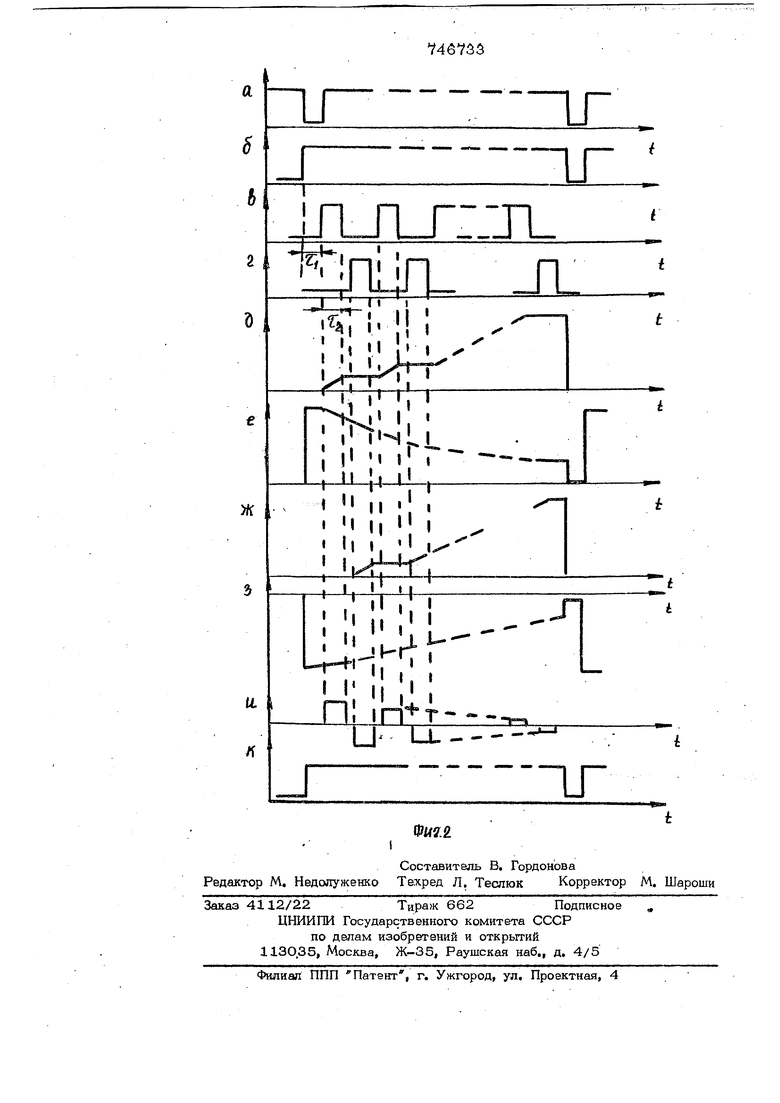

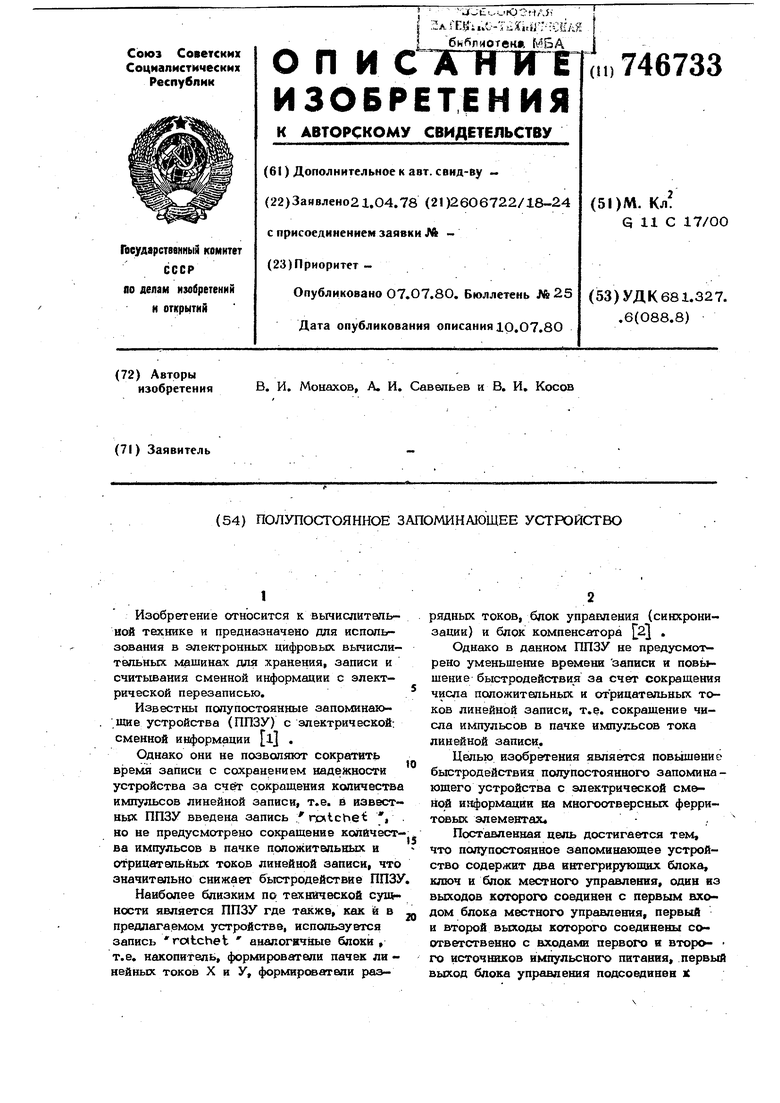

Изобретение относится к вычислительной технике и предназначено для использования в электронных цифровых вычислительных машинах для хранения, записи и считывания сменной информации с электрической перезаписью. Известны полу постоянные запоьО1нан щие устройства (ППЗУ) с электрической; сменной информации l . Однако они не позволяют сократить время записи с сохранением надежности устройства за счёт сокращения количества импульсов линейной записи, т.е. в известных ППЗУ введена запись ncntcbe / но не предусмотрено сокращение колйчества импульсов в пачке положительных в отрицательных токов линейной записи, что значительно снижает быстродействие ППЗУ Наиболее близким по тахнической сущности является ППЗУ где также, как и в предлагаемом устройстве, используется запись ratchet аналогичные блоки, т.е. накопитель, формирователи пачек ли нейных токов X н У, формирсюатвли разрядных токов, блок управления (синхронизации) и блок компенсатора 2 . Однако в данном ППЗУ не предусмотрено уменьшение времени записи и повььшение быстродействия за счет сокращения числа положительных и отрицательных токов линейной записи, т.е. сокращение числа импульсов в пачке импульсов тока линейной записи. Целью изобретения является повышение быстродействия полупостоянного запоминающего устройства с электрической см Н01Й информации аа многоотверсньсх ферритовых элементах -, Поставленная цель достигается тем, что попупостоянное запоминающее устройство содержит два интегрирующих блока, ключ и блок местного управления, один из выходов которого соединен с первым входом блока местного управления, первый и второй выходы которого соединены соответственно с входами первого и вторсн- ГО источников импульсного питания, первый выход блока управления подсоединен входам формировапгелей раэр5здных токов и к входу Шюча, выход к угорог к одним из входов интегрирующих блоков, второй вь№од блока управления подключен к вторг)1йсуш;бДУ первого интегрирующего блока, соединенного со вторьш входом блока местного управления, третий выход блока управления соединен со вторьпс входов второго интегрирующего блока, выход которого, подключен к третьему входу блока местногоуправления, а четвертый выход блока управления подключен к четвертому нходу блока местного упра влеНйя, к вторым входам формирователей отрицатель Hfeix линейньрс токов записи и считывания. На фиг. 1 представлена блок-схема полупостоянного запоминающего устройства} на фиг, 2 - временная диаграмма рабс ты ЗУ. Устройство содержит блок 1 управления, Соединенный с кодовыми шинами 2 Записи и с кодовыми шинами 3 считывани один из выходов блока 1 управления соединен с формирователями 4 разрядных токов, подсоединенных по вьгходам к разряднь1м шинам 5 накопителя, и ко входу ключа 6. Этот же выход блока 1 управления подключенк6 аходу блока 7 местного управления,, . , . Второй выход блока 1 управления соединен со входами формирователей 8 и 9 линейньЬс положительных токов записи и со входом интегрирующего блока 10, второй вход которого соединен со входом второго интегрирующего блока 11 и вьсхо- дом ключа 6, а выход интегрирующего блока 1О подключен ко входу блока 7 местного управления,подсоединенного к источнику 12 положительного импульсного питания. Выход источника 12 пблбжйтёльноГо импульсного питания подключен ко входам формирователей линейных положительных токов йаписи 8 и 9 и ко входу одного из формирователей 13 линейных отрицательных токов записи и считывания, Третий выход блока 1 управления соединен со входами формирователей 13 и 14 линейных отрицательных токов записи и считывания, со вторым входом интегрирующего устройства 11, подсоединенного кблоку 7 местного управления, выход которого подключен к источнику 15 отрицательного иммульсного питания, выход которого соединен со входами одного из формирователей линейных положительных токов записи 8 и входами форМирова тел;; 14 линейного отрицательного тока записи и считыван1га. 74 3 В режиме записи с кодовой щины 2 запиСи поступает сигнал а Запись (зп) на блок управления (фиг. 2). Блок управления вырабатывает на первом выходе управляющий сигнал б, который запускает формирователи разрядных токов и блок местного управления, с выхода которого подается управляющий сигнал на источник положительного импульсного питания и на источник отрицательного импульсного питания. Затем с некоторой задержкой относительно управляющего сигнала с первого выкода вырабатывается первый управляющий импульс на втором выходе блока управления в , с помощью которог о запускаются формирователи линейных положительных токов записи. Этот же импульс подается на интегрирующий блок 9. С выхода интегрирующего бпрка 9 подается соответствующий потенциал д на блок м&стного управления. Далее вырабатываете управляющий иМпульс на третьем выходе г , который запускает формирователи линейных отрицательных токов записи и считьюания и Поступает на вход второго интегрирующего блока 10. С выхода интегрирующего блока управляющий потенциал ж поступает на блок местного управл&ния, Далее поочередно вырабатьшаются управляющие сигналы на втором и третьем вьгхсдах блока управления для организации ratchet записи. При этом на интегрирующих блоках увеличиваются управляющие потенциальи За счет этого уменьшается напряжение с источника положительного импульсного питания е и с источника отрицательного импульсного питания з, что вызывает уменьшение линейных токов записи. Эти токи в конце цикла записи равны по амплитуде номинальнь1М и. Но, тек. Как в начале цикла записи линейные токи бьШи значительно больше номинальных, появилась возможность сократить цикл записи, не ухудшая надежность записи по сравнению С записью большим количеством импульсов при ratchet записи номинальными токами. В конце цикла записи, т.е. по окончании управляющего сигнала на первом выходе блока управления срабатьшает ключ, с помощью которого интегрирующие блоки устанавливаются в исходное состояние к . (фиг. 2).« Работа в режиме считывания предложенного устройства не отличается от .известных устройств. Считывание происходит одиночным линейным импульсом той же ;попярнсхли, что и последний импульс линейного тока записи в пачке импульсов rcHtchet записи. При а-эом с четвертого выхода блока управления по импульсу считьтание (сч), поступившему с. кодовой шины 3, подается управляющий сигнал на запуск формирователей Линейных отрицательвьгх токов записи и считывания и на блок местного управления, Таким образом, в предложенном устройстве за счет введения двух интегриру- юцщх блоков, блока местного управлени:я и ключа появляется возможность увеличения амплитуд токов линейной записи с по степенным снижением их амплитуд до номинальных, что дает возможность сократить количество импульсов линейных токов в пачке импульсов ratchet записи, а, следовательно, и уменьшить время записи, что увеличивает быстродействие устройства при запиби, не ухудшая его надежности за счет исключения недозаписи. Формула изобретения Полупостоянное запоми 1ающее устройство, содержащее накопитель, подключенньй к выходам формирователей разрядных токов и формирователей отрицательньк и положитепьньос линейных токов записи и считьшания, которых собоинень с соответствующими выходами блока управления, входы блока управления подключень1 л кодовым шинам записи и считывания, и источники импульсного питания, свя занные с формирователями отрицательных и положитапьоых линейных токов записи и считывания, о т л и ч а ю щ е е с я теь|, что, с целью повышения быстродействия устройства при записи ип|)ормаиии, оно содержит два интегрирующих блока, ключ и блок местного управления, один из выходов которого соединен с первым ахо|д6м блока местного управления, первый и второй выходы которого соеднйены соотВетственно с входами первого и в:торого источников импульсного питания, первый вь1Ход блока управления подсоединен к входам формировапгелей разрядных токов и к входу ключа, вьскод которого подключен к одним из входов интегрирующих блокс«, второй выход блока управления подключен к второму входу первогч} интегрирующего блока, соединенного со вторым входом блока местного управления, третий вход блока управления соединен со вторым В.ХОДОМ второго интегрирующего блока, выход которого подключен к тр&тьему входу блока местного управления, а четвертый выход блока управления подсс)едянен к четвертому входу блока местного управления, к вторым входам формирователей отрицательных линейных токов записи и считьюания. Источники информации, принятые во внимание при экспертизе 1, Шигин X Г. и Дерюгин А, А. Цифровые вычислительйь ю машины. М., Энергия, 1975, с. 221. 2 ППЗУ Бортовая память на элементе микробиакс со считыванием без разрушения информации. МРП СССР, перевод 2433 (прототип).

fftUQi

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупостоянное запоминающее устройство | 1977 |

|

SU693436A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

| Запоминающее устройство | 1979 |

|

SU826417A1 |

| Запоминающее устройство | 1979 |

|

SU858094A1 |

| Устройство для отображения информации | 1985 |

|

SU1328840A2 |

| Запоминающее устройство | 1978 |

|

SU765876A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-21—Подача