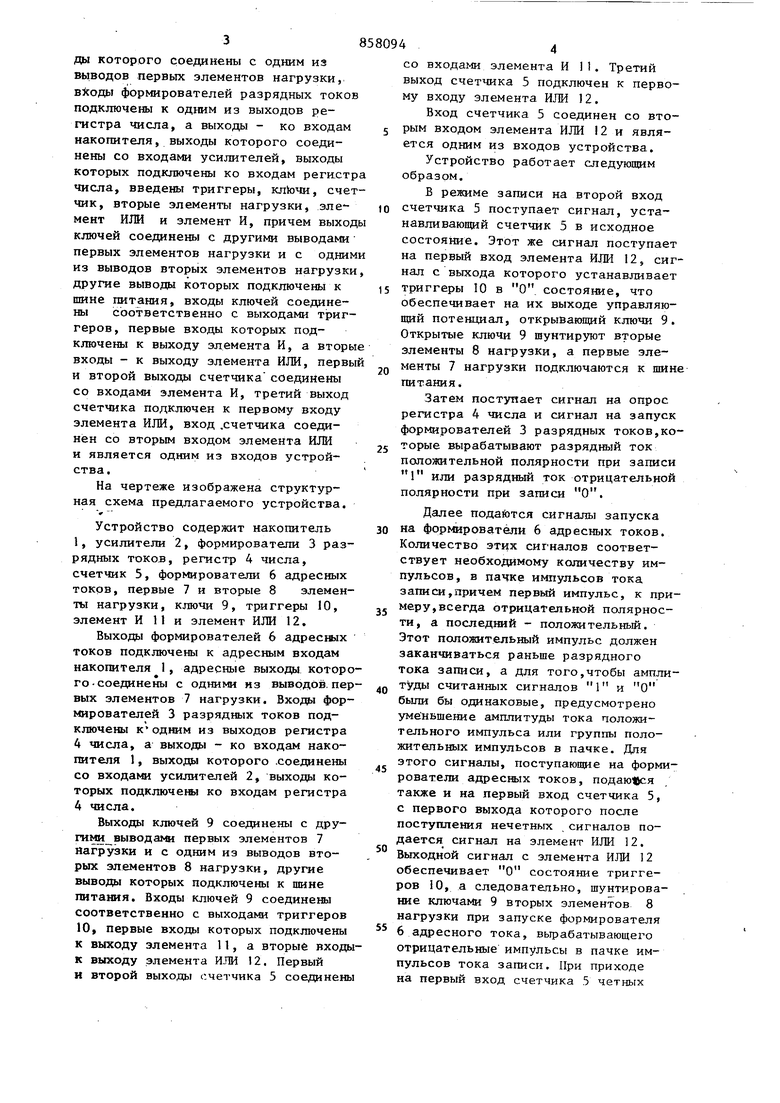

Изобретение относится к ющим устройствам. Известно запоминающее устройств содержащее накопитель, подключенны к формирователям разрядного тока за писи и к усилителям воспроизведения выходы которых подключены к пёрв1Л4 входам числового регистра, вторые входы которого подсоединены к кодов шине, а выходы - к первым входам формирователей разрядных токов записи, вторые входы которых подключены к кодовой шине, подсоединенной к формирователям адресных токов записи считывания, подключенным к концам адресных щрн .накопителя, другие концы которых подключены к нагрузочным элементам р . Недостатком этого устройства является низкая надежность. Наиболее близким техническим решением к данному изобретению является устройство, содержащее накопитель, разрядно-считывающие линии которого соединены с усилителями воспроизведения и с формирователями разрядного тока записи, подключенными к выходам числового регистра,вторые входы которого подключены к кодовым шинам, соединенным с формирователями адресных токов записи-считывания, выходы которых подключены к адресным шинам накопителя, соединенным с нагрузочными элементами Недостатком известного устройства является низкая надежность вследствие несимметричного перемагничивания запоминающих магнитных :: лементов при записи 1 и О. Цель изобретеиия - повышение надежности устройства. Поставленная цель достигается тем, что в запоминающее устройство,содержащее накопитель, усилители, формирователи разрядных токов, регистр числа и формирователи адресных токов, выходы которых подключены к адресным входам накопителя, адресные выходы которого соединены с одним кз вьшодов первых элементов нагрузки, входы формирователей разрядных токов подключены к одним из выходов регистра числа, а выходы - ко входам накопителя, выходы которого соединены со входами усилителей, выходы которых подключены ко входам регистр числа, введены триггеры, , счет чик, вторые элементы нагрузки, эле мент ИЛИ и элемент И, причем выход ключей соединены с другими выводами первых элементов нагрузки и с одним из выводов вторых элементов нагрузки другие выводы которых подключены к шине штания, входы ключей соединены соответственно с выходами Т риггеров, первые входы которых подключены к выходу элемента И, а вторы входы - к выходу элемента ИЛИ, первы и второй выходы счетчика соединены со входами элемента И, третий выход счетчика подключен к первому входу элемента ИЛИ, вход .счетчика соединен со вторым входом элемента ИЛИ и является одним из входов устройства. На чертеже изображена структурная схема предлагаемого устройства. Устройство содержит накопитель 1, усилители 2, формирователи 3 разрядных ТОКО.В, регистр 4 числа, счетчик 5, формирователи 6 адресных токов, первые 7 и вторые 8 элемен ты нагрузки, ключи 9, триггеры 10, элемент И 11 и элемент ИЛИ 12. Выхода формирователей 6 адрес1й 1х токов подключены к адресным входам накопителя 1, адресные выходы котор го -соединены с одними из выводов, пе вых элементов 7 нагрузки. Входы фор мирователей 3 разрядных токов подключены к одним из выходов регистра 4 числа, а выходы - ко входам накогштеля 1, выходы которого .соединены со входами усилителей 2, выходы которых подключешл ко входам регистра 4 числа. Выходы ключей 9 соединены с друГИ1 выводai№ первых элементов 7 Нагрузки и с одним из выводов вторых элементов 8 нагруэки, другие выводы которых подключены к шине питания. Входы ключей 9 соединены соответственно с выходами триггеров 10, первые входы которых подключены к выходу элемента 11, а вторые вход к выходу элемента И.ЛИ 12. Первый и второй выходы счетчика 5 соединен 4 со входами элемента И 11. Третий выход счетчика 5 подключен к первому входу элемента ИЛИ 12. Вход счетчика 5 соединен со вторым входом элемента ИЛИ 12 и является одним из входов устройства. Устройство работает следующим образом. В режиме записи на второй вход счетчика 5 поступает сигнал, устанавливающий счетчик 5 в исходное состояние. Этот же сигнал поступает на первый вход элемента ИДИ 12, сигнал с выхода которого устанавливает триггеры 10 в 0 состояние, что обеспечивает на их выходе управляющий потенциал, открывающий ключи 9. Открытые ключи 9 шунтируют вторые элементы 8 нагрузки, а первые элементы 7 нагрузки подключаются к шине питания. Затем поступает сигнал на опрос регистра 4 числа и сигнал на запуск формирователей 3 разрядных токов,которые вырабатывают разрядный ток положительной полярности при записи 1 или разрядный ток отрицательной полярности при записи О. Далее подаются сигналы запуска на формирователи 6 адресных токов. Количество этих сигналов соответствует необходимому количеству импульсов, в пачке импульсов тока записи,причем первый импульс, к примеру,всегда отрицательной полярности, а последний - положительный. Этот положительный импульс должен заканчиваться раньше разрядного тока записи, а для того,чтобы амплитуды считанных сигналов 1 и О были бы одинаковые, предусмотрено уменьшение амплитуды тока положительного импульса или группы положительных импульсов в пачке. Для этого сигналы, поступающие на формирователи адресных токов, подаю 1ся также и на первый вход счетчика 5, с первого выхода которого после поступления нечетных сигналов подается сигнал на элемент ИЖ 12. Выходной сигнал с элемента ИЛИ 12 обеспечивает О состояние триггеров 10, а следовательно, шунтирование ключами 9 вторых элементов 8 нагрузки при запуске формирователя 6 адресного тока, вырабатывающего отрицательные импульсы в пачке импульсов тока записи. При приходе на первый вход счетчика 5 четных 5 сигналов с его второго выхода подается управляющий сигнал на первый вход элемента И 11. Однако срабаты™ вание элемента И 11 по четному сигна лу запуска формирователей адресных токов 6 произойдет после прихода определенного их количества, сигнало со второго выхода счетчика 5, т.е. при поступлении управляющего сигнала на второй вход элемента И 11 с третьего выхода счетчика. В этом случае на выходе элемента И 1I вырабатывает ся управляющий сигнал, по которому триггеры 10 устанавливаются в 1 состояние, закрываются ключи 9, шунти- з рующие вторые элементы 8 нагрузки. Это приводит к уменьшению амплитуда последнего положительного импульса в пачке импульсов тока записи или амплитуд определенного наперед за- данного количества положительных им пульсов в пачке импульсов тока запи си за счет подключения к первым эле ментам 7 нагрузки вторых элементов 8 нагрузки. Таким образом, установленное чис уменьшенных амплитуд положительных импульсов из пачки импульсов записи обеспечивает одинаковое перемагничивание магнитных элементов накопителя 1 при записи 1 и. О, а тем самым сравнивает амплитуды считан1а1Х сигна лов 1 и Q в режиме считывания. Считывание происходит по сигналу, поступившему на формирователи 6 адресных токов.При этом опрос осуществляется одним отрицательным импульсо адресного тока считывания, а сигналы считывания поступают после усиления на усилителях 2 на входы числового регистра 4. Технико-эконоьическое преимуществ предлагаемого устройства заключается в том, что в результате применения Ключей и вторых элементов нагру ки, в нем обеспечивается одагнаковое перемагничивание магнитных элеменсигнапри записи тов в накопителе лов О и 1 и, выравни тем самым, и 1 сигналов О вание считанных значиза счет чего при считывании, тельно повышается надежность. 4 Формула изобретения SanoNoiHaK ee устройство, содержащее накопитель, усилители, формирователи разрядных токов, регистр числа и формирователи адресных токов, выходы Которых подключены к адресным входам накопителя, адресные выходы которого соединены с одними из вы-, водов первых элементов нагрузки,входы формирователей разрядных токов подключены к одним из выходов регистра числа, а выходы - ко входам накопителя, выходы которого подключены ко входам усилителей, выходы которыг соединены со входами регистра числа, отличающееся тем,что t целью повышения надежности устройства, оно содержит триггеры, ключи, счетчик, вторые элементы нагрузки, элемент ИЖ и элемент И, причем выходы ключей соединены с другими выводами первых элементов нагрузки и с одними из выводов вторых элементов нагрузки, другие выводы которых подключены к пине питания, входы ключей соединены соответственно с выходами триггеров, первые входы которялх подключеиь к выходу элемента И, а вторые входы к выходу элемента ИШ, первыйи второй выходы счетчика соеданены со входами элемента И, третий выход счетчика подключен к первому входу элемента ИЛИ, вход счетчика соединен со вторым входом элемента ШШ и является одним из входов устройства. ИСТОЧ1ШКИ информации, ринятые во внимание при экспертизе 1. А.М.Иванов и др. Вопросы потроения магнитно-электронных сменных локов ППЗУ с электрической записью информации на ферритовмх линейках. Тезисы . докладов конференции ЗУ-76. Тбилиси, 1976. 2. Петерсон М. Бортовая память на элементе микробиакс.со считыванием без разрушения информации.Перевод № 2433 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство | 1979 |

|

SU826417A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

Авторы

Даты

1981-08-23—Публикация

1979-11-20—Подача