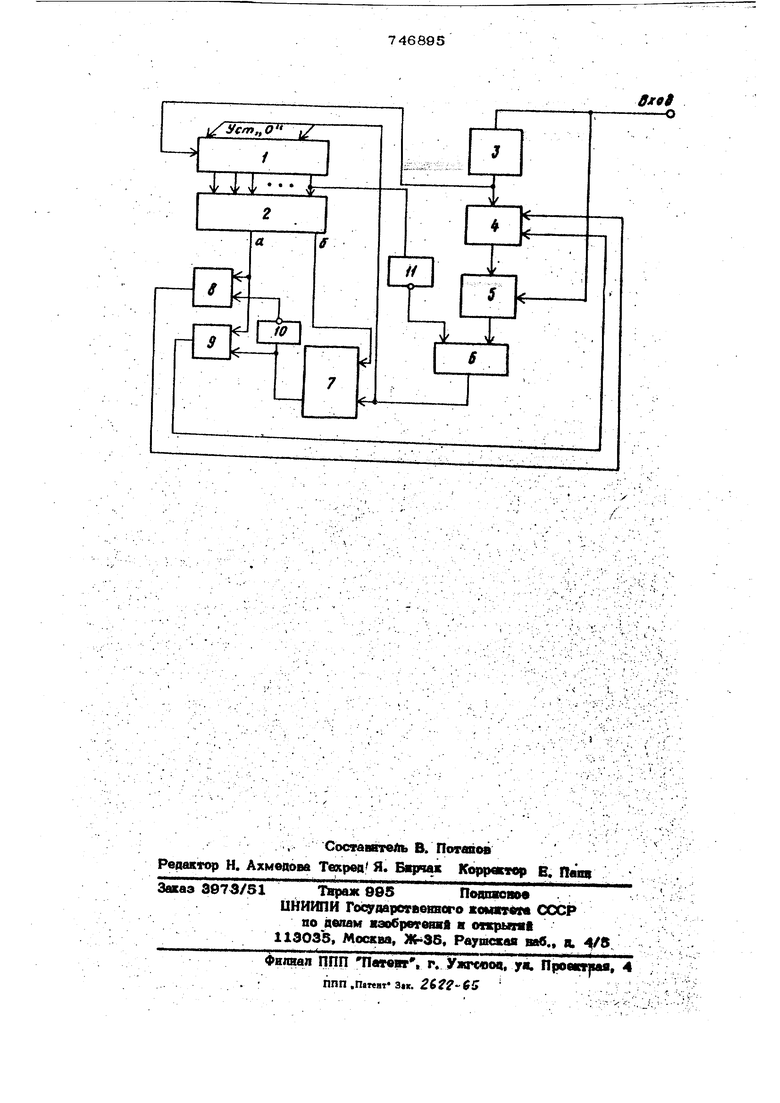

Изобретение относится к импульсной технике и может быть применено в конт рольно- Измерительной аппаратуре для . цифровых систем связи и вычислительной техники. . По основному а ВТ. св. № 598226 известно устройство для синхронизадии контрольного я эталонного цифровых сигналов, содержащее счетчик тактов, дешифратор, блсж выделения тактовой частоты, генератор эталонного сигвала; блок несовпадений, схемы запрета, триггер, два элемента совпадения я инвер тор. Недостатком устройства является то, что длительность цикла сравнения контрольной и эталонной пооледовательшх;тей импульсов не зависит от того, в каком такте цикла вь1Явлеяо первое несовпадение. Это обуславливает сравнительно бол шое время вхождения в синхронизм. Целью изобретеш я является уменьшение времени синхро шзации. Указанная цель достигается тем, ITO в устройство для синхровиэдции контроль ного и эталоннсяо цифровы сигналов, содержащее схему запрета, блок выделения тактовой частоты, вход которого лошслючен к шине ковтрольнсиго сигнала, первый выход блока выделения тактовой частоты соединен со входом Счетчвиса тактов, которсяО дешифратор подключены к первым входам первого я второго элементов совпадения, выход второго элемента совпадения соединен с первым вхо-; дом генератора эталонного сйгнатта, второй вход которого подключен к выходу блока выделения тактовой частоты, инвертор, триггер я блок несовпадений, выход которого соединен с niepBbtM входом схемы запрета,, второй вход которой подknsoHeH к последнему разряду счетчика тактов, а выход схемы запрета соединен с одним из входов триггера, другой вход которого подюоочен ко второму выходу деш11фратора, пртчем выход триггера соединен со вторым входом второго элеMW{№ Т;ЬШадбШя нёп6 средствейно и через инвертор со вторым входом первого элемента совпадения, выход которого под ключен к третьему входу генератора эталойНого сигнала, выход которого соединей с первым входом блока несовпадений, второй вход которого подключен к luHjfie контрольного сигнала, дополннтельновведен инвертор, включенный между выходом последнего разряда счетчика тактов и входом схемы запрета, а выход схемы запрета подключен ко входу установки в ноль счетчика TakToa Функциональная схема устройства приведена на чертеже и конструктивно содержит счетчик 1 тактов, дешифратор 2, блок 3 выделения тактовой частоты, генератор 4 эталонного сигнала, блок 5 несош1адений, схему 6 запрета, триггер 7, элементы 8 и 9 сбштадения и инверторы 10 а 11. Устройство работает следующим образом. . В блоке 5 несовпадений осуществляется поразрядное сравнение контрольнсво сигнала, поступающего на вход устройстба с линии, -и Эталонного сигнала, формируемого генератором 4, Выявленное носовйаденне фиксируется триггером 7 и устанавливает счетчик 1 в нулевое соо тояние, причем сигнал с выхода инвер-; тора 11 закрывает схему 6 зайрета, отключая т| пггер 7 от выхопа блока 5 н сош1аденв б ; Затем сигнал с выхода си дешифратора 2 считывается через элемен 9 лловпадення и поступает в схему гене ратора 4, осущейтвляя сдвиг эталонной последовательности на такт. По окончаНИИ счктыеашя |ростояния триггера 7 йа выходе б дешифратора 2 появляетсй им пульс, обнуляющий триггер, .подготавливая его к новому пикду синхрошзапия. При пбрШлючёнйнп х:леднего разряда 1 тактов b единичное Ьбстояние схема 6 запрета открывается, н начинается новый цикл синхронизации, повторяющийся до тех пор, пока за такт не будет зафиксировано несовпадений (ГА-количество разрядов счетчика). При отсутствий в течение тактов несовпадений триггер 7 остается обнуленным, и сигнал с выхода а дешифратора 2 через схему 8 совпадений поступает в схему генератора 4, фиксируя окончание процесса синхрстшзации. Последний (п -ый) разряд счетчика обеспечивает отключение триггера 7 от блока 5 несовпадений на время, необходимое ДЛЯ завершения переходных процессов вызванных сдвигом эталонной последовательнбсти на такт, а также позволяет разделить во времени фиксацшо несовпадений, их считывание и возвращение триггера в исходное состояние, необходимое для УСТОЙЧИВОЙ работы устройства. В известном устройстве цикл выявлевия несовпадений продолжается в течение 2 тактов и не з ависит от того, В| такте выявлено первое несовпадение. В данном устройстве цикл выявления несовпадений завершается при выявлении первого нёсоштадения. Таким образом, за счет уменьшения продолжительности цикла вьгавления несовпадений уменьшается общее вхождения в синхронизм. Формула изобрете|Н1ия Устройство для синхронизации ко.нтрольногЬ и эталонного цифровьа СИГНАЛОВ по авт.св. № 598226, о т ли чаю щ в 9, Си тем, что, с целью уменьшения временя синхроннзашга, в него дополш1тел1гво введен инвертор, включенный между выходом последнего разряда счетчика тактов В входом схемы: запрета, а выхоц схемы запрета подключен ко входу устаBOBicH в аЪйь счетчика тактов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1976 |

|

SU598226A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1977 |

|

SU668081A2 |

| Устройство для измерения проскальзываний цифровых сигналов | 1989 |

|

SU1674388A1 |

| Устройство для синхронизации импульсных последовательностей | 1977 |

|

SU748838A1 |

| Устройство синхронизации измерительных последовательностей | 1978 |

|

SU720766A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1979 |

|

SU999149A1 |

| Устройство для синхронизации измерительных последовательностей импульсов | 1978 |

|

SU688983A1 |

| Устройство для синхронизации импульсных последовательностей | 1979 |

|

SU1160551A2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

Авторы

Даты

1980-07-05—Публикация

1978-05-31—Подача