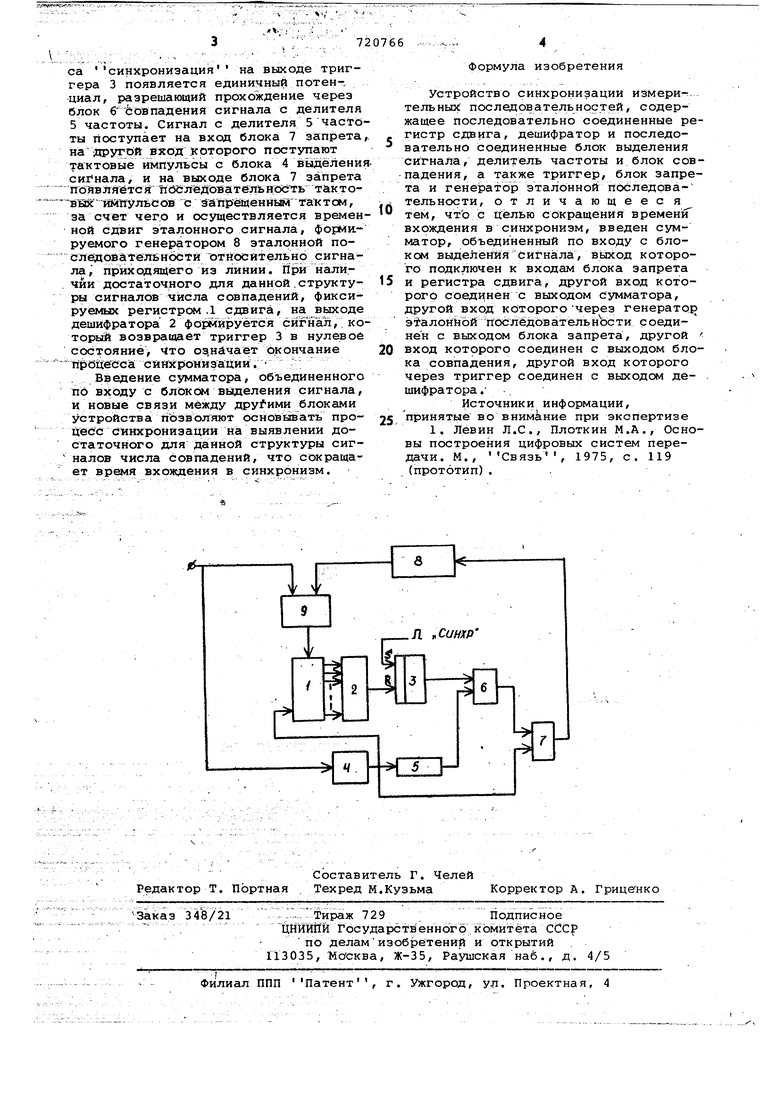

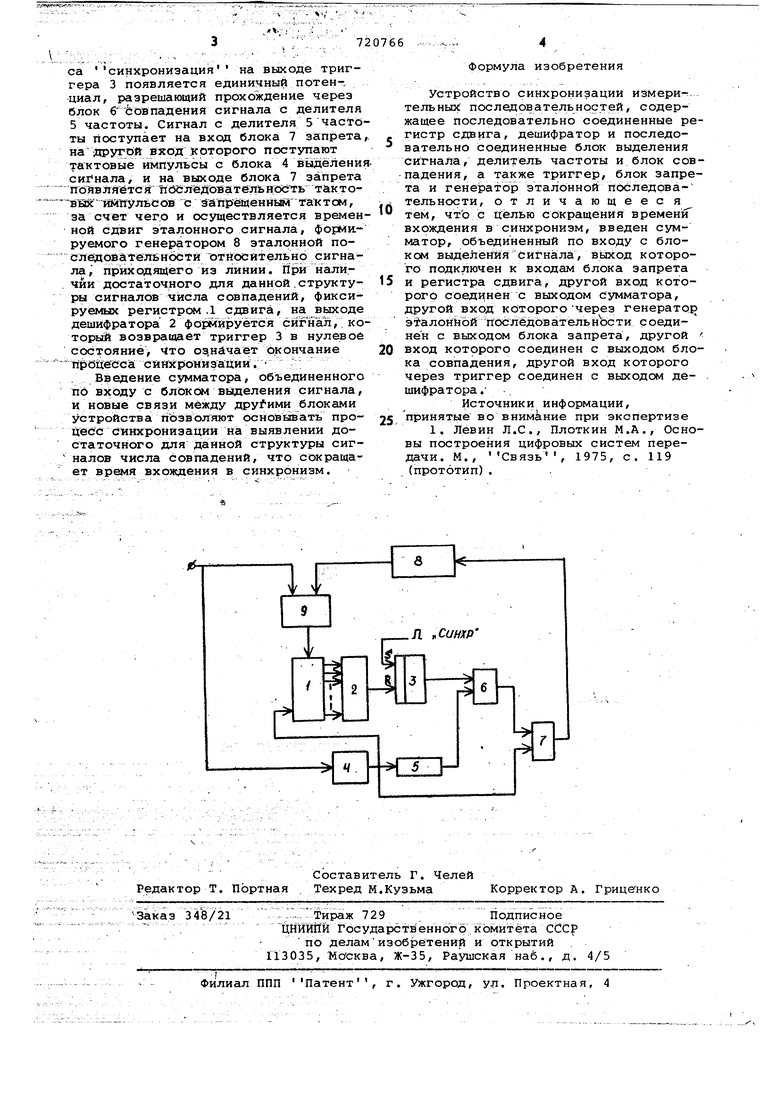

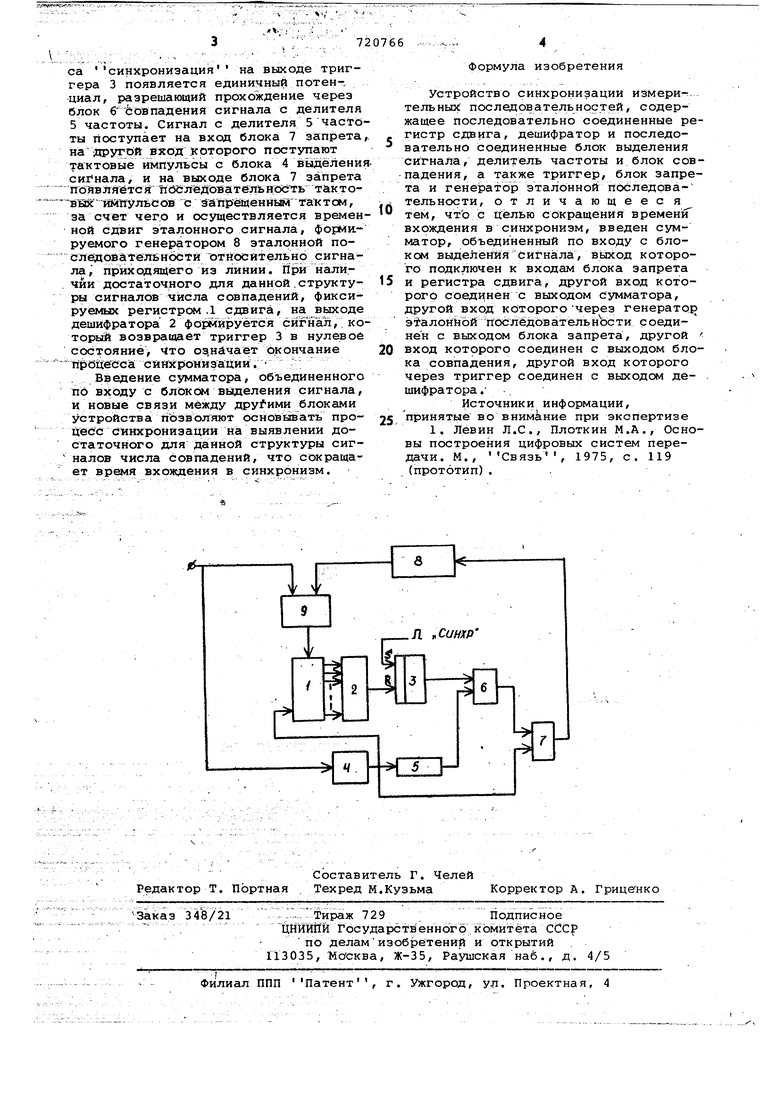

Изобретение относитея к системам связи с импульсно-кодсвой модуляцией и может использоваться при контроле линейных трактов цифровых систем передачи. Известно устройство синхронизации измерительных последовательностей, содержащее последовательно соединенные регистр сдвига, дешифратор и последовательно соединенные блок выделения сигнала, делитель частоты и блок совпадения, а также триггер, блок за грета и генератор эталонной последовательности 1. Однако известное устройство имеет значительное время вхождения в синхронизм. Цель изобретения - сокращение вре мени вхождения в синхронизм. Для этого в устройство синхрониза ции измерительных последовательносте содержащее последовательно соединенные регистр сдвига, дешифратор и rioследовательно соединенные блок выделения сигнала, делитель частоты и блок совпадения, а также триггер, блок запрета и генератор эталонной последовательности, введен сумматор, объединенный по входу с блоком выделения сигнала, выход которого подклю чен к входам блока запрета и регистра сдвига, другой вход которбго соединен с выходсм сумматора, другой вход которого через генератор эталонной последовательности соединён с выходом блока запрета, другой вход которого соединен с выходсял блока совпадения, другой вход которого через триггер соединен с выходом дешифратора. На чертеже представлена структурнай электрическая схема предложенного устройства. Схема устройства синхроц 1зации измерительных последовательностей содержит последовательно соединенные регистр 1 сдвига, дешифратор 2 и триггер 3, последовательно соединенные блок 4 выделения сигнала, делитель 5 частрты и блок 6 совпадения, блок 7 запрета, генератор 8 эталонной последовательности и сумматор 9. Устройство работает следующим обра зетл. В сумматоре 9 (по модулю два) осуществляется поразрядное сравнение . контрольного сигнала, приходящего из линии, и эталонного сигнала, формируемого генераторсм 8 эталонной последовательности. При поступлении на вход синхронизации триггера 3 импульса синхронизация на выходе триггера 3 появляется единичный потенциал, разрешающий прохождение через блок 6 Ьовпадения сигнала с делителя 5 частоты. Сигнал с делителя 5 частЬ ты поступает на вход блока 7 запрета на другой вход которого поступают тактовые импульсы с блока 4 выдёлени сигнала, и на выходе блока 7 за1прета пьявйяётсй 11белёдьвательнснгть такто вШ; ййпулбсов С аапрёгценный тактсм, за счет чего и осуществляется времен ной сдвиг эталонного сигнала, формируемого генератором 8 эталонной поеледовагёльнбстйтэтйосительно сигнала приходящего из линии. При наличии достаточного для данной.структуры сигналов числа совпадений, фиксируемых регистре .1 еда ига, на выходе дешифратора 2 формируется сигнал,, ко торый возвращает триггер 3 в нулевое состояние, что оз.начает окончание нрбЦёСса; сййХронизгаЦйи. : .Введение сумматора, объединенного п6 входу с блоксэм выделения сигнала, и новые связи между другими блоками устройства пЪэвблнют основывать процесс синхронизации на выявлении достаточного для данной структуры сигналов числа совпадений, что сокращает время вхождения в синхронизм. Формула изобретения Устройство синхронизации измерительных последовательностей, содержащее последовательно соединенные регистр сдвига, дешифратор и последовательно соединенные блок выделения си гнала, делитель частоты и блок совпадения, а также триггер, блок запрета и генератор эталонной пбследрвательности, отличающеес я тем, чтЪ с целью сокращения времени вхождения в синхронизм, введен сумматор, объединенный по входу с блоком выделения Сигнала, выход которого подключен к входам блока запрета и регистра сдвига, другой вход которого соединен с выходом сумматора, другой вход которого через генерато15 э алонй6й последовательнЪсти соединен с выходом блока запрета, другой вход которого соединен с выходом блока совпадения, другой вход которого через триггер соединен с выходом дешифратора . .. Источники информации, принятые во внимание при экспертизе 1, Левин Л.С., Плоткин М.А., Основы построения цифровых систем передачи. М., Связь 1975, с. 119 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1978 |

|

SU746895A1 |

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1979 |

|

SU999149A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1987 |

|

SU1510104A1 |

| Устройство синхронизации по циклам | 1983 |

|

SU1172053A1 |

| Устройство синхронизации М-последовательности | 1981 |

|

SU1053312A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство синхронизации с М-последовательностью | 1981 |

|

SU1003371A2 |

Авторы

Даты

1980-03-05—Публикация

1978-06-05—Подача