(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОНТРОЛЬНОГО и ЭТАЛОННОГО ЦИФРОВЫХ СИГНАЛОВ

частоты а также элемент НЕ, .RS-триггер и блок несовпадений, выход которого с первым входом элемента НЕТ, второй вход которого подключен к последнему разря у счетчика импульсов, а выход элемента НЕТ соединен с одним из входов RS-триггера, другой вход которого подключен ко второму выходу дешифратора, прячем выход RS-ipHrrepa соединен со вторым входом второго элемента И непосредственно и через элемент НЕ со вторым входом первого элемента И, выход которого подключен к третьему входу генератора этало шых сигналов, выход которого соединен с первым входом блока несовпаде1ШЙ, второй вход которого подключен к шине контрольного сигнала, введены последовательно соедкненньш счетчик несовпадений, дополнительный дешифратор и блок элементов ИЛИ, при этом выход элемента НЕТ подключен ко входу сче1чика несовпадений, другие входы кото; рого соединены с вторым входом дешифратора, а выход блока элементов ИЛИ соединен с одним из входов RS-триггера.

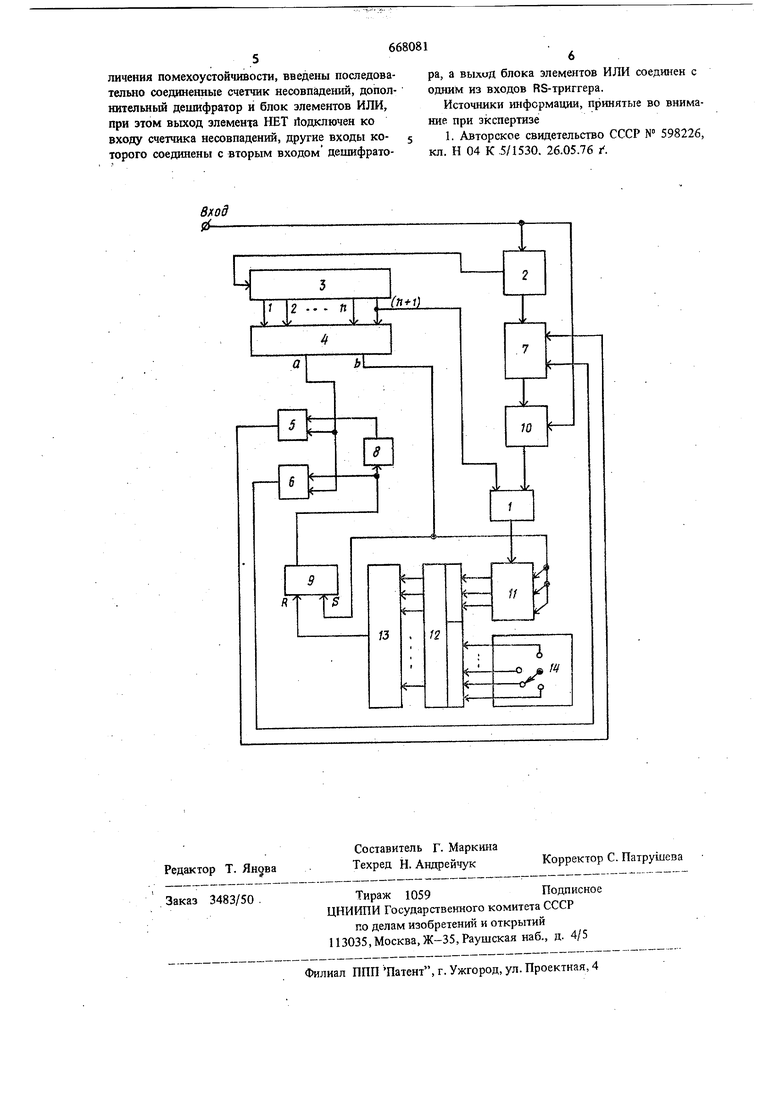

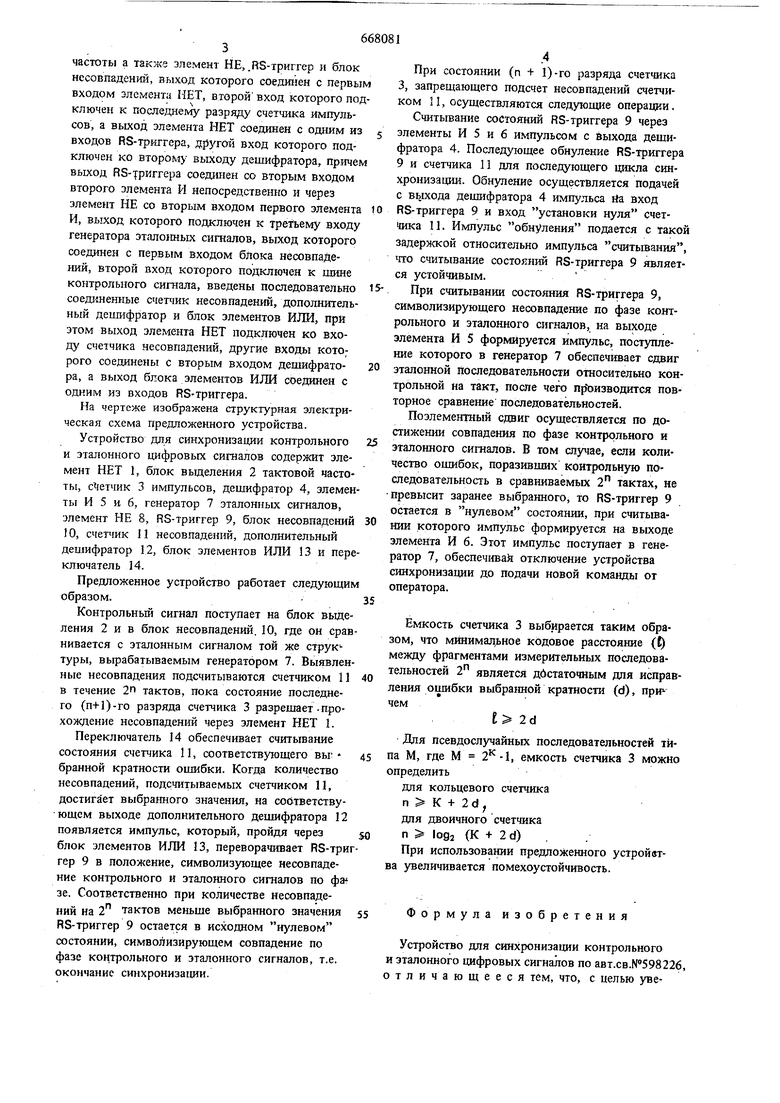

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство для синхронизации контрольного и эталонного цифровых сигналов содержит элемент НЕТ 1, блок выделения 2 тактовой частоты, с1етчик 3 импульсов, дешифратор 4, элементы И 5 н 6, генератор 7 эталонных сигналов, элемент НЕ 8, RS-триггер 9, блок несовпадений 10, счетчик 11 несовпадений, дополнительный дешифратор 12, блок элементов ИЛИ 13 и переключатель 14.

Предложенное устройство работает следующим образом.

Контрольный сигнал поступает на блок вьщеления 2 и в блок несовпадений. 10, где он сравнивается с эталонным сигналом той же структуры, вьфабатываемым генератором 7. Выявленные несовпадения подсчитываются счетчиком 11 в течение 2п тактов, пока состояние последнего (п+1)-го разряда счетчика 3 разрешает.прохождение несовпадений через элемент НЕТ 1.

Переключатель 14 обеспечивает считывание состояния счетчика 11, соответствующего вы бранной кратности ошибки. Когда количество несовпадений, подсчитываемых счетчиком И, достигает выбра шого значения, на соответствующем выходе дополнительного дешифратора 12 появляется импульс, который, пройдя через

блок элементов ИЛИ 13, переворачивает RS-триггер 9 в положение, символизующее несовпадение контрольного и эталонного сигналов по фа зе. Соответственно при количестве несовпадений на 2 тактов меньше выбранного значения RS-триггер 9 остается в исходном нулевом состоянии, символизирующем совпадение по фазе контрольного и эталонного сигналов, т.е. окончание синхронизавди.

При состоянии (п + 1)-го разряда счетчика 3, запрещающего подсчет несовпадений счетчиком II, осуществляются следующие операции.

Считывание состояний RS-триггера 9 через элементы И 5 и 6 импульсом с выхода дешифратора 4. Последующее обнуление RS-триггера 9 и счетчика 11 для последующего цикла синхронизации. Обнуление осуществляется подачей с вь.кода дешифратора 4 импульса йа вход RS-триггера 9 и вход установки нуля счетteKa 11. Импульс обнуления подается с тако задержкой относительно импульса считывания что считывание состояний RS-триггера 9 является устойчивым.

При считывании состояния RS-триггера 9, символизирующего несовпадение по фазе контрольного и эталонного сигналов, на выходе элемента И 5 формируется импульс, поступление которого в генератор 7 обеспечивает сдвиг эталонной последовательности относительно контрольной на такт, после чего производится повторное сравнение последовательностей.

Поэлементный сдвиг осуществляется по достижении совпадения по фазе контрольного и эталонного сигналов. В том случае, если количество ошибок, поразивших контрольную последовательность в сравниваемых 2 тактах, не превысит заранее выбранного, то RS-триггер 9 остается в нулевом состоянии, при считывании которого импульс формируется на выходе элемента И 6. Этот импульс поступает в генератор 7, обеспечдаай отключение устройства синхронизации до подачи новой команды от оператора.

Емкость счетчика 3 выбирается таким образом, что минимальное кодовое расстояние (t) между фрагментами измерительных последовательностей 2 является дбстаточным для исправления ошибки выбра1шой кратности (d), при чем

t 2d

Для псевдослучайных последовательностей типа М, где М , емкость счетчика 3 можно определить

для кольцевого счетчика

п К + 2d,

для двоичного счетчика

п logi {К + 2d)

При использовании предложенного устройвтва увеличивается помехоустойчивость.

Формула изобретения

Устройство для синхронизации контрольного и эталонного цифровых сигналов по авт.св.№598226, отличающееся тем, что, с целью увеличения помехоустойчивости, введены последовательно соединенные счетчик несовпадений, дополнителы1ый дешифратор и блок элементов ИЛИ, при этом вьиод элемента НЕТ йодключен ко входу счетчика несовпадений, другие входы которого соединены с вторым входом дешифратора, а выхид блока элементов ИЛИ соединен с одним из входов RS-триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 598226, кл. Н 04 К .5/1530. 26.05.76 г .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1976 |

|

SU598226A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1978 |

|

SU746895A1 |

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для синхронизации импульсных последовательностей | 1977 |

|

SU748838A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1979 |

|

SU999149A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Авторы

Даты

1979-06-15—Публикация

1977-10-17—Подача