Изобретение относится к импульсной технике и может быть использовано в контрольно-измерительной аппаратуре для цифровых систем передачи информации.

Известно устройство для синхронизации контрольного и эталонного цифровых сигналов, содержащее блок выделения тактовой частоты, первый выход которого соединен с входом счетчика импульсов, второй выход- с первым входом генератора эталонного сигнала, а вход - с входом устройства и первым выходом блока несовпадения, второй вход которого подключен к выходу генератора эталонного сигнала, а выход - к первому входу элемента НЕ, при этом второй вход элемента НЕ соединен с первым выходом счетчика импульсов, а выход - с первым входом триггера, второй вход которого подключен к первому выходу дешифратора, а выход - к первому входу первого элемента И, а через элемент НЕ - к первому входу второго элемента И, второй вход которого соединен с вторым выходом дешифратора и вторым входом генератора эталонного сигнала, при этом третий вход генератора эталонного сигнала соединен с выходом первого элемента И, а второй выход счетчика импульсов подключен к входу дешифратора 1.

Недостатки данного устройства - большое время вхождения в синхронизм и низкая помехоустойчивость.

Наиболее близким по технической суш,ности к предлагаемому является устройство для синхронизации контрольного и эталонного цифровых сигналов, содержащее блок выделения тактовой частоты, выход которого соединен с тактовым входом генератора эталонного сигнала, состоящего из регистра сдвига и блока логической обратной связи, при этом выход генератора эталонной последовательности связан с первым блоком несовпадений и первым входом переключающего блока, состоящего из двух элементов И, выходы которых подключены к входам элемента ИЛИ, и инвертора, включенного между первыми входами элементов И, выход переключающего блока соединен с другим входом генератора эталонного сигнала, а вторые входы блока несовпадений и переключающего блока связаны с входом устройства и входом блока выделения тактовой частоты, кроме того, выход блока несовпадений через последовательно включенные накопитель и синхрогенератор подключен к входу инвертора в переключающем блоке 2.

Недостатком известного устройства является невысокая помехоустойчивость и ограниченный диапазон рабочих частот.

Цель изобретения - повышение помехоустойчивости и расширение диапазона рабочих частот.

Поставленная цель достигается тем, что в устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов, содержащее генератор эталонного

сигнала, информационный вход которого подключен к выходу блока переключения, тактовый вход генератора эталонного сигнала подключен к выходу блока выделения тактовой частоты, а выход генератора эталонного сигнала соединен с первым входом блока переключения и с первым входом блока несовпадения, второй вход которого подключен к входной шине, к входу блока выделения тактовой частоты и к второму входу блока

0 переключения, третий вход которого подключен к выходу синхрогенератора, а также первый накопитель, введены четыре элемента И, два триггера, второй накопитель и регистр сдвига, тактовый вход которого подключен к первому входу первого элемента И, первому входу второго элемента И, к выходу блока выделения тактовой частоты и к счетному входу синхрогенератора, вход управления которого подключен к выходу второго накопителя, выход синхрогенератора подключен к установочному входу регистра сдвига и к первому входу первого триггера, второй вход которого соединен с последним разрядным выходом регистра сдвига, выход первого триггера подключен ко второму входу второго элемента И, и первому входу третьего

элемента И, второй вход которого соединен с предпоследним разрядным выходом регистра сдвига, информационный вход которого соединен с выходом блока несовпадения и с первым входом четвертого элемента И, второй вход которого соединен с вторым входом первого элемента И и с дополнительным выходом синхрогенератора, причем выход первого элемента И соединен со счетными входами первого и второго накопителей, выход четвертого элемента И соединен

с входом сброса первого накопителя и с первым входом второго триггера, второй вход которого подключен к выходу первого накопителя, а выход второго триггера подключен к входу сброса второго накопителя.

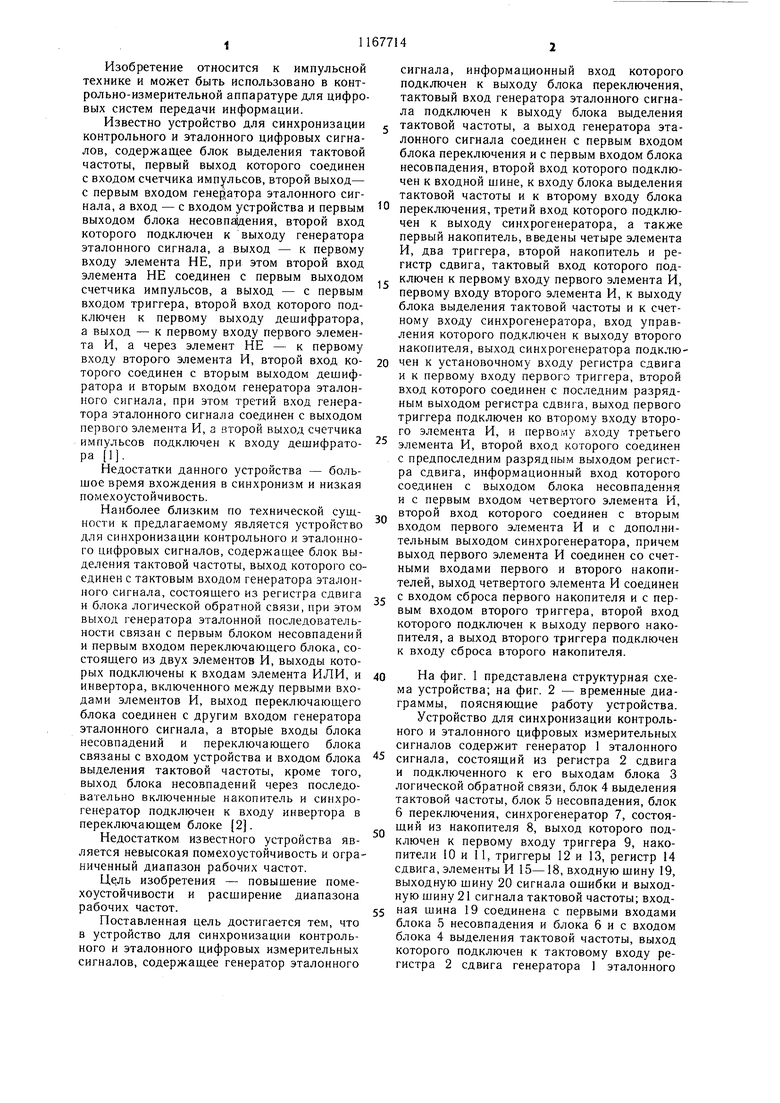

0 На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства. Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов содержит генератор 1 эталонного

5 сигнала, состоящий из регистра 2 сдвига и подключенного к его выходам блока 3 логической обратной связи, блок 4 выделения тактовой частоты, блок 5 несовпадения, блок 6 переключения, синхрогенератор 7, состоящий из накопителя 8, выход которого подключен к первому входу триггера 9, накопители 10 и 11, триггеры 12 и 13, регистр 14 сдвига, элементы И 15-18, входную шину 19, выходную шину 20 сигнала ошибки и выходную шину 21 сигнала тактовой частоты; входная шина 19 соединена с первыми входами блока 5 несовпадения и блока бис входом блока 4 выделения тактовой частоты, выход которого подключен к тактовому входу регистра 2 сдвига генератора 1 эталонного

сигнала, к тактовому входу регистра 14, к счетному входу накопителя 8 и к первым входам элементов И 15 и 18, при этом выход блока 5 несовпадения подключен к информационному входу регистра 14 сдвига и к входу элемента И 16, выход которого связан с входом сброса накопителя 10 и входом триггера 12, другой вход которого подключен к выходу накопителя 10, а выход триггера 12 соединен с входом сброса накопителя 11, причем вход накопителя 11 связан с входом накопителя 10 и выходом элемента И 15, а выход подключен к входу триггера 9 синхрогенератора 7, первый выход которого соединен с входом сброса накопителя 8 и входами элементов И 15 и 16, а другой выход подключен к входу управления блока 6, к входу установки регистра 14 и входу триггера 13, другой вход которого связан с выходом регистра 14, а выход подключен к входу элемента И 18 и входу элемента И 17, причем другой вход элемента И 17 подключен к другому выходу регистра 14, кроме того, выход блока 3 логической обратной связи связан с входом блока 6, выход которого подключен к информационному входу регистра 2 сдвига.

Блок 6 состоит из элементов И 22 и 23, выходы которых подключены к входам элемента ИЛ И. 24, а первые входы объединены через инвертор 25, вход которого является управляющим входом блока 6, вторые входы элементов И 23 и 22 являются информационными входами блока 6, а выход элемента ИЛИ 24 является выходом блока 6.

Блок 3 логической обратной связи, определяемый видом последовательности, формируемой генератором 1 эталонного сигнала, состоит из сумматоров 26 и 27 по модулю два, элементов И 28-30 и элемента ИЛИ 31, с помощью которых осуществляется выбор требуемого режима работы генератора 1 эталонного сигнала. При подаче сигналов на входы элементов И 28 или 29 с управляющих входов 32 и 33 устройства генератор 1 эталонного сигнала обеспечивает формирование псевдослучайной М-последовательности соответствующего периода, а при подаче управляющего сигнала на вход элемента И 30 с управляющего входа 34 устройства генератор 1 эталонного сигнала формирует циклическую последовательность, структура которой определяется начальным кодом, записанным в регистр 2 сдвига.

Устройство работает следующим образом.

При подаче с выхода триггера 9 синхрогенератора 7 разрешающего уровня на управляющий вход блока 6 открыт элемент И 23, а элемент И 22 закрыт благодаря инвертору 25. При этом щина 19 устройства подключается через элемент И 23 и элемент ИЛИ 24 к информационному входу регистра 2 сдвига генератора 1 эталонного сигнала. При подаче с выхода триггера 9 синхрогенератора 7 запрещающего уровня открыт

элемент И 22, а элемент И 23 закрыт благодаря инвертору 25. При этом к информационному входу регистра 2 генератора 1 эталонного сигнала через элемент И 22 и элемент ИЛИ 24 подключается выход блока 3 5 логической обратной связи. Блок 4 выделения тактовой частоты выделяет из контрольного сигнала, поступающего на щину 19 устройства, сигнал тактовой частоты, который поступает на тактовый вход генератора 1 этаQ лонного сигнала. В исходном состоянии с выхода синхрогенератора 7 на управляющий вход блока 6 поступает запрещающий уровень и генератор 1 эталонного сигнала преобразует последовательность тактовых импульсов в эталонную последовательность

5 (структура которой определена блоком 3 логической обратной связи), фаза которой первоначально не совпадает с фазой контрольного сигнала на шине 19 устройства. При этом на выходе блока 5 несовпадений появляются импульсы, поступающие на вход

0 регистра 14 сдвига. Сигнал с другого выхода синхрогенератора 7 открывает элементы И 15 и 16, за счет чего сигнал тактовой частоты с выхода блока 4 поступает на входы накопителей 10 и 11, при этом импульсы с выхода блока 5 несовпадения поступают на вход сброса накопителя 10 и вход триггера 12, причем, если интервал между соседними импульсами сигнала на выходе блока 5 несовпадения меньше емкости N накопителя 10, то последний сбрасывается раньше, чем на

0 его выходе появится импульс. При этом триггер 12 импульсами с выхода блока 5 несовпадения удерживается в состоянии, при котором отсутствует сигнал сброса накопителя 11. Тогда после накопления заданного числа NS тактовых импульсов на выходе

5 накопителя 11 появится импульс, переключающий триггер 9 синхрогенератора 7. При этом с входа сброса накопителя 8 снимается уровень, блокирующий накопитель 8, и он начинает подсчет тактовых импульсов. Сигнал с выхода синхрогенератора 7 закрывает

0 элементы И 15 и 16, за счет чего прекращается изменение состояния накопителей 10 и 11. Сигнал с первого выхода синхрогенератора поступает %а установочные входы регистра 14 сдвига, обеспечивая запись единицы в первый разряд регистра 14 сдвига и нулей во все остальные разряды, причем это состояние удерживается в течение всей длительности импульса на выходе синхрогенератора 7. Кроме того, сигнал с выхода синхрогенератора 7 переключает триггер 13

0 в положение, при котором элементы И 17 и 18 закрыты и соответствующие сигналы на шины 20 и 21 не поступают. Также сигнал с первого выхода синхрогенератора 7 поступает на управляющий вход блока 6, обеспечивая подключение тины 19 устройства

к информационному входу регистра 2 сдвига генератора 1 эталонного сигнала. Контрольная последовательность заполняет регистр 2 сдвига в течение действия импульса на выходе синхрогенератора 7. После того, как на вход накопителя 8 поступило N2 тактовых импульсов, на его выходе формируется импульс, переключающий триггер 9 в исходное положение, при котором к информационному входу регистра 2 сдвига вновь подключается выход блока 3 логической обратной связи генератора 1 эталонного сигнала. При этом генератор 1 эталонного сигнала продолжает формировать эталонную последовательность, но фаза этой последовательности совпадает с фазой контрольной последовательности, поскольку фаза эталонной последовательности была определена начальной комбинацией кодов заданной контрольной последовательности. После возвращения триггера 9 в исходное состояние, единица, записанная в регистр 14 сдвига,начинает под воздействием тактовых импульсов сдвигаться к выходу. Через П| тактов (где ni - число разрядов регистра 14 сдвига) на выходе регистра 14 появится импульс, переключающий триггер 13, сигнал с выхода которого открывает элементы И 17 и 18. Тактовые импульсы от блока 4 выделения тактовой частоты через открытый элемент И 18 проходят на шину 21, а импульсы от блока 5 несовпадения через регистр 14 сдвига и открытый элемент И 17 проходят на шину 20. Если синхронизация не наступила (например, из-за ошибки во фрагменте контрольного сигнала, записанного в регистре 2 сдвига генератора 1 эталонного сигнала в качестве начальной комбинации), то импульсы на выходе блока 5 несовпадения содержат регулярную составляющую, определяемую структурой синхронизирующих измерительных последовательностей. При несовпадении М-последовательностей, формируемых генератором 1 эталонного сигнала при подаче управляющих сигналов на входы 32 и 33, при любом их взаимном сдвиге регулярная составляющая сигнала на выходе блока 5 несовпадения представляет собой М-последовательность той же структуры, в которой максимальное число тактовых интервалов между двумя соседними импульсами не превышает (HI - 1), где П2 - число разрядов регистра 2 сдвига. При несовпадении циклических последовательностей (которые формируются при подаче управляющего уровня на вход 34) максимальное число тактовых интервалов между двумя соседними импульсами в сигнале на мходе блока 5 несовпадения также не превышает (пг-1). Емкость накопителя 10 выбирается так, чтобы . В этом случае импульсы с выхода блока 5 несовпадения сбрасывают накопитель 10 раньше, чем на его выходе появится импульс, переключающий триггер 12, сигнал с выхода которого сбрасывает накопитель 11. Поэтому на выходе накопителя 11 через N3 тактовых интервалов вновь появится импульс, переключающий триггер 9, т. е. на выходе синхрогенератора 7 появится следующий

импульс, обеспечивающий через элемент И 23 и элемент ИЛИ 24 запись в регистр 2 сдвига генератора 1 эталонного сигнала нового фрагмента из контрольной последовательности, и так далее, до тех пор, пока безошибочная запись начальной комбинации в регистр 2 сдвига не обеспечит совпадений контрольного и эталонного сигнала по фазе. При наличии синхронизации контрольного и эталонного измерительных сигналов

0 и отсутствии ошибок в контрольном сигнале импульсы на выходе блока 5 несовпадения отсутствуют и на выходе накопителя 10 через каждые NI тактовых импульсов появляется импульс, подтверждающий состояние триггера 12, сигнал с выхода которого блокирует накопитель 11, не допуская переключения триггера 9 импульсом с выхода накопителя 11. При этом триггер 9 блокирует накопитель 8 и синхрогенератор 7 не вырабатывает импульсов, при которых осуществляется запись фрагмента контрольного сигнала в регистр 2 сдвига генератора 1 эталонного сигнала, что обеспечивает устойчивое удержание синхронизма.

Если в контрольном сигна.те имеются ошибки, то при наличии синхронизации контрольного и эталонного сигналов импульсы на выходе блока 5 несовпадения являются импульсами ошибок, число которых подсчитывается за определенное количество тактовых интервалов при измерении коэффициента (вероятности) ошибок. Любой импульс ошибки переключает триггер 12 в положение, в котором снимается блокировка с накопителя 11, но импульс на-выходе накопителя 11 появляется только в том случае, если в течение N3 тактовых интервалов после любого импульса ошибок между двумя соседними импульсами не было промежутка больше NI тактовых интервалов. Выбирая значения NI и N3 достаточно большими (причем ), можно сделать вероятность ложного срабатывания устройства

под воздействием ошибок сколь угодно малой при любой вероятности ошибки, не равной 0,5 (для двоичного канала при вероятности независимых ошибок, равной 0,5, пропускная способность равна нулю и передача любой информации невозможна). Несколько подряд

следующих импульсов ошибок, например, образуюших пакет ошибок, также не приводит к появлению импульса на выходе накопителя 11 и ложному .началу синхронизации, если длительность такого пакета меньQ ше, чем (N3-NI). Если все же ложное срабатывание произошло, то импульс с второго выхода синхрогенератора 7 переключает триггер 13, который блокирует выдачу с выхода блока 5 несовпадения через регистр 14 сдвига того отрезка сигнала, который

5 может быть искажен в процессе поиска синхронизма. При этом выдача блокируется независимо от причины, вызвавшей нарушение синхронизма, т. е. не только при ложном

нарушении синхронизма, но и при сбоях, например, в блоке 4 выделения тактовой частоты. Поскольку в последнем случае импулЬс на выходе накопителя 11 появится не раньше, чем через Na тактовых интервалов, то число разрядов П| регистра 14 сдвига выбирается больше Na, т. е. . Из последовательности тактовых импульсов на шине 21 исключается количество импульсов, равное числу (Ыз+П|) тактовых интервалов, исключенных в сигнале на шине 20, в которых возможно искажение из-за нарушений синхронизма. Поэтому нарушение синхронизма независимо от причин его вызвавших, не приводит к искажению результатов измерений коэффициента ошибок прибором, в котором для синхронизации контрольного и эталонного цифровых измерительных сигналов используется предлагаемое устройство.

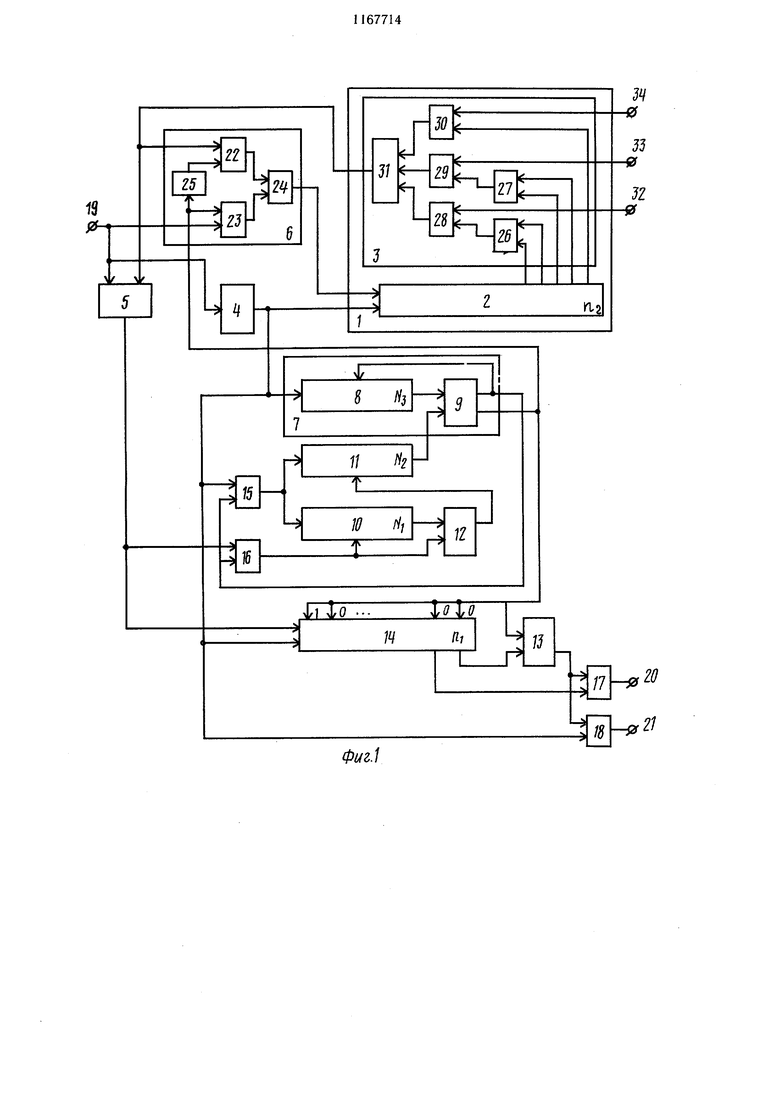

Работа устройства поясняется временными диаграммами, где буквами обозначены сигналы: а - на шине 19; б - на выходе блока 4 выделения тактовой частоты; в - на выходе элемента ИЛИ 31, являюшегося выходом генератора 1 эталонного сигнала; г - на выходе блока 5 несовпадения; д - на выходе триггера 9, являюш,егося выходом синхрогенератора 7; е - на выходе элемента И 5; ж - на выходе элемента И 16; з - на выходе триггера 12; и - на выходе накопителя 10; к - на выходе накопителя 1Г; л - на выходе накопителя 11; л - на выходе накопителя 8; ж - на последнем выходе регистра 14 сдвига (цифрами 00...01 обозначен вывод записанной комбинации); н - на предпоследнем выходе регистра 14 сдвига; о - на выходе триггера 13; я - на шине 20 (выход элемента И 17); р - на шине 21 (выход элемента И 18); с - на выходе элемента И 22; т - на выходе элемента ИЛИ 24.

Временные диаграммы отражают работу устройства после его включения, поэтому участок «Л в сигналах (фиг. 2п и 2р) является искаженным, поскольку все элементы памяти, в том числе регистр 14 сдвига, триггер 13, после включения устанавливаются произвольно. Исключение этого участка может быть достигнуто известным способом.

например, применением времязадающеи цепи, устанавливаюшей триггер 9 после включения в требуемое положение. В этом случае диаграмма работы устройства после включения соответствует участку «В. Однако предлагаемое устройство используется в контрольноизмерительной аппаратуре, элементы памяти которой после включения устанавливаются также произвольно и .требуют общей установки исходного состояния, в том числе

0 счетчиков ошибок и тактовых интервалов, зафиксировавших результат поступления сигналов участка «А. Поэтому введение специальной установочной цепи является избыточным.

Таким образом, предлагаемое устройство обладает большей помехоустойчивостью, чем известное, поскольку ложное нарушение синхронизма из-за воздействия ошибок не происходит в любом случае, если длина пакета ошибок меньше (N3-NI), причем это значение можно сделать сколь угодно большим, в частности (Na-Ni), а вероятность превышения этого значения (т. е. вероятность ложного нарушения синхронизма из-за воздействия ошибок) сколь угодно малой, тогда как в известном устройстве ложное нарушение синхронизма происходит уже в том случае, если два импульса ошибок появятся через интервал, меньший, чем П2, т. е. применение известного устройства возможно при

малых вероятностях ошибок Рош-с-, а предлагаемое устройство можно применять при ,5. Однако даже нарушения синхронизма, вызванные любыми причинами, не приводят к искажению входного сигнала и, как следствие, результатов измерения коэффициента ошибок прибором, в котором применяется данное устройство (в отличие от применения известного устройства). Кроме того, помехоустойчивость предлагаемого устройства определяется только параметрами N:, N2 и Na, которые в известном устройстве

Q зависят от частоты, а в предлагаемом устройстве не зависят от частоты. Поэтому помехоустойчивость предлагаемого устройства не зависит от частоты, что обеспечивает возможность его применения в широком диапазоне рабочих частот.

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОНТРОЛЬНОГО И ЭТАЛОННОГО ЦИФРОВЫХ ИЗМЕРИТЕЛЬНЫХ СИГНАЛОВ, содержащее генератор эталонного сигнала, информационный вход которого подключен к выходу блока переключения, тактовый вход генератора эталонного сигнала подключен к выходу блока выделения тактовой частоты, а выход генератора эталонного сигнала соединен с первым входом блока переключения и с первым входом блока несовпадения, второй вход которого подключен к входной шине, к входу блока выделения тактовой частоты и ко второму входу блока переключения, третий вход которого подключен к выходу синхрогенератора, а также первый накопитель, отличающееся тем, что, с целью повышения помехоустойчивости и расширения диапазона рабочих частот, в него введены четыре элемента И, два триггера, второй накопитель и регистр сдвига, тактовый вход которого подключен к первому входу первого элемента И, первому входу второго элемента И, к выходу блока выделения тактовой частоты и к счетному входу синхрогенератора, вход управления которого подключен к выходу второго накопителя, выход синхрогенератора подключен к установочному входу регистра сдвига и к первому входу первого триггера, второй вход которого соединен с последним разрядным выходом регистра сдвига, выход первого триггера подключен ко второму входу второго элемента И и первому входу третьего элемента И, второй вход которого соединен с предпоследним разрядным выходом регистра сдвига, информационный вход которого соединен с выходом блока несовi падения и с первым входом четвертого элемента И, второй вход которого соединен (Л с вторым входом первого элемента И и с дополнительным выходом синхрогенератора, причем выход первого элемента И соединен со счетными входами первого и второго накопителей, выход четвертого элемента И соединен с входом сброса первого накопителя и с первым входом второго триггера, второй вход которого подключен к выходу первого накопителя, а выход второго триг05 гера подключен к входу сброса второго на копителя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1976 |

|

SU598226A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1979 |

|

SU999149A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-15—Публикация

1983-08-04—Подача