1

Изобретение относится к импульсной технике и может быть применено при построении аппаратуры тестирования и настройки оборудования цифровых сис-j тем связи и вычислительной техники.

Известно устройство для синхронизации импульсных последовательностей,, содержащее вьщелитель тактовой частоты, генератор эталонной последова-- Q тельности, регистр сдвига, элемент запрета, элементы И, первые входы первого и второго из которых объединены, два RS-триггера и инвертор 1.

Недостаток известного устройства заключается в низкой надежности и ограниченном диапазоне структур измерительных последовательностей.

Цель изобретения - повышение надежности устройства и расширениГе диапа- JQ зона структур синхронизируемых послецовате гпьностей.

Поставленная цель достигается тем, что в устройство для синхронизации импульсных последовательностей, со- jj держащее выделитель тактовой частоты, генератор эталонной последовательнос ти, регистр сдвига, элемент запрета, элементы И, первые входы первого и второго из которых объединены, два Q

RS-триггера и инвертор, в него дополнительно введены элемент несовпадения и синхрогенератор, выход которого соединен с первым входом третьего элемента И и через инвертор с первым входом первого элемента И, выход которого подключен к информационному входу регистра сдвига, прямой выход первого разряда и инверсный выход второго разряда которого через четвертый элемент И подключены к запрещающему входу элемента запрета и S-входу первого RS-триггера, R-вxoдf которого соединен с выходом третьего элемента И, а прямой и инверсный выходысо вторыми входами первого и второго элементов И соответств.енно, причем элемент запрета через генератор эталонной последовательности соединен с первым входом элемента несовпадения, информационный вход элемента запрета через вьщелитель тактовой частоты подключен к входной шине и второму входу элемента, несовпадения, выход которого соединен со вторым входом третьего элемента И, третий вход которого соединен с выходом второго RS-триггера, S и R входы которого подключены к выходу второго элемента И

И Шине синхронизации соответственно, а выход выделителя, тактовой частоты соединеи с тактовым входом регистра сдвига.

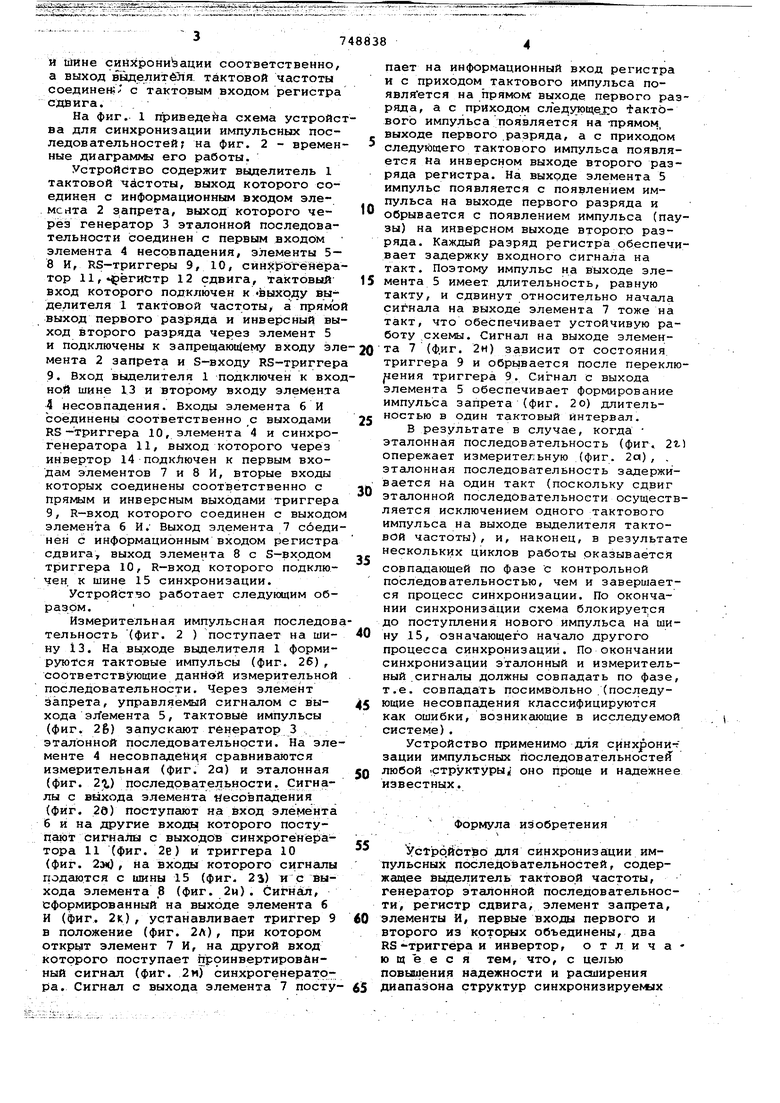

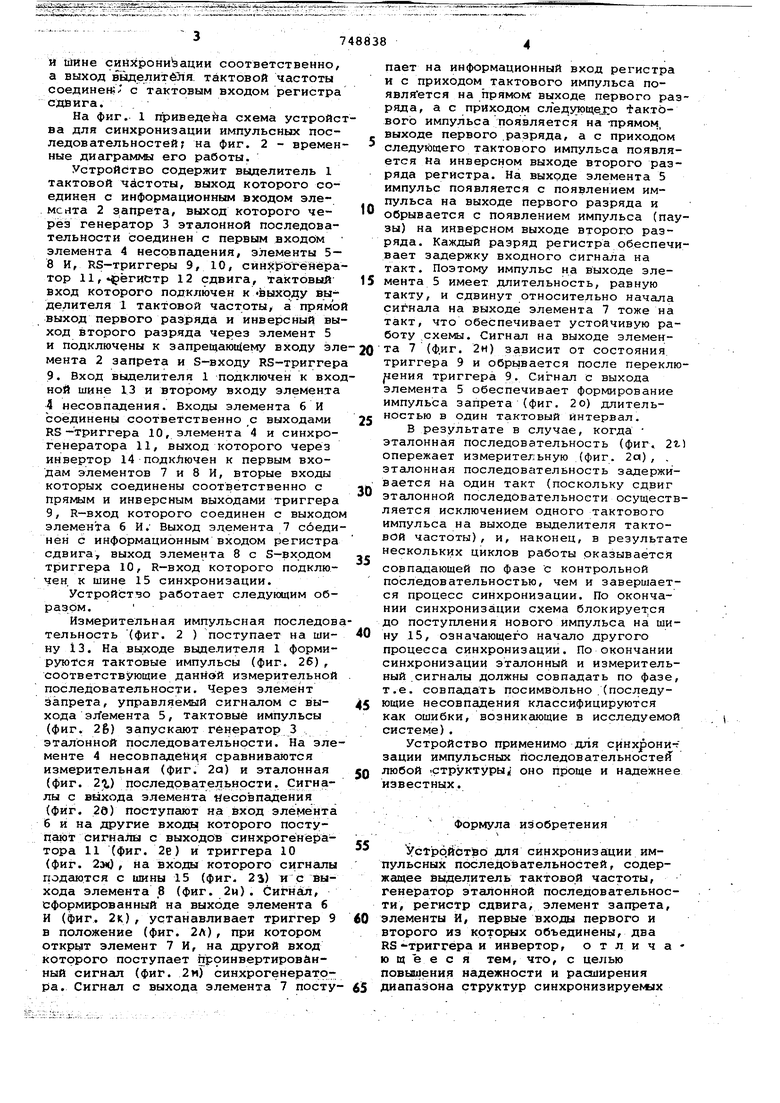

На фиг. 1 приведейа схема устройства для синхронизации импульсных последовательностей; на фиг. 2 - временные диаграмкы его работы.

Устройство содержит выделитель 1 тактовой чистоты, выход которого соединен с информационным входом элемента 2 запрета, выход которого черёэ генератор 3 эталонной последовательности соединен с первым входом элемента 4 несовпадения, элементы 58 И, RS-триггеры 9, 10, сиНхрогенёратор 11,регистр 12 сдвига, тактовый вход которого подключен к «выходу выделителя 1 тактовой частоты, а прямой выход первого разряда и инверсный выход второго разряда через элемент 5 и подключены к запрещающему входу эле мента 2 запрета и S-входу RS-триггера . Вход выделителя 1 подключен к входной шине 13 и второму входу элемента 4 несовпадения. Входы элемента 6 И соединены соответственно с выходами RS-триггера 10, элемента 4 и синхрогенератора 11, выход которого через инвертор 14 подключен к первым входам элементов 7 и 8 И, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера 9, R-вход которого соединен с выходом элемента 6 И. Выход элемента 7 соединен с информационным входом регистра сдвига, выход элемента 8 с S-вхрдом триггера 10, Н-вход которого подключен, к шине 15 синхронизации.

Устройство работает следующим образом.

Измерительная импульсная последовательность (фиг. 2 ) поступает на шину 13. На выходе выделителя 1 формируются тактовые импульсы (фиг. 26), соответствующие данной измерительной последовательности. Через элемент Запрета, управляемый сигналом с выхода элемента 5, тактовые импульсы (фиг. 26) запускают гбнератор 3 эталонной последовательности. На элементе 4 несовпадения сравниваются измерительная (фиг. 2а) и эталонная (фиг. 21.) последовательности. Сигналы с выхода элемента Несовпадения (фиг. 2в) поступают на вход элемента 6 и на другие входы которого поступают сигналы с выходов синхрогёнёратора 11 (фиг. 2е) и триггера 10 (фиг. , на входы которого сигналы подаются с шины 15 (фиг. 2Ъ) и с выхода элемента 8 (фиг. 2м) . Си1нал, сформированный на выходе элемента б И (фиг. 2к), устанавливает триггер 9 в положение (фиг. 2л), при котором открыт элемент 7 И, на другой вход которого поступает проинвертировакный сигнал (фиг. 2и) синхрогенерато-; ра. Сигнал с выхода элемента 7 поступает на информационный вход регистра и с приходом тактового импульса появляется на прямом: выходе первого разряда, а с приходом следующехо тактового импульса появляется на-прямом, выходе первого .разряда, а с приходом следующего тактового импульса появляется на инверсном выходе второго разряда регистра. На выходе элемента 5 импульс появляется с появлением импульса на выходе первого разряда и обрывается с появлением импульса (паузы) на инверсном выходе второго разряда. Каждый разряд регистра обеспечивает задержку входного сигнала на такт. Поэтому импульс на выходе элемента 5 имеет длительность, равную такту, и сдвинут относительно начала сигнала на выходе элемента 7 тоже на такт, что обеспечивает устойчивую работу .схемы. Сигнал на выходе элемен та 7 (ф.иг. 2н) зависит от состояния триггера 9 и обрьавается после переклю ения триггера 9. Сигнал с выхода элемента 5 обеспечивает формирование импульса запрета (фиг. 2о) длительностью в один тактовый Интервал.

В результате в случае, когда эталонная последовательность (фиг. 2 опережает измерительную (фиг. 2а), , эташонная последовательность згщерживается на один такт (поскольку сдвиг эталонной последовательности осуществляется исключением одного тактового импульса на выходе выделителя тактовой частоты), и, наконец, в результат нескольких циклов работы оказывается совпадающей по фазе С контрольной последовательностью, чем и завершается процесс синхронизации. По окончании синхронизации схема блокирует.ся до поступления нового импульса на шину 15, означающего начало другого процесса синхронизации. По окончании синхронизации этешонный и измерительный .сигналы должны совпадать по фазе, т.е. совпадать посимвольно .(последующие несовпадения классифицируются как ошибки, возникающие в исследуемой системе).

Устройство применимо для синхрони- зации импульсных последовательностей любой .структуры оно проще и надежнее известных.

Формула изобретения

Устройство для синхронизации импульсных последовательностей, содержащее выделитель тактовой частоты, генератор эталонной последовательности, регистр сдвига, элемент запрета, элементы И, первые входы первого и второго из которых объединены, два RS-триггера и инвертор, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и расширения диапазона структур синхронизируемых

последовательностей, в него дополнительно введены элемент несовпадения и синхрогенератор, выход которого соединен с первым входом третьего элемента И и через инвертор с первым входом первого элемента И, выход которого .подключен к информационному входу регистра сдвига, прямой выход первого разряда и инверсный выход второго разряда которого через четвертый элемент И подключены к запрещающему входу элемента запрета и Sвходу первого RS-триггера, R-вход которого соединен с выходом третьего элемента И, а прямой и инверсный выходы - со вторыми входами первого и второго элементов И соответственно, причем элемент запрета через генератор эталонной последовательности соединен с первым входом элемента несовпадения, информационный вход элемента запрета через выделитель тактовой частоты подключен к входной шийе и второму входу элемента несовпадения, выход которого соединен со вторым входом третьего элемента И, третий вход которого соединен с вызгодом второго RS-триггера, S и R входи ко торого подкл1очены к выходу второго элемента И и шине синхронизации соОтвётственно, а выход выделителя тактовой частоты соединен с тактовым входом регистра сдвига.

Щеточники информации, принятые во внимание при экспертизе 5 1, Левин Л.С.I Плоткин М.А. Осно1 ы построения цифровых систем Tiepeдачи. М., Связь, 1975, с. 117, ;РИС, 4.1 (прототип).

«V

Г

uC

Авторы

Даты

1980-07-15—Публикация

1977-08-08—Подача