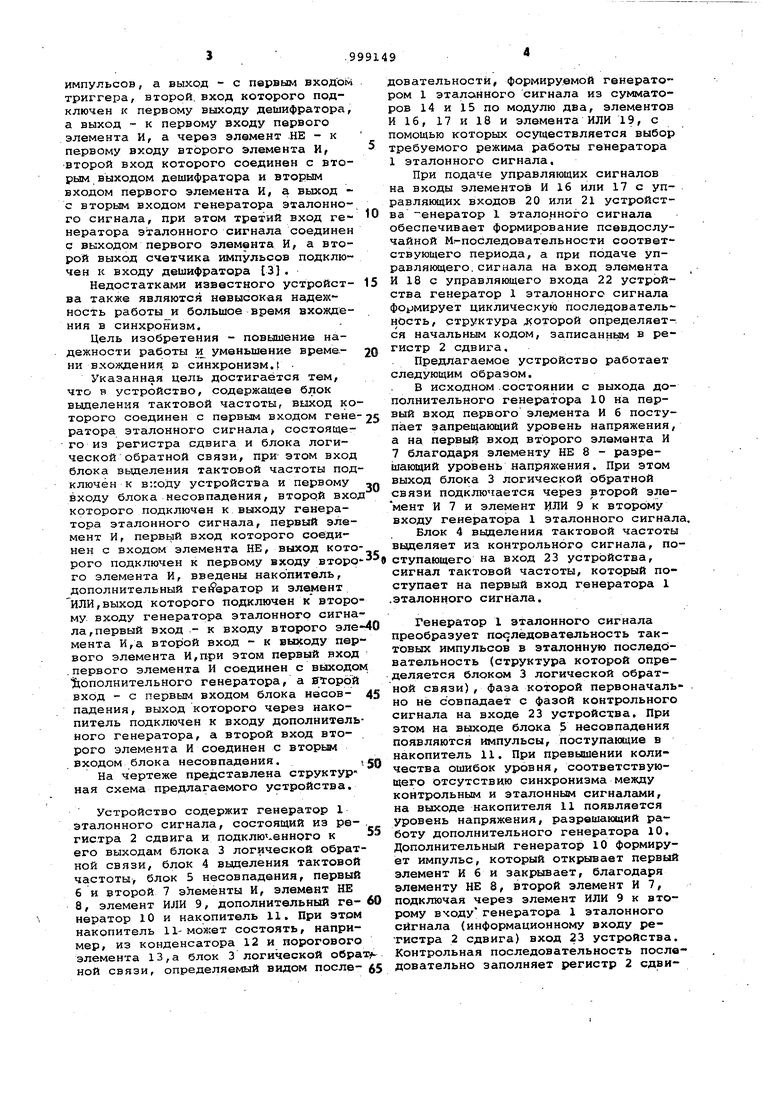

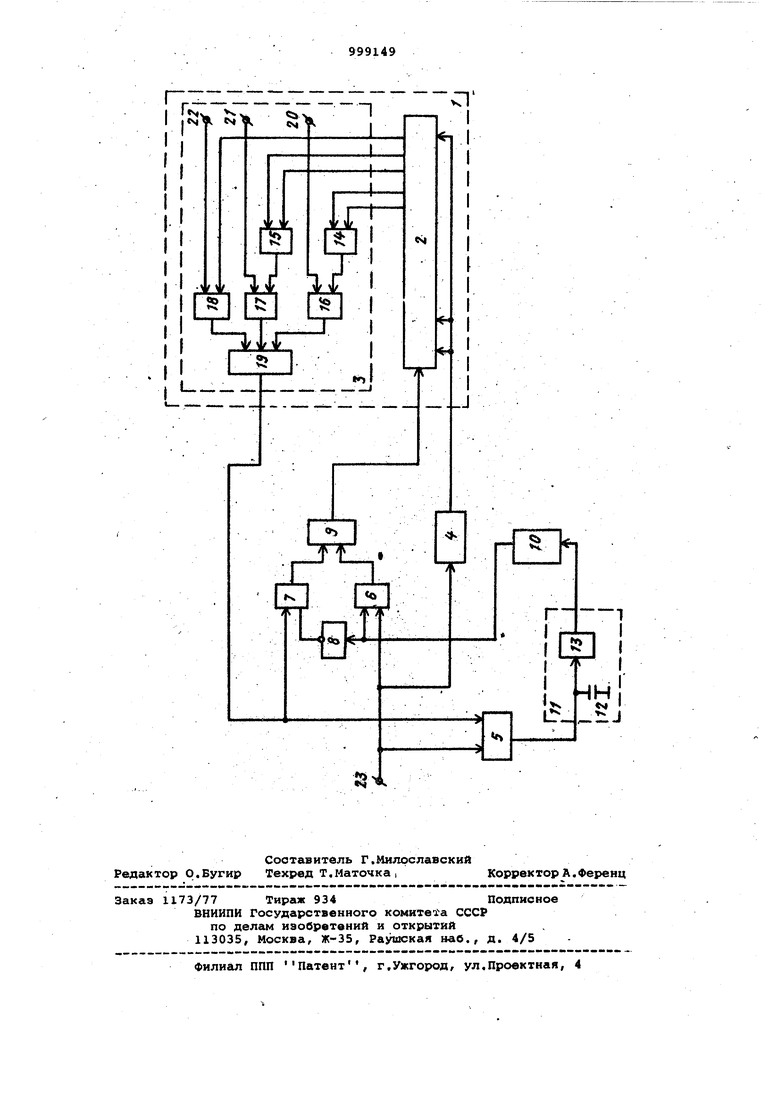

импульсов, а выход - с первым входом триггера, второй, вход которого подключен к первому ВБ1ХОДУ дешифратора, а выход - к первому входу первого элемента И, а через элемент .НЕ - к первому входу второго элемента И, второй вход которого соединен с вторым выходом дешифратора и вторым входом первого элемента И, а выход с вторым входом генератора эталонного сигнала, при этом третий вход ге нератора эталонного сигнала соединен с выходом первого элемента И, а второй выход счетчика импульсов подклю чен к входу дешифратора 13. Недостатками известного устройства также являются невысокая надежность работы и большое время вхождения в синхронизм. Цель изобретения - повышение надежности работы и уменьшение време.ни вхождения, в синхронизм, . Указанная цель достигается тем/ что в устройство, содержащее блок выделения тактовой частоты, выход ко торого соединен с первым входом гене ратора эталонного сигнала, состоящего из регистра сдвига и блока логической обратной связи, при этом вход блока выделения тактовой частоты под ключен к в::оду устройства и первому Ёходу блока несовпадения, вторрй вхо которого подключен к выходу генератора эталонного сигнала, первый элемент И, первый вход которого сое динен с входом элемента НЕ, выход кото рого подключен к первому входу второ го элемента И, введены накопитель, дополнительный гейЪратор и элемент или,выход которого подключен к второ му входу генератора эталонного сигна ла, первый вход - к входу второго эле мента И,а второй вход - к выходу пер вого элемента И,при этом первый вход первого элемента И соединен с выходо ;Ьополнительного генератора, а второй вход - с первым входом блока несовпадения, выход которого через накопитель подключен к входу дополнитель ного генератора, а второй вход второго элемента И соединен с вторым входом блока несовпадения. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит генератор 1 эталонного сигнала, состоящий из PSгистра 2 сдвига и подключенного к его выходам блока 3 логической обрат ной связи, блок 4 выделения тактовой чг1стоты, блок 5 несовпадения, первый б и второй 7 элементы И, элемент НЕ 8, элемент ИЛИ 9, дополнительный ганератор 10 и накопитель 11. При этом накопитель 11-может состоять, например, из конденсатора 12 и порогового элемента 13,а блок 3 логической обра ной связи, определяемый видом последовательностй, формируемой генератором 1 эталонного сигнала из сумматоров 14 и 15 по модулю два, элементов И1б, 17и18и элемента ИЛИ 19, с помощью которых осутцествляется выбор требуемого режима работы генератора 1 эталонного сигнала, При подаче управляющих сигналов на входы элементов И 16 или 17 с управляющих входов 20 или 21 устройства -енератор 1 эталонного сигнала обеспечивает формирование псевдослучайной М.-последовательности соответствующего периода, а при подаче управляющего, сигнала на вход элемента И 18 с управляющего входа 22 устройства генератор 1 эталонного сигнала формирует циклическую последовательность, структура 4 оторой определяет-. ся начальным кодом, записаннЕлм в регистр 2 сдвига. Предлагаемое устройство работает следующим образом, В исходном .состоянии с выхода дополнительного генератора 10 на первый вход первого И 6 поступает запрещакмций уровень напряжения, а на первый вход второго элемента И 7 благодаря элементу НЕ 8 - разрешающий уровень напрях ения. При этом выход блока 3 логической обратной связи подключается через второй элемент И 7 и элемент ИЛИ 9 к второму входу генератора 1 эталонного сигнала. Блок 4 выделения тактовой частоты выделяет из контрольного сигнала, поступающего на вход 23 устройства, сигнал тактовой частоты, который поступает на первый вход генератора 1 .эталонного сигнала. Генератор 1 эталонного сигнала преобразует последовательность тактовых импульсов в эталонную последовательность (структура которой определяется блоком 3 логической обратной связи), фаза которой первоначально не совпадает с фазой контрольного сигнала на входе 23 устройст;ва. При этом на выходе блока 5 несовпадения появляются импульсы, поступаюдие в накопитель 11, При превышении количества ошибок уровня, соответствующего отсутствию синхронизма между контрольным и эталонным сигналс1ми, на выходе накопителя 11 появляется уровень напряжения, разрешающий работу дополнительного генератора 10, Дополнительный генератор 10 формирует импульс, который открывает первый элемент И 6 и закрьшает, благодаря элементу НЕ 8, второй элемент И 7, подключая через элемент ИЛИ 9 к второму входу генератора 1 эталонного сигнала (информационному входу ретистра 2 сдвига) вход 23 устройства. Контрольная последовательность последовательно заполняет регистр 2 сдви га. По окончаний импульса на выходе дополнительного rejiepaTOpa 10 к второму входу генератора 1 эталонного сиг,нала вновь подключается выход блока 3 логической обратной свлзн генератора 1 эталонного сигнала.При этом генаратор 1 эталонного сигнала продолжает формировать эталонную последовательность, но фаза этой последовательности совпадает с фазой контрольной последо вательности,поскольку фаза эталонной О последовательности была определена начальной комбинацией, заданной контрольной последовательностью..

При наличии синхронизации контрольного и эталонного сигналов импульсы 15 на выходе блока 5 несовпадения отсутствуют и на выходе накопителя 11 появляется уровень напряжения, блокирующий дополнительный генератор 10. Если синхронизация не наступает (на- 20 пример, за счет ошибки во Фрагменте контрольного сигнала, записанном в регистр 2 сдвига генератора 1 эталонного сигнала в качестве начальной комбимации), то уровень напряжения на 25 выходе накопителя 11 остается неизменным и после паузы, определяемой величиной скважности работы дополнительного генератора 10, на выходе дополнительного генератора 10 появля-« ется следующий импульс, обеспечивгиощий через первый элемент И 6 и элемент ИЛИ 9 запись в регистр 2 сдвига генератора 1 эталонного сигнала новой начальной комбинации из контрольного сигнала, и так далее до совпаде- ния контрольного и эталонного сигналов по фазе.

При этом длительность импульса на выходе дополнительного генератора 10 должна быть не менее п Т,- где п - 40 число разрядов регистра 2 сдвига генератора I эталонного сигнала, а Т - период тактовой частоты на выходе блока 4 выделения тактовой часто-, ты. Пауза между импульсами на выхо- 45 де дополнительнрго генератора 10 должна быть достаточной для разряда накопителя после наступления синхронизма {например, для разряда накопительного конденсатора 12)«jO

Предлагаемое устройство обеспечивает повышенную надежность работы эа счет обеспечения автоматического восстановления синхронизации при сбоях или при ложном вхождении в син- jj хронизм. Кроме того, длительность .процесса вхождения в синхронизм в

предлагаемом изобретении равна п Т и в И раз меньше, чем в известном (М - длина синхронизируемой последовательности) . Особенно значительный выигрыш достигается при использовании предлагаемого устройства для синронизации псевдослучайных последовательностей больших периодов . Например, при синхронизации М-последовательности с периодом () длительность процесса уменьшается в 10 раз.

Формула изобретения

Устройство для синхронизации контрольног.о и эталонного цифровых сигналов , содержащее блок вьщеления тактовой частоты, выход которого соединен с первым входом генератора эталонного сигнала, состоящего из регисра сдвига и блока логической обратной , при этом вход блока выделения тактовой частоты подключен к входу устройства и пересяду входу бло|ка несовпадения, второй вход которого подключен к выходу генератора эталонного сигнала, первый элемент И, первый вход которого соединен с входом элемента НЕ, выход..которого подключен к первому входу второго элемента И, отличающееся тем, что, с целью повышения надежности работы и уменьшения времени вхождения в синхронизм, в него введены накопитель, дополнительный генератор и элемент ИЛИ, выход которого подключен к второму входу генератора эталонного сигнала, первый вход - к выходу второго элемента И, а второй вход - к выходу первого элемента И, пр9 этом первый вход первого элемента и соединен с выходсм дополнительного генератора, а второй вход - с первым входом блока несовпадения, выход которого через накопитель подключен к входу дополнительного генератора, а второй вход второго элемента И соединен с вторым входом блока нвсовпсщения.

Источники информации, принятые во внимание при экспертизе

1.Патент США W 3971888, кл. ITSIS, опублик. 1976.

2.Авторское свидетельство СССР .6889ЬЗ, кл. Н 03 К 5/153, 1978.

3.Авторское свидетельство СССР 598226, кл. Н.03 К 5/153, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1978 |

|

SU746895A1 |

| Устройство для измерения коэффициента ошибок в цифровых трактах передачи информации | 1989 |

|

SU1674394A1 |

| Устройство синхронизации измерительных последовательностей | 1978 |

|

SU720766A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для измерения коэффициента ошибок в цифровых трактах передачи информации | 1981 |

|

SU1040617A1 |

| Устройство синхронизации с М-последовательностью | 1987 |

|

SU1522420A1 |

| Устройство для синхронизации контрольного и эталонного цифровых сигналов | 1976 |

|

SU598226A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации М-последовательности | 1990 |

|

SU1734226A1 |

Авторы

Даты

1983-02-23—Публикация

1979-07-02—Подача