Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств универсальных и специализированных цифровых вычислительных машин.

Известны устройства, содержащие регистры множимого и множителя, сумматор, группу элементов И, матрицу модулей.

Недостатками известных устройств являются представление чисел и организация частичных произведений параллельным способом и большой расход оборудования на матрицу модулей.

Известно устройство для умножения чисел, содержащее (n-Н) и п-разрядные сдвиговые регистры первого и второго сомножителей, первую из (п+1)-го и вторую из (п-1)-го группы элементов И, регистр из (2п+И-К) сумматоров накапливающего типа, блок управления и блок преобразования кода, элементы И, ИЛИ, выходы которых управляют соответственно первой и второй группами элементов И, выходы которых поразрядно заведены на входы регистра сумматоров, а информационные входы поразрядно - к выходам соответствующих триггеров первого и

1

00

ел

оо

4.

со

второго регистров. Элементами И, ИЛИ управляют выходы входных триггеров первого и второго соответственно сдвиговых регистров сомножителей и сигналы управления из блоков преоб разования кода и управления. В устройстве коды сомножителей поступают последовательно, а частичные произведения вырабатываются параллельным способомо

Недостатком данного устройства является организация п младших разрядов частичного произведения на последнем такте умножения, когда вводят ся младший разряд множимого и старший разряд множителя, что удлиняет операцию умножения ча п тактов, «о- торые необходимо выполнить для прогона переносов из младшего, (2п+1)-го разряда в старший

Наиболее близким к предлагаемому по техническому решению является устройство для умножения чисел в прямом коде, содержащее п-разрядные регистры первого и второго сомножителей, первую и вторую группы из п и (п-1) элементов И соответственно и n-разрядный блок суммирования (п- разрядность сомножителей), выход i-ro разряда регистра первого сомножителя соечинен с первым входом i-ro элемента И первой группы (,...,п) выход j-ro разряда регистра второго сомножителя соединен с первым входом j-ro элемента И второй группы (,

ооо,П-IJ„

Недостатками известного устройства являются повышенный расход оборудования, так как блок суммирования состоит из 2п разрядов, пониженное быстродействие устройства в целом, так как результат умножения получают через Зп тактов (n-тактов на формирование частичных произведений и 2п тактов - на прогон переносов из младшего 2п-го разряде в старший) и задержанный на п тактов процесс получения младшего 2п-го разряда кода результата. Это связано с тем, что п младших разрядов частичного произведения кода результата формируют на последнем n-м такте, когда введены старший и младший соответственно разряды регистров первого и второго сомножителей. После этого требуется выполнить 2п тактов для прогона переносов из младших разрядов блока суммирования в старшие.

5

0

5

Целью изобретения является сокращение аппаратных затрат, ускорение начала вычисления и повышение быст- родействия в целом.

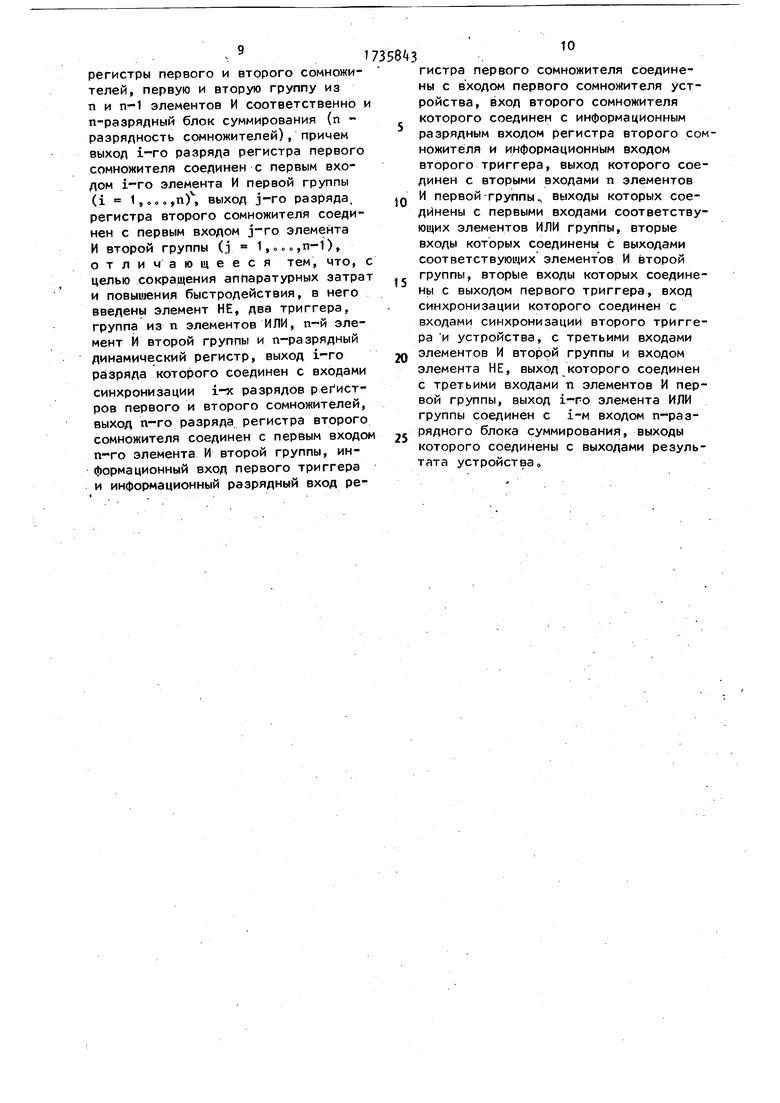

Для достижения поставленной цели в устройство введены элемент НЕ, два триггера, группа из п элементов ИЛИ, n-й элемент И второй группы и Q n-разрядный динамический регистр, выход 1-го разряда которого соединен с входами синхронизации 1-х разрядов регистров первого и второго сомножителей, выход n-го разряда регистре второго сомножителя соединен с первым входом n-го элемента И второй группы, информационный вход первого триггера и информационный разрядный вход регистра первого сомножителя соединены с входом первого сомножителя устройства, вход второго сомножителя которого соединен с информационным разрядным входом регистра второго сомножителя и информационным входом второго триггера, выход которого соединен с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И второй труп- пы, вторые входы которых соединены с выходом первого триггера, вход синхронизации которого соединен с входами синхронизации второго триггера и устройства, с третьими входами элементов И второй группы и входом элемента НЕ, выход которого соединен с третьими входами п элементов И первой группы, выход 1-го элемента ИЛИ группы соединен с i-м входом п-раз- рядного блока суммирования, выходы которого соединены с выходами результата устройства,,

Введенные блоки и элементы с их связями обеспечивают умножение двух чисел, представленных последовательным кодом младшими разрядами вперед, с организацией за п тактов всех частичных произведений параллельным спо- 0 собом с формированием младшего 2п-го разряда кода результата на первом такте умножения, когда в устройство введены младшие n-е разряды сомножителей После формирования всех частич- 5 ных произведений, т.е. через п тактов, следует выполнить п тактов для получения результата умножения (после формирования переносов в старший разряд).

0

5

0

5

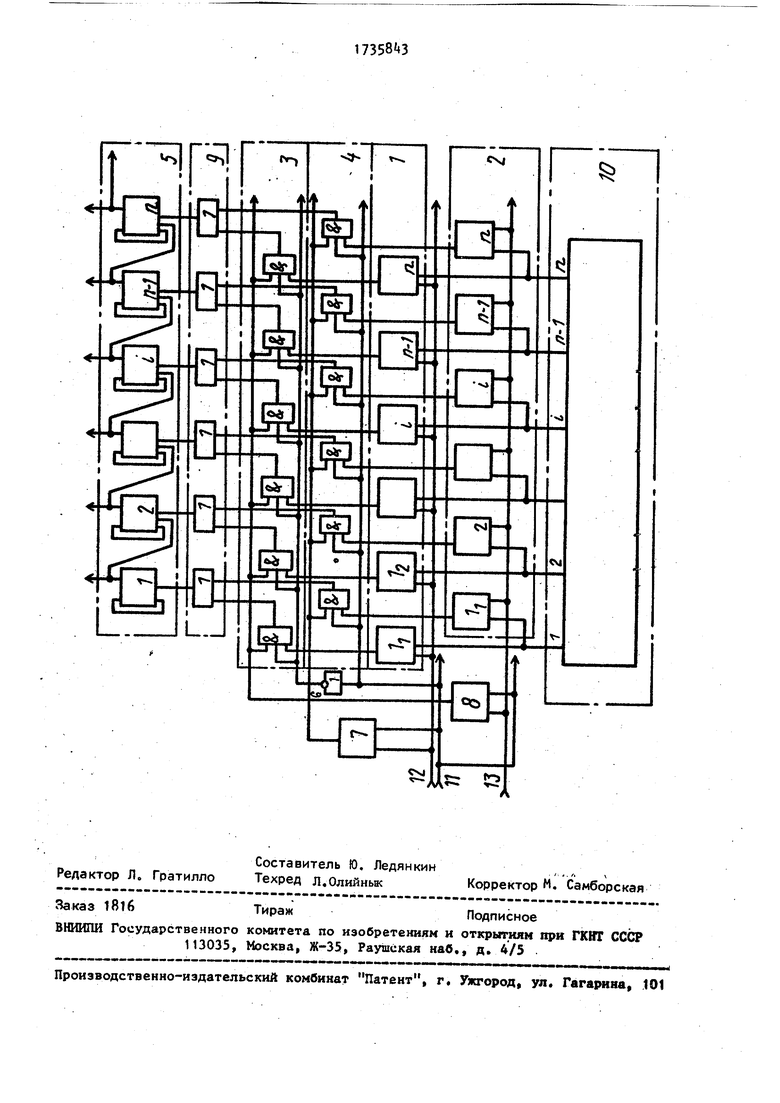

На чертеже представлена схема устройства о

Устройство содержит п-разрядные регистры первого 1 и второго 2 сомножителя, первую 3 и вторую k группы элементов И, блок 5 суммирования, инвертор 6, первый 7 и второй 8 триггеры, n-разрядчые группы элементов ИЛИ 9 и динамический регистр 10, вход 11 синхронизации устройства, входы первого 12 и второго 13 сомножителей устройства и выходы блока суммирования.

173

При работе устройства младшими разрядами вперед одновременно поступают 1-е (,п) разряды кодов сомножителей соответственно множимого (А) и множителя (В). Одновременно на выходе 1-го разряда динамического регистра 10 вырабатывают сигнал управления, который поступает на вход синхронизации 1-х разрядов регистра обоих сомножителей и разрешает ввод значений поступивших бит сомножителей в 1-е разряды регистров первого 1 и второго 2 сомножителей. На сигнале управления С с входа 11 синхронизации устройства, 1-е разряды обоих регистров сомножителей, а также оба триггера 7 и 8 установят в состоянии соответствующих бит сомножителей. Работу устройства начинают с подачи младших n-х разрядов.

Первые входы 1-х (,п) элементов И первой 3 и второй k групп по- разрядно подключены к i-м (,п) выходам регистров первого 1 и второго 2 сомножителей, вторые входы элементов И объединены и подключены к выходам второго 8 и первого 7 соответственно триггеров устройства, а третьи входы - к входу 11 синхронизации устройства через инвертор 6 непосредственно, а выходы элементов И первой 3 и второй групп поразрядно через первый и второй соответственно входы элементов ИЛИ группы 9 подключены к i-м (,п) входам блока 5 суммирования.

Состояния текущих 1-у разрядов кодов множимого (А) и множителя (В), которые запомнены на один такт в пе первом 7 и втором 8 триггерах устройства на i-м такте работы через вторые входы первой 3 и второй групп элементов И разрешают или запрещают

передачу в блок 5 суммирования 1-х частичных произведений, сформированных в обоих регистрах сомножителей. Управляющие сигналы, которые поступают с входа 11 синхронизации устройства на третьим входы обеих групп элементов И в зависимости от состояния первого 7 и второго 8 триггеров, коJQ торые своими выходами подключены к вторым входам элементов И обеих групп, осуществляют передачу в блок 5 суммирования частичных произведений, сформированных в регистрах первого 1 и второго 2 сомножителей, выходы которых соединены с первыми входами элементов И. Таким образом, частичные произведения от кода множимого (А), сформированного на регистре первого 1 сомножителя, заносят в блок 5 суммирования на противофазе (С) и при единичном состоянии текущего 1-го разряда кода множителя во втором триггере 8, а частичные про25 изведения от кода множителя (В), сформированного в регистре второго сомножителя 2, заносят в блок 5 суммирования на фазе (Ј) и при единичном состоянии текущего 1-го разряда кода множимого в первом триггере 7.

15

20

i

Работа устройства начинается, когда на вход 11 синхронизации (тактовый вход) устройства подают фазу (С); на которой всегда заносят текущие раз35 ряды кодов сомножителей в первый 7 и второй 8 триггеры, а также в регистры первого 1 и второго 2 сомножителей. При такой организации связей в течение всей процедуры умножения

40 будет иметь место отставание в занесении частичного произведения от кода множителя, сформированного в регистре второго 2 сомножителя, так как в этот момент каждый элемент И А

45 группы элементов по третьему входу будет открыт сигналом с входа 11 синхронизации устройства, а выходы с регистра второго 2 сомножителя отражают состояние регистра до момен50 та переключения, т.е. состояние предыдущего 1-го такта.

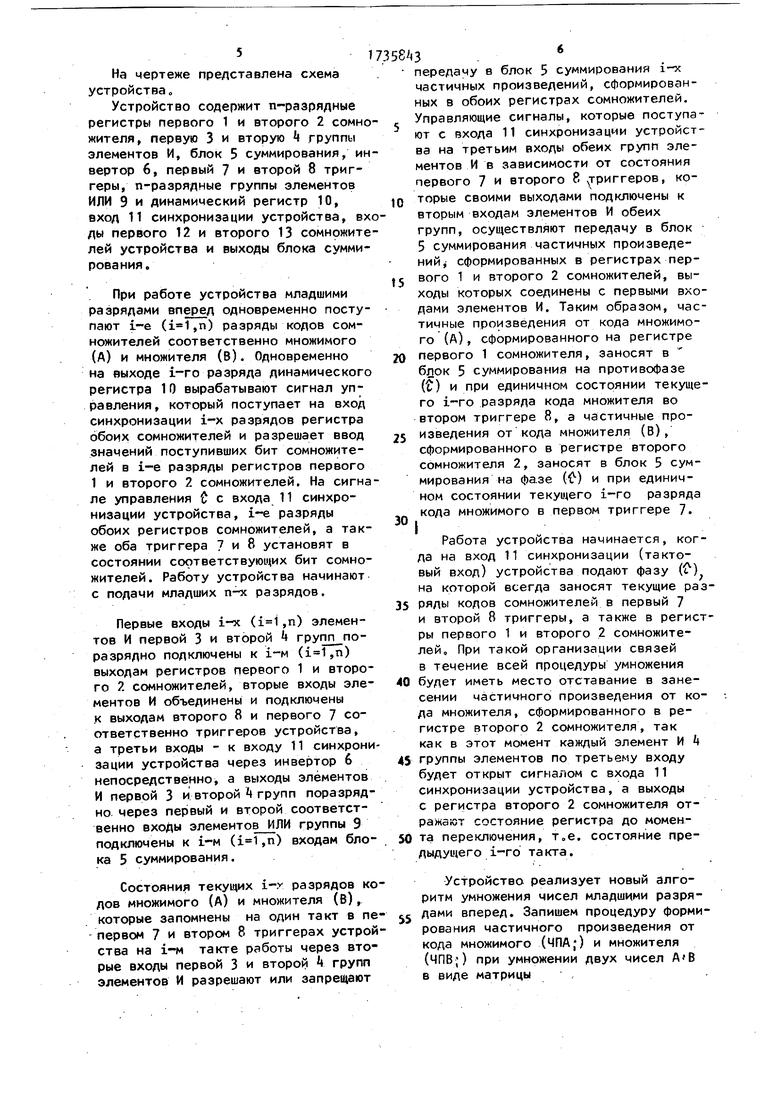

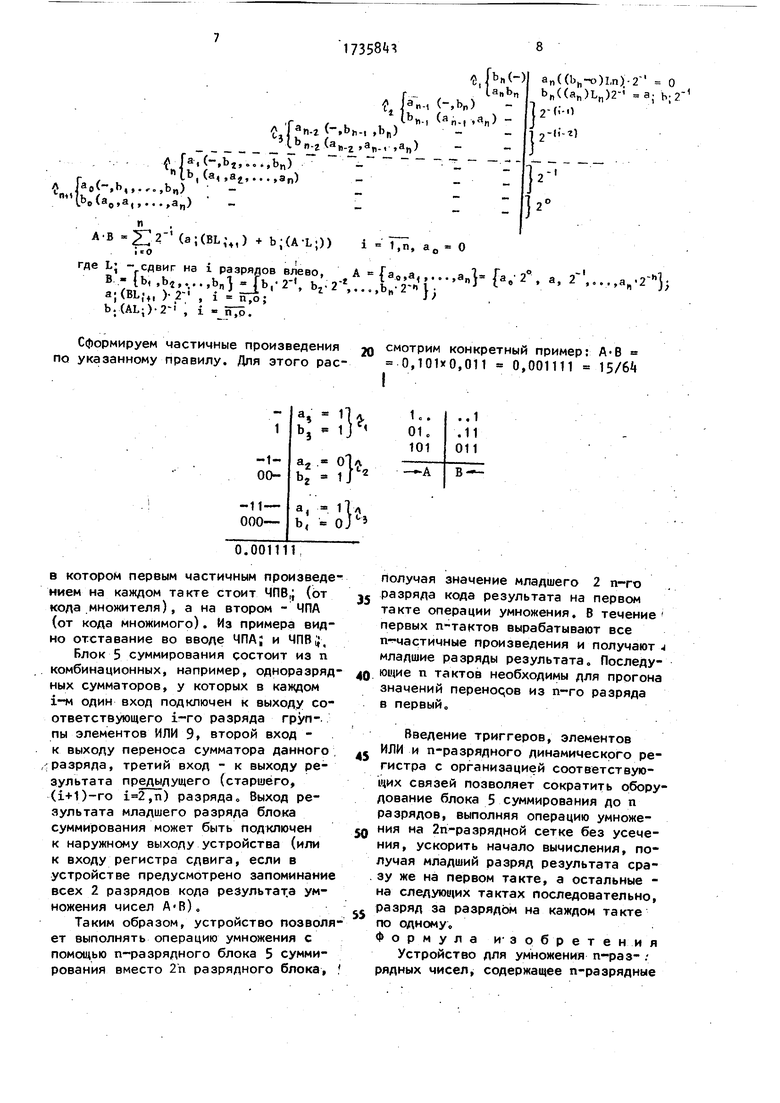

Устройство реализует новый алгоритм умножения чисел младшими разря- сс дами вперед. Запишем процедуру формирования частичного произведения от кода множимого (ЧПА;) и множителя (ЧПВ;) при умножении двух чисел А В в виде матрицы

IV, (а„., ,а„) 2 -li-1)

J2-KJ}

Л fan-2 Kb,-, ,bn) (a«-z,aB.,,aft)

Jai(Ь,o,,bn)-

nlb, (a4,at, ...,an)

Л jao(,,.т.,bn)-m lb0 a0,a,,...,an) nA-B -ZX (a;(BL, +,) b;(A-L;)) i « T,

;«o

где L; -сдвиг на i разрядов влево, А - {a,,a,,...,an}- a .-2°, a, ,... .a,,; В - lbi ,b4,v.,bnj ( 2- , Ьг.2-,...,Ь„-2--Ij a;(BL;4I ) Г1 , i - iT$;

b.(AL;)-2- , i пТБ.

Сформируем частичные произведения 20 СМОТРИМ конкретный пример: А-В по указанному правилу. Для этого рас- 0,101x0,011 0,001111 15/6

I

ianb

-,bn)

(а„., ,а„) )l an((bh-)Ln).-2- О | Ьп((аг1)Ьп)2-; а; Ь;2И

2 -li-1)

J2-KJ}

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1481744A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения двух @ -разрядных чисел | 1987 |

|

SU1439581A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения | 1989 |

|

SU1654815A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств универсальных и специализированных цифровых вычислительных машин Целью изобретения является сокращение аппаратурных затрат и повышение быстродействия. Устройство содержит регистры сомножителей 1,2, две группы элементов И 3,4, блок 5 суммирования, элемент НЕ 6, триггеры 7,8, группу элементов ИЛИ 9 и динамический регистр 10, Устройство реализует алгоритм умножения чисел, начиная с младших разрядов в прямом коде в соответствии с выражением А-В ;- (a4(BL;+1) + 1;(A L;)), i 1,п, А Г i1n где i l,n, A , а0...а„)п, В {b,,Ь,...bnj - разряды сомножителей, L - сдвиг влево. Коды сомножителей поступают последовательным кодом, частичные произведения и результат умножения формируются параллельным кодом. Результат произведения получается за 2п тактов. 1 ил. Q « (Л

}.

-1

, - OJ

«

0.001111

в котором первым частичным произведением на каждом такте стоит ЧПВ,| (от кода множителя), а на втором - ЧПА (от кода множимого). Из примера видно отставание во вводе ЧПА; и ЧПВ

Блок 5 суммирования состоит из n комбинационных, например, одноразрядных сумматоров, у которых в каждом i-м один вход подключен к выходу соответствующего 1-го разряда труп-, пы элементов ИЛИ 9, второй вход - к выходу переноса сумматора данного , - разряда, третий вход - к выходу результата предыдущего (старшего, (i+O-го ,n) разряда. Выход результата младшего разряда блока суммирования может быть подключен к наружному выходу устройства (или к входу регистра сдвига, если в устройстве предусмотрено запоминание всех 2 разрядов кода результата умножения чисел А«В).

Таким образом, устройство позволяет выполнять операцию умножения с помощью п разрядного блока 5 суммирования вместо 2п разрядного блока,

..1 .11 011

В

получая значение младшего 2 п-го . разряда кода результата на первом такте операции умножения. В течение первых n-тактов вырабатывают все n-частичные произведения и получают л младшие разряды результата. Последу- 0 ющие n тактов необходимы для прогона значений переносов из n-го разряда в первый.

Введение триггеров, элементов , ИЛИ и n-разрядного динамического регистра с организацией соответствующих связей позволяет сократить оборудование блока 5 суммирования до n разрядов, выполняя операцию умноже- « ния на 2п-разрядной сетке без усечения, ускорить начало вычисления, получая младший разряд результата сра- . зу же на первом такте, а остальные - на следующих тактах последовательно, разряд за разрядом на каждом такте по одному. Формула и-зобретения

Устройство для умножения п-раз- .- рядных чисел, содержащее п-разрядные

регистры первого и второго сомножителей, первую и вторую группу из п и п-1 элементов И соответственно и n-разрядный блок суммирования (п - разрядность сомножителей), причем выход 1-го разряда регистра первого сомножителя соединен с первым входом 1-го элемента И первой группы (i 1,.)v, выход j-ro разряда, регистра второго сомножителя соединен с первым входом j-ro элемента И второй группы (j 1,оо о,п-1), отличающееся тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия, в него введены элемент НЕ, два триггера, группа из п элементов ИЛИ, n-й элемент И второй группы и п-разрядный динамический регистр, выход 1-го разряда которого соединен с входами синхронизации 1-х разрядов ров первого и второго сомножителей, выход n-го разряда регистра второго сомножителя соединен с первым входом n-го элемента И второй группы, информационный вход первого триггера и информационный разрядный вход регистра первого сомножителя соединены с входом первого сомножителя устройства, вход второго сомножителя которого соединен с информационным разрядным входом регистра второго сомножителя и информационным входом второго триггера, выход которого соединен с вторыми входами п элементов И первой группы., выходы которых соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И второй группы, вторые входы которых соединены с выходом первого триггера, вход синхронизации которого соединен с входами синхронизации второго триггера и устройства, с третьими входами элементов И второй группы и входом элемента НЕ, выход которого соединен с третьими входами и элементов И первой группы, выход i-го элемента ИЛИ группы соединен с i-м входом п-раз- рядного блока суммирования, выходы которого соединены с выходами результата устройства.

| Устройство для умножения | 1987 |

|

SU1481744A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для умножения | 1984 |

|

SU1203512A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1992-05-23—Публикация

1989-06-05—Подача