мого кода Б дополнительный, управляющие входы которых соединены с входами знаков соответственно первых и вторых мко.имых ii множителей устройства, выходы первого и второго преобразователей прямого кода в дополнительный подключен соответственно к первой и второй группам входов третьего комбинационного сумматора, выходы (k+3) младших разрядов которого подключены к соответствующим входам первой группы входов (k+3) младших разрядов четвертого комбинационного сумматора, входы первой группы В.ХОДОВ (k-i-4)-ro и (k+5)-ro разрядов которого соединегпз с выходом старшего (k+4)-ro разряда третьего комбинационного сумматора, вторые входы разрядов четвертого комбинационного сумматора с второго по (k+3)-fi подключены к выходам (k,+2) младших разрядов регист

ра результата, вхопы которого подключены соответственно к выходам (k+3) младших разрядов и )-го разряда четвертого комбинационного сумматора, выходы (k+4)-ro и (k+5)-ro разрядов которого подключены соответственно к первому и второму входам второго регистра задержки, выходы которого соединены с входами сумматора в избыточной двоичной системе счисления, а третий и чет вертый входы подключены к выходам (К+3)-го и (k+4)-ro старших разрядов регистра результата, выход (k-f-4)-ro разряда которого соединен также с вторыми входами (К+4)-го и (К-Ь5)-го разрядов четвертого комбинационного сумматора, выходы сумматора в избыточной двоичной системе счисления являются выходами результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕНИЙ, содержащее регистры первого множимого и первого множителя, информационные входы кото рьк соединены с шинами соотве-рственно первого множимого и первого множителя устройства, а управляющие входы подключены к вьосодам регистра записи, сумматор в избыточной двоичной системе счисления, выходы которого яв ляются выходами устройства, первый блок элементов И, первые входы элемзн- тов И которого соединены с соответству- нишми вькоаами регистра первого множителя, и регистр результата о т л и - ч а ю ш ее с я тем, что, с целью упрощения и расширения его функдионапьньрс возможностей, заключающегося в получении суммы двух провзведений, оно содержит первый, второй, третий и 4eiv вертый комбинационнью суммато|хы, регистры второго множимого и второго множителя, второй I третий и четверггый блоки элементе И первый и второй преобразователи прямого кода в аопош{ительнь1Й, первый и второй регистры зацегмаси, причем первый и второй входы первого регистра задержки соединены с входами соответственно первого и второго множителей устройства, первые входы элементов И второго и третьего блоков соединены с соответствующими выходами регистров соответственно первого и второго множи- мьк, а первый и второй выходы первого регистра задержки подключены к вторым входам элементов И соответственно второго и третьего блоков элементов И, вторые входы элементов И первого блока элементов И соединены с юродом пе{ вого множимого устройства, вход второго множимого которого подключен к информацисжному входу регистра второго множимого, первые входы элементов И чет. вертого блока элементов И соединены с (Л выходами регистра второго множителя, вход второго множимого устройства подключен к вторым входам четвертого блока элементов И, информационный вход регистра второго множителя подключен к входу второго множителя устройства, а управляющие входы соединены с управля- ющими входами регистра второго множиК9 мого и подключены к выходам регистра О 00 записи, выходы элементов И первого и третьего блоков элементов И соединены с соответствующими входами первсй груп00 пы младших разрядов соответственно первого и второго комбинационных сумматоров, входь вторых групп разрядов которых с второго по (k+l)- (k-разрядность операндов) подключены к соответствующим выходам элементов И соотве ственно второго и четвертого блоков элементов И, а выходы первого и второго комбинационных сумматоров подключены к информационным входам соответственно первого и второго преобразователей пря

1

Изобретение относигся к цифровой вьь. числительной технике и может быть исползовано при построении специализированных вычислительных систем.

Известно устройство для вычисления сумм произведений, содержашее два сумматора, регистры разности и суммы, блоц коммутаторов, регистры хранения частич ного результата и многовходовой сумма-

тор 5 .;

Это устройство работает в избыточной двоичной системе счисления и требует преобразования множимых визбыточный овошшый код, а множителейВ код, со-

держащий только 1 или 1, что яйляется недостатком устройства.

Наиболее близким к предлагаемому является устройство для умножения, со-) держащее регистр множимого и регистр множителя, входы которых являются

входами множимого и множителя устройства, а выходы подключены к первым и вторым входам блока элементов И, выходы которого соединены с информационными входами коммутатора, управляющие входы которого подключены к выходу блока анализа знака, входы которого явпяких;я входами множимого и множителя устройства, выходы коммутатора соединены с первой группой входов многовхоцо- вого сумматора в избыточной двоичной системе счисления, вторая группа входов

и выходы которого соединены соответ ственно с выходами и входами первого и второго регистров результата, и регистр записи, выходы которого подключены к управляющим входам регистра множителя 2 .

Недостатком устройства является сложность алгоритма умножения, что требует больших аппаратурных затрат, и получение только произведения двух чисел.

Цель изобретения - упрощение устройства и расширение функциональных возможностей, заключающееся в получении суммы двух произведений.

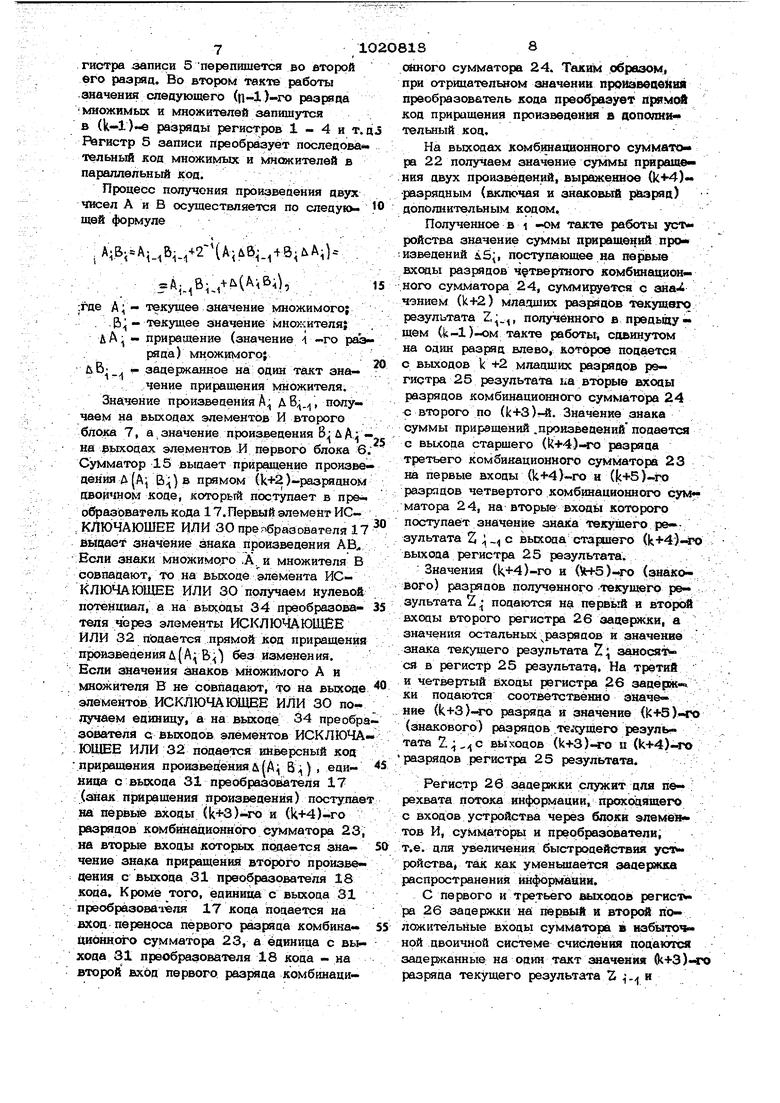

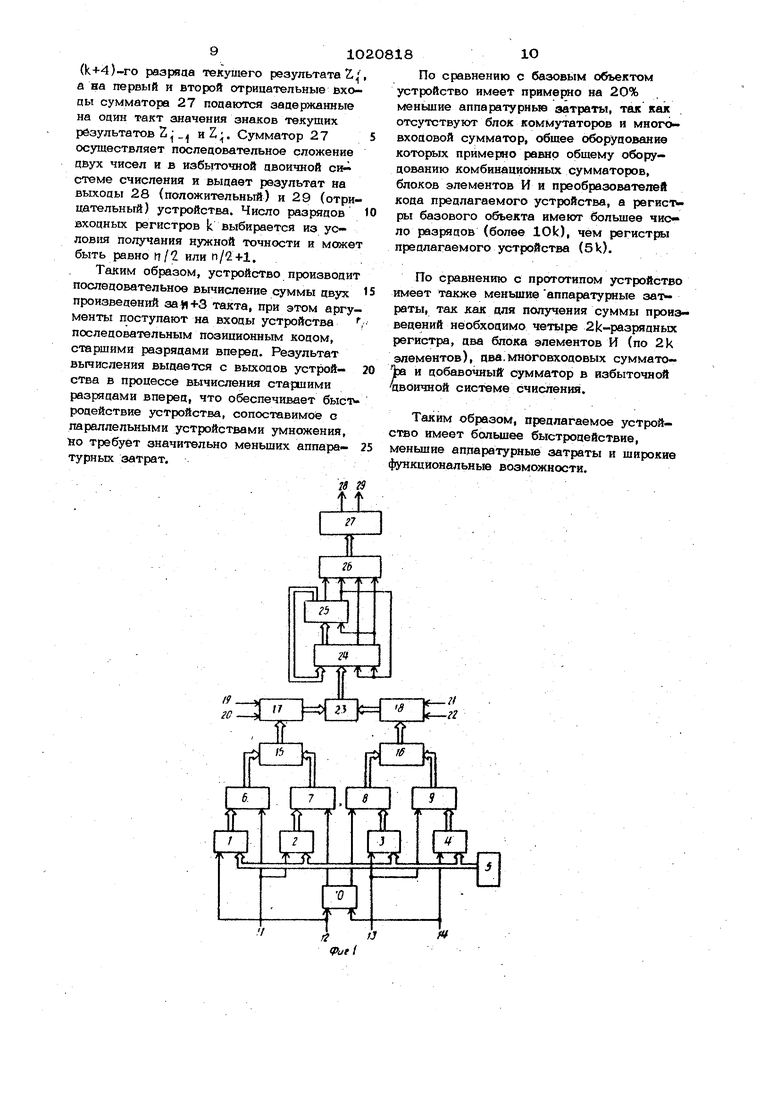

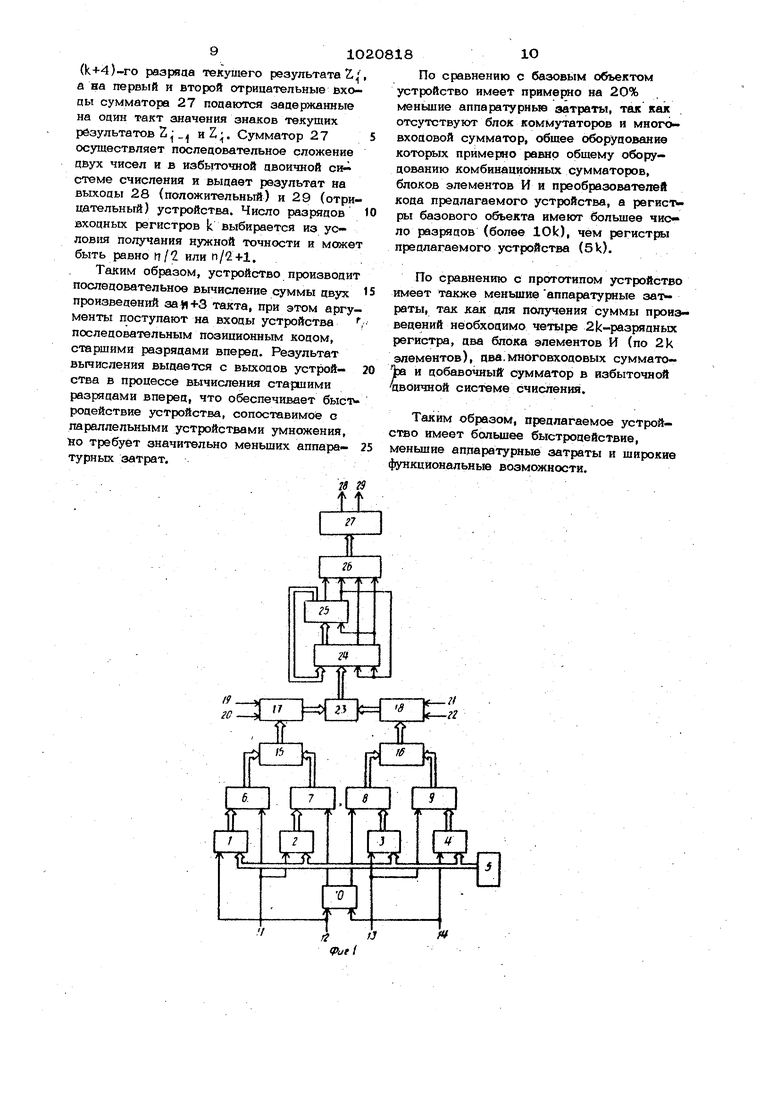

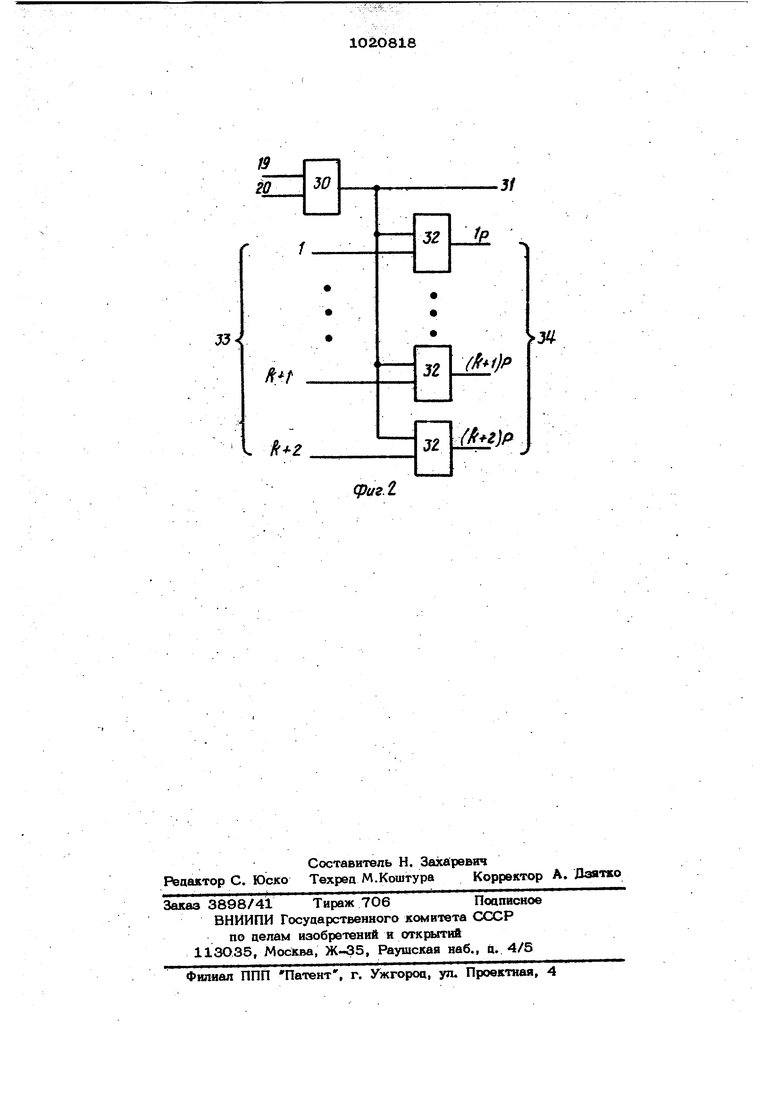

Для достижения поставленной цели устройство для вычисления сумм произведений, содержащее регистры первого множимого и первого множителя, информационные входы которых соединены с шинами соответственно первого множимого и первого множителя устройства, а управляющие входы подключены к выходам регистра записи, сумматор в избыточной двоичной системе счисления, выходы которого являются выходами устройства, первый блок элементов И, первые входы элементов И которого соединены с соответствующими выходами регистра первого множителя и регистр результата, содержит первый и второй (k+1-разрядные) комбинационные сумматоры, третий (k+4-разрядный) комбинационный сумматор, четвертый (k+ 5 -разрядный) комбинационный сумматор, регистры второго множимого и второго множителя, второй, третий и четвертый блоки элементов И, первьгй и второй преобразователи прямого кода в дополнительный, первый и второй регистры задержки, причем первый и второй входы регистра задержки соединены с входами соответственно первого и второго множителей устройства, первые входы элементов И второго и третьего блоков соединены с соответствуюШйми выходами регистров сортветственйо первого и второго множимыя;, а первый и второй выход netpBoro {регистра задержки подключены к вторым входам элементов И соотверственно второго и третьего блоков элеме тов И, вторые входы элементов И niepBor 6noJKa элементов И соединены с вхсиюм первого множимого устройства, вход второго множимого кото{)ого подключен к ин формационному входу регистра второго множимого, первью входы элементов И четвертого блока элементов соединены с выходами регистра второго множителя, вход второго множимого устройства подключен к вторым входам элементов И четвертого блока, информационный кход регистра второго множителя подключен ,к входу второго множителя устройства, а управляющие входы соединены с управляющими входами регистра второго , множимого и подключены к выходам регистра записи, выходы элементов И первого и третьего блоков элементов И сое- пинены с соответствующими входами первой группы k младших разрядов соответственно первого и второго комбинационных сумматоров, входы вторых групп разрядов которых с второго по (k+l)-fi (k-раэрядность операндов) подключены к с оогветсгвующим выходам элементов И соответсгвенно второго к четвертого блоков элементов И, а выхо ВЫ первого и второго комбинационных J.nCJV/« V Л fft., J A.4/JVJ4/riJlC«.I nV/nn О1Л. сумматоров подключены к информационным входам соответственно первого к вто рого преобразователей прямого кода в дополнительный, управляющие входы которьрс соединены с входами знаков соответственно) первых и вторых множимых и множителей устройства, вьгходы первого И второго преобразователей прямого кода в пополнительный подключены соответстве но к первой и второй группам входов тре тьего комбинационного сумматора, выход младших (k+3) разрядов которого подкл чены к соответствующим входам первой .группы входов младших (k-f3) разрядов. етвертого комбинационного сумматора, хоаы первой группы входов (k+4).o и ()-го раэряцов которого соединены выходом старшего (К+4)-го раэряаь третьего комбинационного сумматора, вторые вхоцы раэряцов четвертого комбинационного сумматора с второго по (k+S)-и подключены к выходам (k+2) младших разрядов регистра результата, входы которых подключены соответственно к выходам (k+3) младших разрядов и (k+5)-ro разряда четвертого комбинационного сумматора, выходы (kM)-ro и {k-f5)-ro разрядов которого подключены соответ- ственно к первому и второму входам второго регистра задержки, выходы которого соединены с входами сумматора в избыточной двоичной системе исчисления, а третий и четвертый входы подключены к выходам )-го и (k+4)-ro старших разрядов регистра результата, выход (К 4)-го разряда которого соединён также о вторыми входами {k+4)-го и (k+5)-ro разрядов четвертого комбинационного сум- матора, выходы сумматора в избыточной двоичной системе счисления являются выхо- дами результата устрсйства. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - пример выполнения преобразователя прямого кода в дополнительный. Управляющие входы регистров первого множителя 1, первого множимого 2, второго множимого 3 и второго множителя 4 объединены и подключены к выходам регистра 5 записи, а их разрядный выходы соединены с первыми входами соц ответственно первого, второго, третьего и четвертого блоков элементов И 6 - 9,;. вторые входы второго и третьего блоков элементов И 7 и 8 подключены ссютвет сгвенно к первому и второму выходам первого регистра 10 задержки, вход 11 первого множимого устройства подключен к вто- . рым входам элементов И первого блока элементов И 6 и к информационному входу регистра первого множимого 2, вход 12 первого множителя устройства соединен с информационным входом ре- гистра первого множителя 1 и с первым входом первого регистра 10 задержки, второй вход которого соединен с информач -ционным входом регистра второго множи- теля 4 и с входом 13 второго множителя устройства, вход 14 второго множимого которого подключен к информационному входу регистра второго множимого 3 ик вторым входам элементов И четве того блока элементов И 9, выходы элементов И первого и третьего блоков элементов И 6 и 8 соединены с первыми вхоааии k млацших разрядов соответствен но nepBOix) и второго комбинационных сумматоров 15 и 16, вторые ккоаы разрядов которых с второго по ()-й подключены к выходам элементов И соотв ственно второго и четвертого блоков элементов И 7 и 9, а liDc разрядные выходы соединены с информационными входами соответственно первого и второго преобразователей 17 и 18 прямого кода в дополнительный. Управляющие входы перв го преобразователя 17 кода подключены к входам 19 и 2О знаков первого множимого и первого множителя устройства, а управляющие входы второго преобразователя 18 кода подключены к входам 21 и 22 знаков второго множимого и второго множителя устройства. Выходы преобразователей 17 и 18 кода соединены соответственно с первыми и втоушгми разрядными входами третьего комбинацио ного сумматора 23, выходы k+3 младших разрядов которого подключены к первым входам k +3 младших разрядов четвертого комбинационного сумматора 24, первые входы (k+4)ro и (k+5)-ro разрядов которого соэцинены с выходом старшего (k+4)ro разряда третьего комбинационного сумматора 23. Вторые входы разрядов четвертого комбинационного сумматора 24 с второго по {k+3)«ft подключены к выходам k +2 младших раэ. рядов регистра 25 результата, выход (k + 4)-го разряда которого соединен с вторыми входами (k+4)-ro и ( )-го разрядов четвертого комбинационного сумматора 24 и с вторым входом второго регистра 26 задержки, первый вход которого соещшен с выходом (k+3)ro разряда регистра 25 результата, входы k -ЬЗ младших разрядов которого соединены с выходами k +3 младших разрядов че-гвертого комбинационного сумматора 24, выход (k-M)-го разряда которого соединен с третьим входом второго регист ра 26 задержки, четвертый вход которого подключен к входу ()(+4)-го разряда регистра 25 результата.и к выходу ()-r разряде четвертого комбинационного сумматора 24. Первый и третий выходы втсм рого регистра 26 задержки соединены со. ответственно с первым и вторым положительными входами сумматора 27 в избыточной двоичной системе счисления, выходы которого являются выходами 28 И 29 результата устройства, а первый и второй отрицательные входы подключе1гы соответственно к второму и четвертому выходам второго регистра 26 задержки. Преобразователи 17 и 18 прямого кода в дополнительный содержат по (k+3) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Входы пер- . вого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 (выход которого соединен с первым выходом 31 преобразователя) соединены с управляющими входами 19 и 20 преобразо вателя, первый выход которого подключен к выходу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ ЗО и к первым входам остальных (k+2) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 32, вторые входы которых являются информационными входами 33 преобразователя, выходы 34 которого с второго по (и+3)-й подключены к выходам элементов ИСК ЛЮЧАКШЕЕ ИЛИ 32. Выходы 34 первого и второго преобразователей кода 17 и 18 подключены соответственно к первым и вторым входам k +2 младших .разрядов третьего комбинационного сумматора 23, первые входы (k+3)-ro и (k+4)-ro разрядов которого соединены с его ЕОСОДОМ переноса разряда и подключены к первому выходу первого преобразователя кода 17, а первый выход 31 второго преобразователя 18 кода подключен к вторым входам ()ro и (k +4 )-го разрядов третьего комбинационного сумматора 23 и к второму входу первого разряда четвертого комбинационного сумматора 24 (не показан). Устройство работает следующим образом.. . В начале каждого цшша вычислений регистры 2 и 3 множимых, регистры 1 и 4 множителей, регистр 25 результата, второй регистр 26 задержки сбрасыва- ются в нулевое состояние (цепь сброса на чертеже не показана). Одновременно в первый (младший) разряд регистра 5 записи записьшается единица. В результате в начале первого такта работы.устройств ва на управляюш ие входы k -го старшего разряда регистров 2 и 3 множимых и регистров 1 и 4 множителей поступает сигнал разрешения записи. Значения стар шего п -го разряда множимых, и множителей, поступающих последовательным позиционным кодом на входы 11-14 устройства, на первом такте запишутся Bk-« старшие разряды регистров 1-4 и, кроме того, эначення г) -го разряда множителей запишутся в регистр 10 задержки. Единица из первого разряда регистра .записи 5 перепишется во второй его разряд. Во втором такте работы значения следующего (tl-i)-ro разряда МНОЖИМЫХ и множителей запишутся в (k-l)-e разряды регистров 1 - 4 и т.д Регистр 5 записи преобразует последова тельный код множимых и мнонсителей в параллельный код. Процесс получения произведения дв чисел А и В осуществляется по следук. щей формуле .A.B-A.,B.,- 2-nAi B.,)- ; ,iB-,,+ (MBi),; тде А; - текущее значение множимого; . g) - текущее значение мнох-:ителя} д А - приращение (значение -i -го раз ряда) множимого; Г) UD , - задержанное на один такт значение приращения множителя. Значение произведения А дВ., получаем на выходах элементов И второго блока 7, а значение произведения 8 дД - на эыхоаах элементов И первого блока 6 Сумматор 15 выдает приращение произве дения д|А ) в прямом (k-i-2)-рвзрядном дво 1чном коде, который поступает в пре образрватель кода 1 Т.ПервыЙ элеменг ИС- „ КЛЮЧАЮШЕЕ ИЛИ 30 пре.рааователя 17 выдает значение знака произведения АВ Воли знаки множимого ,А. и множителя В совпадают, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ ЗО получаем нулевой потенциал, а на выходы 34 прёобразователя через элементы ИСКЛЮЧАЮЩЕЕ Или 32 подается прямой код приращения произведенияд|А Б) без изменения. Если значения знаков множимого А и множителя В не совпадают, то на выходе элементов ИСКЛЮЧАКЩЕЕ ИЛИ ЗО подучаем единицу, а на выходе 34 преобр зователя с выходов элементов ИСКЛЮЧА ЮЩЕЕ ИЛИ 32 подается инверсный код приращения произвеценияд(А В) , единица с выхода 31 преобразователя 17 (знак приращения произведения) поступае на nepBbie входы ()Hro и (k-«-4)rro разрядов комбина дионн6го сумматора 23 на вторые входы которых псздается значение знака приращения второго произведения с выхода 31 преобразователя 18 кода. Кроме того, единица с выхода 31 преобразова1еля 17 кода подается на вход переноса первого разряда комбинаitHoiiHoro сумматора 23, а единица с выхода 31 преобразователя 18 кода - на второй вход первого разряда комбинацийного сумматора 24. Таким образом, ри отрицательном значении произвеоеМия реобразователь кода преобразует пртмой од приращения произведен в аопопни- ельный код. На выходах комбинационного сумматора 22 получаем значение суммы прираше- ня двух произведений, выраженное ()«. разрядным (включая и знаковый р1заряд) дополнительным кодом. Полученное в 1 -ом такте работы устройства значение суммы приращений про-. изведений iSj, поступающее на первые входы разрядов четвертного комбин ихиОн- ного сумматора 24, суммируется с ана -знием (k42) младщих разрядов текущего результата Z,,, полученного в предыду щем Ck-l)-OM такте работы, сдвинутом на один разряд влево, которое подается с выходов k +2 младщих разрядов регистра 25 результата ьа вторые входы разрядов комбинационного сумматора 24 с второго по (k+3)r4i. Значение знака суммы приращений .произведений подается с вывода старшего (k+4) разряда третьего комбинационного сумматора 23 на первые входы (kMy-ro и (k+5)-t4 разрпцов четвертого комбинационного сумматора 24, на вторые входы которого поступает значение знака ре-зультата 21 - с выхода старшего (k+4)HPO выхода регистра 25 результата.: Значения (k+4)-ro и (5)-го (знакового) разрядов полученного текущего результата 2 .j подаются на первый и второй входы второго регистра 26 задержки, а значения остальных разрядов и значение знака текущего результата 7, заносят ся в регистр 25 результата. На третий и четвертый Ёходы регистра J26 зацерж- ки подаются соответственно значение (k.+3)-ro разряда и значение {(i-J-S)-ro (знакового) разрядов .те.сушего результата 2.4 - с выходов (k-t-3)o п ()-гo разрядов регистра 25 результата Регистр 26 задержки служит для перехвата потока информации, проходящего с входов устройства через блоки элемён тов И, суМматорш и преобразователи, т.е. для увеличения быстродействия усч ройства, так как уменыоается заде1 кка распространения информааня. С первого и третьего шлходов регистр. ра 26 задержки на первый н второй положительные входы сумматора & избыто нрй двоичной системе счиЬления подаюпгся задержанные на один такт а«ачения ()-ro разряда текущего результата Z -. и ()-го разряца текущего результата 2г| а на первый и второй отрицательные входы сумматора 27 подаются задержанные на оцин такт значения знаков текущих результатов aZ. Сумматор 27 осуществляет последовательное сложение двух чисел и в избыточной двоичной ctf стеме счисления и выдает результат на выходы 28 (положительный) и 29 (отрицательный) устройства. Число разрядов входных регистров k выбирается из ус ловия получания нужной точности и может быть равно fill илип/2+1, Таким образом, устройство производит последовательное вычисление суммы двух произведений такта, при этом аргументы поступают на входы устройства последовательным позиционным кодом, старшими разрядами вперед. Результат вычисления выдается с вьгходов устройства в процессе вычисления старшими разрядами вперед, что обеспечивает быстродействие устройства, сопоставимое с параллельными устройствами умножения, но требует значительно меньших аппаратурных затрат. 10 18 По сравнению с базовым объектом устройство имеет примерно на 20% , меньшие аппаратурные затраты, так как отсутствуют блок коммутаторов и многовходовой сумматор, общее оборудование которых примерно равно общему оборудованию комбинационных сумматоров, блоков элементов И и преобразователей кода предлагаемого устройства, а регистры базового объекта имеют больщее число разрядов (более 10k), чем регистры предлагаемого устройства (5k). По сравнению с прототипом устройство имеет также меньшие аппаратурные зарраты, так как для получения суммы произведений необходимо четыре 2k-paзpядныx регистра, два блока элементов И (по 2k элементов), два.многовходовых сумматоЪа и добавочный: сумматор в избыточной оичной системе счисления. Таким образом, предлагаемое устройтво имеет большее быстродействие, еньшие аппаратурные затраты и широкие ункциональные возможности.

/

30 20

33 4

L

.31

yi(1)P

зг

(f(

32

(риг. I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Уплотнение вала | 1989 |

|

SU1672061A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-05-30—Публикация

1982-02-17—Подача