(54) КОДОУПРАВЛЯЕМЫЙ ЭЛЕМЕНТ СЕТОЧНОЙ МОДЕЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Управляемый элемент сеточной электро-МОдЕли | 1979 |

|

SU822217A1 |

| Узел резистивной сеточной модели | 1982 |

|

SU1070558A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2012 |

|

RU2498456C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ (ВАРИАНТЫ) | 2011 |

|

RU2465684C1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для выборки информации из матричного накопителя | 1982 |

|

SU1073796A1 |

| Кодоуправляемый элемент сеточной модели | 1975 |

|

SU547790A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано в специализированных аналоговых вычислительных машинах, в сеточньдх моделях. 5

Известен кодоуправляемый элемент, содержащий блок проводимостей, программный и управляющий блоки, память/ /.

Наиболее близким по техническому10 решению является кодоуправляемый,элемент сеточной модели, содержащий программный блок, блок проводимостей, выход которого подключен к блоку усилителей, выход которого соединен со 5 входом блока коррекции управляющих сигналов, выход которого подключен к первому входу блока формирования управляюьщх сигналов/27.

Недостаток известных кодоуправляе-20 мых элементов заключается в ограниченной точности задания значений весов сопротивлений для магазинов проводимостей в конце диапазона, для магазинов сопротивлений в начале диапазона.25

Цель изобретения - повыиение точности элемента сеточной модели.

С этой целью в кодоуправляемый элемент сеточной модели введены регист; памяти, элемент памяти, два дешифра- зо

тора, при зтом первый выход программного блока подключен к первому входу регистра памяти, второй вход которого соединен с первым выходом первого дешифратора, второй выход которого подключен к первому входу элемента памяти, второй вход элемента памяти соединен со BTOJWM выходом программного блока, третий выход которого подключен ко входу первого дешифратора. Выходы регистра памяти и элемента памяти соединены соответственно с перBbw и вторым входами второго дешифратора, выход которого подключен ко второму входу блока формирования управляющих сигналов, выходы которого соединены с соответствующими управляющими входами блока проводимостей.

Кроме того, блок проводимостей содержит три группы МДП-транзистороя , при этом в каждом разряде, кроме первого, исток МДП-транзистора первой группы объединен с одним из выводов разрядного резистора и подключен к стокам МДП-т1)анзисторов первой и второй группы предыдущего разряда, в первом разряде исток МДПтранзйстора объединен с одним из выводов разрядного резистора и являет|ся входом блока проводимостей, 11ругой

748446

вывод разрядного резистора объединен с истоком МДП-транзистооа тюетьей .и прдк люч ен к ис ток у МДП - тра и зйстрра второй группы последующего разряда, стоки всех МДП-транзисторов третьей группы и стоки МДП-транзисторов первой и второй группы объединены и являются выходом блока прО водимостей, затворы МДП-транзисторов всех групп являются соответствующими управляющими входами блокоВпроводимое тей.

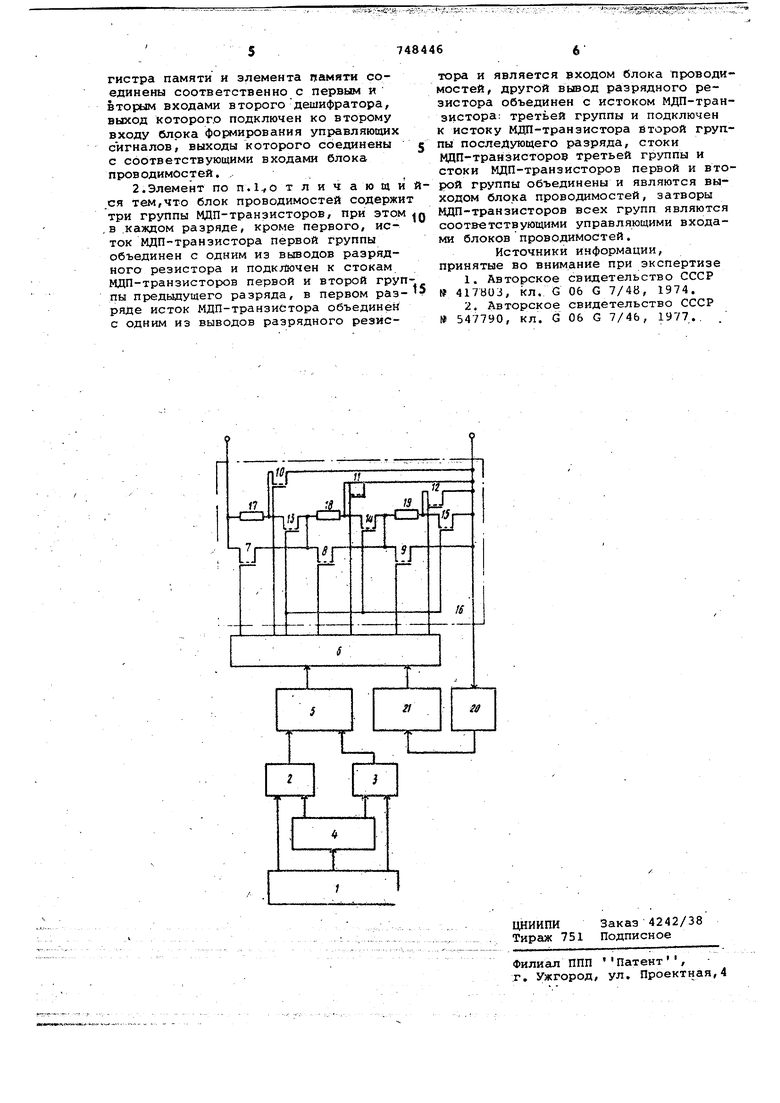

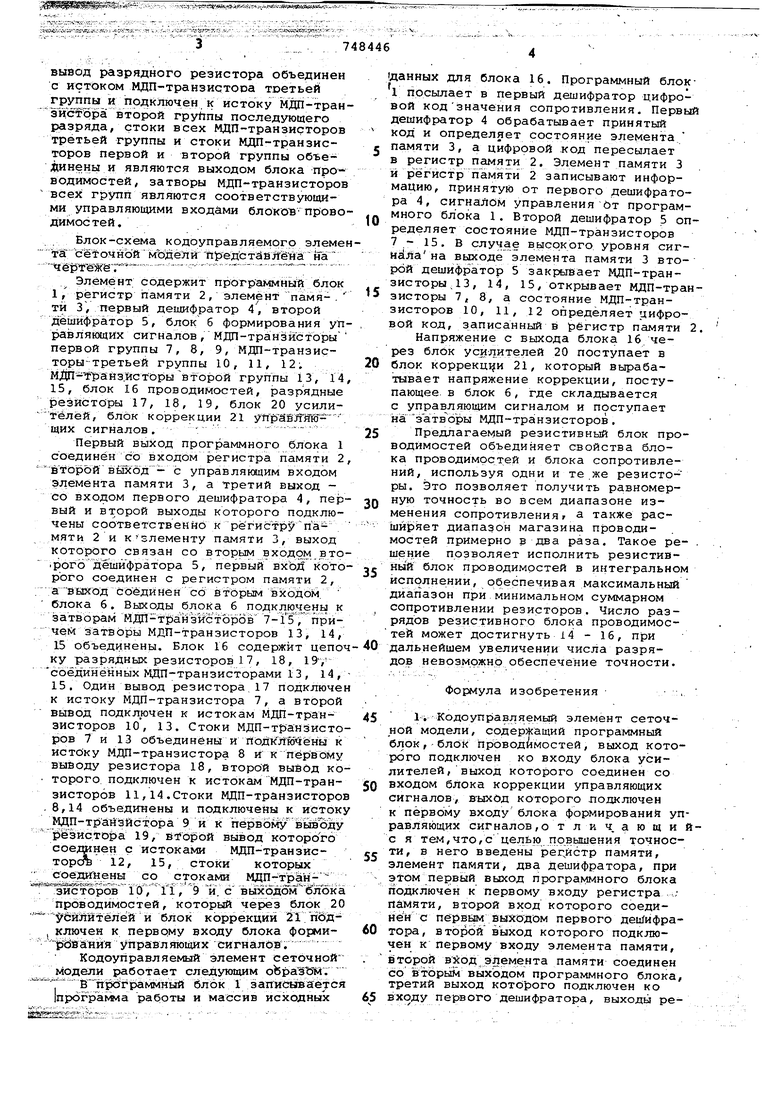

Блок-схема кодоуправляемого элемента: сеточной мЪдели п редставяена на чертеже. .-.„--.

Элемент содержит программный блок 1, регистр памяти 2, элемент памя- . ти 3, первый дешифратор 4, второй дешифратор 5, блок б формирования ytiравлякхцих сигналов , МДП-тран й сторы первой группы 7, 8, 9, МДП-транзисторы-третьей группы 10, 11, 12; мДП- райз;йсторы второй группы 13, 14, 15, блок 16 проводимоетей, разрядные резисторы 17, 18, 19, блок 20 усилиТёлёй, блок коррекции 21 уИрЙвЛяю- -. щих сигналов, -- - --;

Первый выход программного блока 1 соединён со входом регистра памяти 2, второй с управляющим входом элемента памяти 3, а третий выход со входом первого дешифратора 4, первый и второй выходы которого подключены соответственно к рёгистр п а- . мяти 2 и кэлементу памяти 3, выход которого связан со вторым входом вто.рогодешйфратора 5, первый вхЬд Которого соединен с регистром памяти 2, :а выхс|Д соединен со вторым входом/ блока 6. Выходы б.лока 6 подключены к затворам МДЙ-тгранзШтбров 7-15 , гтрйчей затворы МДП-транзисторов 13 14, 15 объединены. Блок 16 содержит цепочку разрядных резисторов 1 7 , 18, 19, соёдинённых мДП-транзисторами 13, 14,15. Один вывод резистора 17 подключен к истоку МДП-транзистора 7, а второй вывод подключен к истокам МДП-транзисторов 10, 13. Стоки МДП-транзисторов 7 и 13 объединены и йОдкЛШёны к истоку МДП-транзистора 8 и к первому выводу резистора 18, второй вывод которого подключен к истокам МДП-транзисторов 11,14.Стоки МДП-транзисторов . 8,14 объединены и подключены к истоку МДП-транзйстора 9 и к первомувыводу 1 ёзйстоЁ)а 19, вывод которого соедшнен с истоками МДП-транзисторот 12, 15, стоки которых соединены со стоками МДП- тр&н- llHCTopSB I0r ll7 9 vi. с В1аходо1и й11ока прбводймостей, который через блок 20 ййййтёлей и блок коррекции 21. подключен к первому входу блока форми- Ьванйя управляющих сигналив.

Кодоуправляемый элемент сеточной модели работает следующим оЬразШ.

В п р 5гр1аммный блок 1 зап исыва ё ся

InporpaNivia работы и массив исходных

данных для блока 16. Программный блок1 посылает в первый дешифратор цифровой кодзначения сопротивления. Первый дешифратор 4 обрабатывает принятый

код и определяет состояние элемента памяти 3, а цифровой .код пересылает в регистр памяти 2. Элемент памяти 3 и р ёгистр памяти 2 записывают информацию, принятую от первого дешифратора 4 , сигналом управления йт програм ° ° блока 1 . Второй дешифратор 5 определяет состояние МДП-транзисторов 7-15. В случа§ высокого уровня сигИг1лана выходе элемента памяти 3 второй дешифратор 5 закрывает МДП-транзисторыЛЗ, 14, 15, открывает МДП-транзисторы 7, 8, а состояние МДП-транзисторов 10, 11, 12 определяет цифровой код, записанный в регистр памяти 2.

Напряжение с выхода блока 16 через блок усилителей 20 поступает в

блок коррекщ и 21, который вырабатывает напряжение коррекции, поступающее, в блок 6, где складывается с управ ляющим сигналом и поступает йа затворы МДП-транзисторов.

Предлагаемый резистивный блок проводнмостей объединяет свойства блока проводимрстей и блока сопротивлений, используя одни и те .же резисторы. Это позволяет получить равномерную точность во всем диапазоне изменения сопротивления г а также расшйряет диапазон магазина проводимостей примерно в два раза. Такое ре- . шен.ие позволяет исполнить резистивйый блок проводимрстей в интегральном

исполнении, рбеспечивая максимальный диапазон при минимальном суммарном сопротивлении резисторов. Число разрядов резистивного блока проводимостей может достигнуть 14 - 16, при дальнейшем увеличении числа разрядов невозмржнр обеспечение точности.

Формула изобретения :,

1 i Кодоуправляемьзй элемент сеточной модели, содержащий программный блок,-блок проводимостей, выход которого подключен ко входу блока усилителей, выход которого соединен со

входом блока коррекции управляющих сигналов, выхОд которого подключен к первому входу блока формирований управляющих сиг налов, о т л и ч, а ю щ и йс я тем,что,с целью првьшения точности, в него введены памяти, элемент памяти, два дешифратора, при этом первый выход прюграммного блока подключен к первому входу регистра ; памяти, второй вход которого соединён с первым выхоДом первого деи ифратора, второй выход которого подключен к первому входу элемента памяти,

втррой в:йод элемента памяти соединен со BTOpfcjM выходом программного блока, третий выход которого подключен ко

входу первого дешифратора, выходы ре5

гистра памяти и элемента памяти соединены соответственно с первым и вторым входами второго дешифратора, выход которого подключен ко второму входу блока формирования управляющих сигналов, выходы которого соединены с соответствующими входами блока проводимое т ей, ,.

тора и является входом блока проводимостей, другой вывод разрядного резистора объединен с истоком МДП-транзистора; третьей группы и подключен к истоку МДП-транзистора второй группы последующего разряда, стоки МДП-транзисторов третьей группы и стоки МДП-транзисторов первой и второй группы объединены и являются выходом блока проводимостей, затворы МДП-транзисторов всех групп являются соответствующими управляющими входами блоков проводимостей.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-07-15—Публикация

1978-05-16—Подача