(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП ТРАНЗИСТОРАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU842964A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Постоянное запоминающее устройство | 1988 |

|

SU1594603A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU731474A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

I

Изобретение относится к автоматике и вычислительной технике.

Известны динамические запоминающие устройства, содержащие матрицу четырехтранзисторных запоминающих элементов с транзисторами предварительного заряда , столбцов и выходными вентильными тран.зисторами столбцов, дешифраторы строк и столбцов, каждый выход которых соединен с соответствующей HIHHOII строки или столбца через вентильный транзистор и буферную ячейку, инверторы кода адреса, логические схемы I .,

Недостатком TBKVIX запоминающих устройств является необходимостьпермодического прерывания обращений к запоминающим устройствам (на 32-64 за каждые 1-2 мс для проведения регенерации информации во всех запоминающих элементах).

Такие прерывания приводят к потере машинного времени.

Наиболее близким к данному техническому рещению является оперативное запоминающее устройство (ОЗУ), выполненное с использованием МДП-транзисторов, содержащее матрицу четырехтранзисторных запоминающих элементов, адресные входы коEJ i j J -- --.----.-J,v.v-... vai..,.,.. .--.- .,:,„

.....,,..., - r - й;-lйs йз ; ; ™ч.,

торых в строках, а разрядные - в столб. цах, соответственно объединены, при этом разрядные входы соединены соответственно со стоками выходных вентильных транзисторов столбцов и истоками транзисторов предварительного заряда столбцов, причем стоки последних соединены с тиной питания, истоки выходных вентильных транзисторов столбцов соединены соответственно с разрядными йшнами устройства, а затворы - соответственно с истоками буферных транзисторов разрядных формирователей, затворы которых соединены соответственно с истоками входных вентильных транзисторов разрядных, формирователей, стоки входных вентильных транзисторов разрядных формирователей соединены с соответствующими

выходами дещифратора столбцов, входы которого соединены с соответствующими выходами блоков формирования прямого и ииверсного кода адреса, дешнфратор строк, входы которого соединены, с соответствую2Q щимн выходами блоков формирования прямого и инверсного кода адреса, а выходы - соответственно со стоками входных вентильных транзисторов адресных формирователей, истоки входных вентильных транзисторов

адреспых формирователей соединены соответственно с затворами буферных транзисторов адресных формирователей, причем входы всех блоков формирования прямого и инверсного кода адреса соединены с соответствующими входными шинами кода адреса устройства 2.

Такое устройство также обладает недостаточным быстродействием.

Цель изобретения - повышение быстродействия ОЗУ.

Для достижения указанной цели устройство дополнительно содержит транзисторы предварительного разряда строки, истоки которых соединены с шиной нулевого потенциала, затворы - с затворами транзисторов предварительного заряда столбцов и с вы: ходом элемента ИЕ-ИЛИ, а стоки - соответственно с истоками двух выходных вентильных транзисторов адресных формирователей в каждом адресном формирователе, причем сток и затвор первого выходного вентильного транзистора в каждом адресном формирователе соединен соответственно с истоком и стоком буферного транзистора, а сток и затвор второго выходного вентильного транзистора - с истоком и стоком дополнительного буферного транзистора, затвор которого соединен в каждом адресном формирователе с истоком дополнительного входного вентильного транзистора, сток дополнительного входного вентильного транзистора в каждом адресном формирователе соединен с соответствующим выходом дешифратора строк, причем первая и вторая шины импульсного питания устройства подключеныко входам элемента ИЛИ, выход которого соединен со входами импульсного питания дешифраторов строк и формирователя прямого и инверсного кода адреса, третья -шина - к первому входу элемента НЕ-ИЛИ, к затворам входных вентильных транзисторов адресных и разрядных формирователей и стокам дополнительных буферных транзисторов адресных формирователей, а четвертая шина - ко второму входу элемента НЕ-ИЛИ, стокам буферных транзисторов адресных и разрядных формирователей и затворам дополнительных входных вентильных транзисторов адресных формирователей.

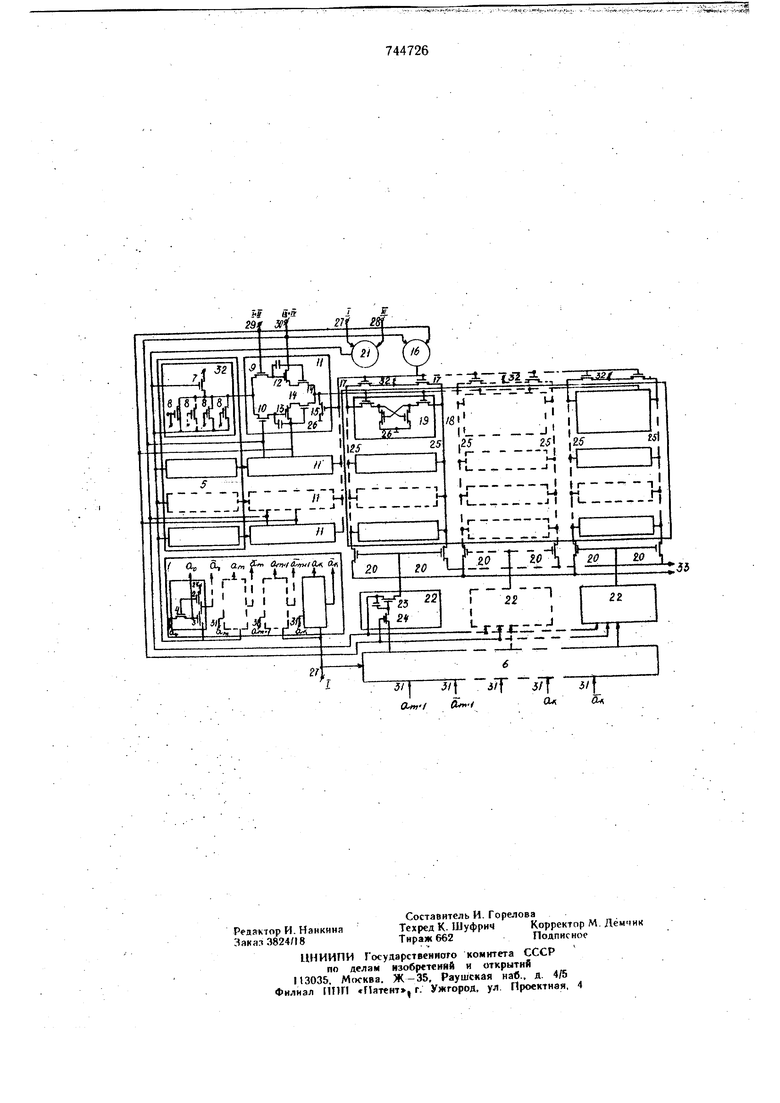

На чертеже изображена функциональная блок-схема оперативного запоминающего устройства на МДП-транзисторах.

Устройство содержит блок 1 формирования прямого и инверсного кода адреса; нагрузочные транзисторы 2, связанные с ним вентильный транзистор 3 и стробирующий транзистор 4. К блоку I подключены дешифратор 5 строк и дешифратор б столбцов, деигифратор 5 строк включает нагрузочный транзистор 7 и соединенные с ним вентйЛьиые транзисторы 8, с которыми связаны входные вентильные транзисторы 9 и дополнительные входные вентильные транзисторы 0 адресных формирователей И, которые также вгслючают буферные транзисторы 12 и дополнительные буферные транзисторы 13, соединенные через выходные вентильные транзисторы 14 с транзисторами 15 предварительного разряда строки. Элемент 16 НЕ-ИЛИ подключен через транзисторы 17 предварительного разряда столбцов к матрице 18 четьгрехтранзисторных .запоминающих элементов 19, подключенных к выходным вентильным транзисторам 20 столбцов. Элемент 21 ИЛИ соединен с блоком 1 формирования прямого и инверсного кода и дешифратором 5 строк. Разрядные формирователи 22, включающие буферные транзисторы 23 и соединенные с ними вентильные транзисторы 24 подключены к элементу 16 НЕ-ИЛИ и.к дешифратору 6 столбУстройство содержит разр чдные шины 25 матрицы, шину 26 нулевого потенциала, шины 27-30 импульсного питания, входную шину 31 кода адреса. Шину 32 питания,

0 выходную разрядную шину 33 устройства. В матрице 18 четырехразрядных запоминающих элементов 19 адресные входы в строках и разрядные в столбцах соот зетственно объединены, разрядные шины 25 соединены соответственно со стоками выходных вентильных транзисторов 20 столбцов и истоками транзисторов 17 предварительного заряда столбцов, причем стоки последних соединены с шиной 32 питания; истоки выходных вентильных транзисторов 20 столбцов со единены соответственно с разрядными щинами 33 устройства, а затворы - с истоками буферных транзисторов 23 разрядных формирователей 22.

В разрядных формирователях 22 затворы буферных транзисторов 23. соединены

соответственно с истоками входных вентильных транзисторов 24, стоки которых соединены с соответствующими выходами дешифратора 6 строк.

В адресных формирователях 11 стоки

входных вентильных транзисторов 9 и 10 соединены с выходами дешифратора 5 строк, истоки транзисторов 9 и (О соединены соответственно с затворйми буферных транзисторов 12 и 13, стоки которых связаны с шинами 29 и 30 импульсного питания, а истоки соединены со стоками выходных вентильных транзисторов 14, затворы которых . объединены со стоками транзисторов 12 и 13, а истоки соединены со стоками транзисторов 15 предварительного разряда строки. Истоки транзисторов 15 соединены с шиной нулевого потенциала, а.затворы - с затворами транзисторов 17 предварительного за-. ряда столбцов и выходом элемента 16 НЕ-ИЛИ..

J В блоке Г формирования прямого и инверсного кода затвор и исток стробирующего транзистора 4 подключены к затворам соответственно нагрузочного транзистора 2 и вентильного тран.чи.стора 3, Истоки транзисторов 2 и 3 объединены и подключены к выходам прямого и инверсного кода зо Зо ... .. а а, который поступает на дешифратор 6 столбцов. Стоки транзисторов 3 объединены и подключены к выходу элемента 21 ИЛИ. В дешифраторе 5 затвор нагрузочного транзистора 7 подключен к выходу логического элемента 21 ИЛИ, а исток подключен к параллельно включенным транзисторам 8, стоки которых подключены к выходу элемента 21, а истоки - к транзисторам 9 и 10 адресных формирователей Оперативное запоминающее устройство на МДП-транзисторах работает следующим образом. При подаче кода адреса по входным шинам кода адреса устройства 31 на блоке 1 формирования прямого и инверсного кода адреса происходит заряд паразитных емкостей шин прямого хода адреса в тех разрядах, где на входе запоминающего устройства (ЗУ) устанавливаются логическая «1, и разряд в тех, где на входе устанавливается логический «О. Щины инверсного кода адреса заряжаются через нагрузочные транзисторы 2 блока фбрмирования прямого и инверсного кода адреса, если на входе «1 - через вентильные транзисторы 3 блока формирования прямого и инверсного кода адреса. Управление вентильным транзистором 3 осуществляется через стробирующий транзистор 4 блока формирования прямого и инверсного кода адреса, одновременно происходит заряд емкостей узлов дешифратора 5 строк и дешифраторов 6 столбцов через нагрузочный транзистор 7 и вентильный транзистор 8 дешифратора строк . В этот же момент через открытые по фазе I + И (шина импульсного питания-29) входные вентильные транзисторы 9 происходит заряд емкостей буферных транзисторов 12 адресных фо-рмирователей П. По окончании фазы 1 закрываются транзисторы 4 и 2, а транзистор 3 остается открытым, если на данный вход была подана логическая «1. На прямых и инверсных шинах устанавливается потенциал, соответствующий коду адреса, поданному в фазе 1 (шина 27). Тогда по окончании фазы I на всех невыбранных выходах дешифраторов 5 и 6 строк и столб-. цов устанавливается нулевой потенциал и происходит до окончания фазы 1 + И разряд емкостей буферных транзисторов 12 адр есньгх -формирователей 11 всех невыбранных адресов через входные вентильные транзисторы 9 и хотя бы один из транзисторов 8. По окончании фазы + И входные вентильные транзисторы 9 закрываются, обеспечивая сохранение заряда на емкостях буфер- ных транзисторов 12, и открываются все транзисторы 17 предварительного заряда столбцов и транзисторы 15 предварительного разряда строк. Управляющий сигнал для них вырабатывается элементом 16 НЕ-ИЛИ, на входы которого поданы фазы 1 + И и III + + IV (шина 30), а па, выходе вырабатывается мощный импульс в паузах между этими фазами. К моменту начала фазы 1П + IV заканчивается предварительный заряд столбцов и разряд строк и транзисторы 17 и 15 закрываются. ; Е выбранной строке протекает ток заряда шины строки от фазы И + IV через выходной вентильный транзистор 14 адресного формирователя, затвор Kotoporo соединен также с фазой III 4- IV. При этом шины выбранного столбца оказываются подключенными к. общим шинам записи-считывания через пару выходных вентильных TpiaHзисторов 20 столбцов. Одновременно сэтими процессами протекает процесс подготовки следующего адреса строки, ко5Орый noAaetcfl к началу фазы -III (шина 28). В этот момент к затвору стробирующих транзисторов 4 блока формирования прямого и инверсного кода адреса, нагрузочных транзисторов 7 дешифратора строк, нагрузочных транзисторов 2 прикладываются напряжения фазы 1П. Поочередная подача фаз I и И1 на эти затворы осуществляется элементом 21 ИЛИ, ко входам которого присоединены шины фаз I и III. Во время действия фазы 1П во входных цепях и в дешифраторе протекают те же процессы, только происходит заряд емкостей адресных формирователей второй цепи, затворы дополнительных буферных транзисторов 13 адресных формирователей которых соединены с выходами дешифратора через дополнительные входные вентильные транзисторы 10 второй цепи, затворы которых подключены к шине фазы 111 -f IV. Этот процесс не влияет на происходящий в этот момент процесс считывания (записи) по предыдущему адресу, так как выходной вентильнь1Й транзистор 14 этого плеча каждого адресног.о формирователя 11 заперт нулевым потенциалом, присутствующим на шине I 4- 1П, с которой соединены затворы указанных вентильных транзисторов. Таким образом в момент считывания (записи) по предыдущему адресу происходит подготовка .следующего адрес;а (заряд емкостей буферных ячеек соответствующей строки). После окончания фазы III 4- IV происходит, как было показано ранее, предварительный заряд столбцов и разряд строк. В начале фазы 1,1 -f 111 происходит возбуждение строки, адрес которой был подготовлен во время фазы 1П,III + IV, и начинается подготовка следующего адреса, как было писано для начала процесса. Таким образом, предлагаемое запоминаюee устройство обеспечивает возможность бращений к нему дважды за каждый перид Tic различным адресам строк. Если на вход дешифратора 5 строк прдаать поочередно код адреса строки, по которой должно производиться считывание (за пис1)/икод адреса строки, в которой должня пр()изводит(сярегенерация, то в каждом и .риоде обращения к ЗУ, кроме рабочей операции (считывание или запись), производится регенерация информации в одной из строк. Тогда за каждые.32 периода обрятения к ЗУ емкостью 1024 слова выполняется полный цикл регенерации без всяких прерываний доступа к памяти. Кроме того, поскольку полный цйкл регенерации при применении данного устройства умень 11ается до нескольких десятков микросекунд, снижается требование к длительности хран ения информации в запоминающих элементах. Это позволяет исключить запоминаюЪ йе емкости и уменьщить размеры тран-зисторов запоминающих элементов. В этом случае плоп1адь кристалла, затрачиваемаяна размещение устройств коммутации строк, оказывается скомпенсированной уменьшения тлощади, занимаемой матрицей памяти.

Формула изобретения .-Оперативное запоминающее устройство на МДП-транзисторах, сбдбржащее матрицу четырехтранзисторных запоминающих элементов, у которых адресные вхоДывСтроках и разрядные в столбцах соответственно объединены, при этом разрядные входы соеди-нены соответственно со стоками выходных вентильных транзисторов столбцов и истоками транзисторов предварительного заряда столбцов, причем стбки последних соединены с щИной питания, истоки выходных вентильных транзисторов столбцов соединены соответственно с разрядными тинами уст-. ройства, а затворы - соответственно с исТ(жаци буферных транзисторов разрядных формирователей, затворы которых соединены соответственно с истоками входFibix вентильных транзисторов разрядных формирователей, стоки входных вен тпльных транзисторов разрядных .формиро-. вателей соединены с соответствующими выходами децгифратора столбцов, входы которого, соединены с соответствующими выходами блоков формирования прямого и инверсного кода адреса, дешифраторов строк, входы которого соединены с соответствующими выходами блоков формирования прямого и инверсного кода адреса, а выходы - соответственно со стоками входных вентильtfAyj-ft. .г ,

Ч

744726

8

ных транзисторов адресных формирователей, истоки входных вентильных транзисторов адресных формирователей соединены соответственно с затворами буферных транзисторов адресных формирователей, причем входы

всех блоков формирования прямого и инверсного кода адреса соединены с соответствующими входными тинами кода а-дреса устройства, отличающееся , что, с целью повышения быстродействия, оно дополнительно содержит транзисторы предварительй ного разряда строки, истоки которых соединены с ЩИНОЙ нулевого потенциала, затворы-с затворами транзисторов предварительного заряда столбцов и с выходом элемента НЕ-ИЛИ, а стоки - соответственно с истоками двух выходныхвентильных тран, зисторов адресных формирователей в каждом адресном формирователе, .причем сток и. затвор первого выходного вентильного транзистора в каждом адресном формирователе соединен соответственно с истоком и

0 стоком буферного транзистора, а сток и затвор второго выходного вентильного транзистора - с истоком и стоком дополнительного буферного транзистора, затвор которого соединен в каждом адресном формирователе с истоком дополнительного входного

вентильного транзистора, сток дополнительного входного вентильного транзистора в каждом адресном формирователе соединен с соответствующим выходом дешифратора строк, причем первая и вторая щины импульсного питания устройства подключены ко входам элемента ИЛИ, выход которого соеди-, пен со входами импульсного пйта.ния дещифраторов строк и формирователя прямого и инверсного кода адреса, третья щина - к первому входу элемента НЕ-ИЛИ, к затво рам входных вентильных транзисторов адресных и разрядных формирователей и стокам дополнительных буферных транзисторов адресных формирователей, а четвертая щина - ко второму входу элемента НЕ-ИЛЙ, стокам буферных транзисторов адресных и разрядных формирователей и затворам дополнительных входных вентильных транзисто-; ров адресных формирователей.

Источники информации, J принятые во внимание при экспертиз

. Патент № 3685027, кл. 340-173, 1972.

- 2. Валиев К. А. и др. Цифровые интеграль-. ные схемы на МДП-транзистбрах. «Сов. радио, 1971, с. 290.

Авторы

Даты

1980-06-30—Публикация

1974-04-29—Подача