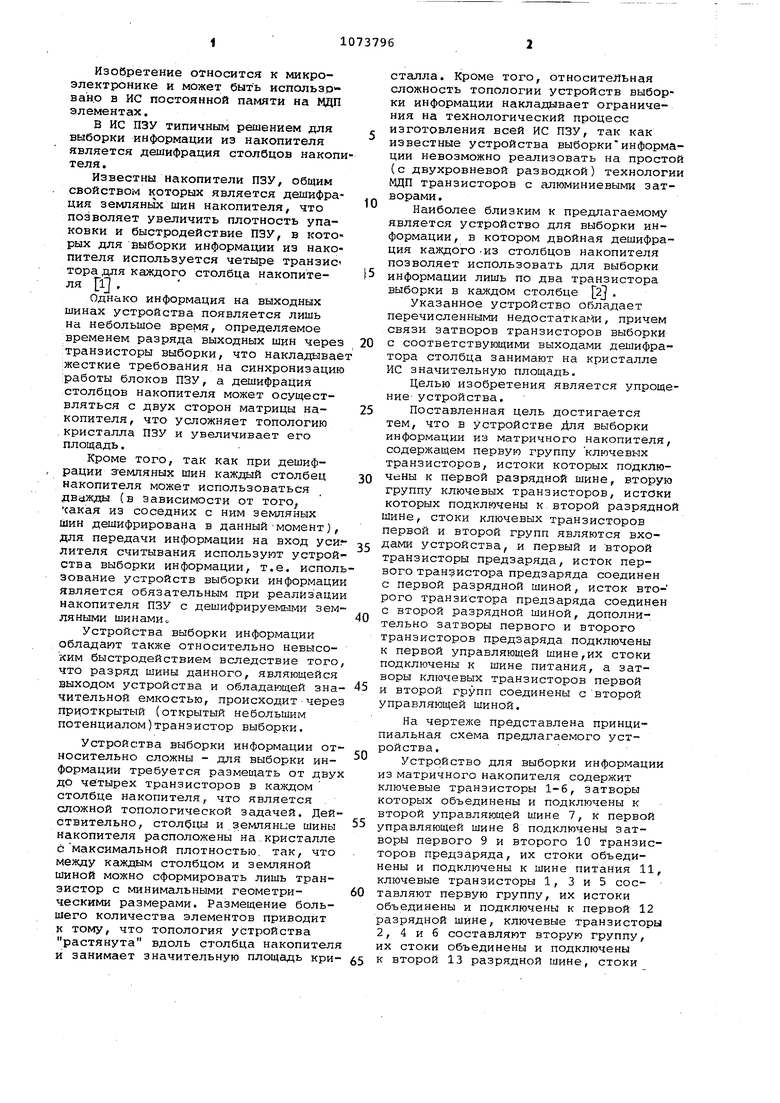

Изобретение относится к микроэлектронике и может быть использрванр в ИС постоянной памяти на МДП элементах. В ИС ПЗУ типичным решением для выборки информации из накопителя является дешифрация столбцов накопи теля. Известны накопители ПЗУ, общим свойством которых является дешифрация земляньЬс шин накопителя, что позволя:ет увеличить плотность упаковки и быстродействие ПЗУ, в которых для выборки информации из накопителя используется четыре транзис1 тора для каждого столбца накопителя 1 . Однако информация на выходных шинах устройства появляется лишь на небольшое время, определяемое временем разряда выходных шин через транзисторы выборки, что наклада1ваё жесткие требования на синхронизацию работы блоков ПЗУ, а дешифрация столбцов накопителя может осуществляться с двух сторон матрицы накопителя, что усложняет топологию кристалла ПЗУ и увеличивает его площадь. Кроме того, так как при дешифрации з-емляных шин каждый столбец накопителя может использоваться дважды (в зависимости от того, сакая из соседних с ним земляных шин дешифрирована в данныймомент), для передачи информации на вход уси лителя считывания используют устрой ства выборки информации, т.е. испол зование устройств выборки информации является обязательным при реализаци накопителя ПЗУ с дешифрируемыми зем ляными шинами Устройства выборки информации обладают также относительно невысоким быстродействием вследствие того что разряд шины данного, являющейся выходом устройства и обладающей зна чительной емкостью, происходит чере приоткрытый (открытый небольшим потенциалом)транзистор выборки. Устройства выборки информации от носительно сложны - для выборки информации требуется размещать от дву до четырех транзисторов в каждом столбце накопителя, что является сложной топологической задачей. Дей ствительно, столбцы и земляние шины накопителя расположены на кристалле 6максимальной плотностью, так, что между каждым столбцом и земляной шиной можно сформировать лишь транзистор с минимальными геометрическими размерами. Размещение большего количества элементов приводит к тому, что топология устройства растянута вдоль столбца накопител и занимает значительную площадь кри сталла. Кроме того, относительная сложность топологии устройств выборки информации накладывает ограничения на технологический процесс изготовления всей ИС ПЗУ, так как известные устройства выборкиинформации невозможно реализовать на простой (с двухровневой разводкой) технологии МДП транзисторов с алюминиевыми затворами. Наиболее близким к предлагаемому является устройство для выборки информации, в котором двойная дешифрация каждого.из столбцов накопителя позволяет использовать для выборки информации лишь по два транзистора выборки в каждом столбце 2 . Указанное устройство обладает перечисленными недостатками, причем связи затворов транзисторов выборки с соответствующими выходами дешифратора столбца занимают на кристалле ИС значительную площадь. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что в Устройстве Для выборки информации из матричного накопителя, содержащем первую группу ключевых транзисторов, истоки которых подключены к первой разрядной шине, вторую группу ключевых транзисторов, истоки которых подключены к второй разрядной шине, стоки ключевых транзисторов первой и второй групп являются входами устройства, и первый и второй транзисторы предзаряда, исток первого транзистора предзаряда соединен с первой разрядной шиной, исток второго транзистора предзаряда соединен с второй разрядной шиной, дополнительно затворы первого и второго транзисторов предзаряда подключены к первой управляющей шине,их стоки подключены к шине питания, а затворы ключевых транзисторов первой и второй групп соединены с второй управляющей шиной. На чертеже представлена принципиальная схема предлагаемого устройства. Устройство для выборки информации из матричного накопителя содержит ключевые транзисторы 1-6, затворы которых объединены и подключены к второй управляющей шине 7, к первой управляющей шине 8 подключены затворы первого 9 и второго 10 транзисторов предзаряда, их стоки объединены и подключены к шине питания 11, ключевые транзисторы 1, 3 и 5 составляют первую группу, их истоки объединены и подключены к первой 12 разрядной шине, ключевые транзисторы 2, 4 и 6 составляют вторую группу, их стоки объединены и подключены к второй 13 разрядной шине, стоки

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Устройство для считывания информации из матричного накопителя | 1978 |

|

SU767834A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

УСТРОЙСТВО ДЛЯ ВЫБОРКИ ИНФОРМАЦИИ ИЗ Г-1АТРИЧНОГО НАКОПИТЕЛЯ, содержащее первую группу ключевых транзисторов, истоки которых подключены к первой разрядной шине, вторую группу ключевых транзисторов, истоки которых подключены к второй разрядной шине, стоки ключевых транзисторов первой и второй групп являются входами устройства, и первый и второй транзисторы предзаряда, исток первого транзистора предзаряда соединен с первой разрядной шиной, исток второго транзистора предзаряда соединен с второй разрядной шиной, отличающееся тем, что, с целью упрощения устройства, затворы первого и второго транзисторов предзаряда подключены к первой управляющей шине, их стоки подключены к шине питания, а затворы ключевых транзисторов первой и второй групп соединены с второй управляющей шиной.«g ±1 (Л со а

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент CtlA № 4193125, кл | |||

| Приспособление для разгонки рельсов ударами | 1923 |

|

SU665A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| : | |||

Авторы

Даты

1984-02-15—Публикация

1982-11-04—Подача