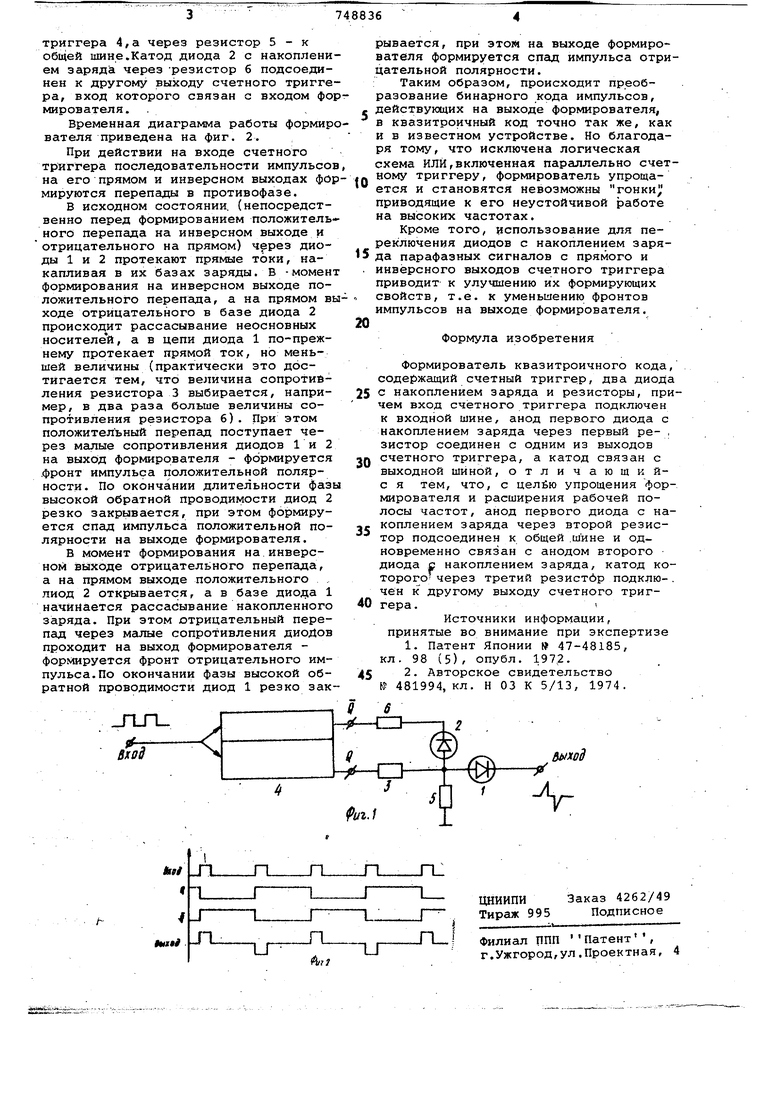

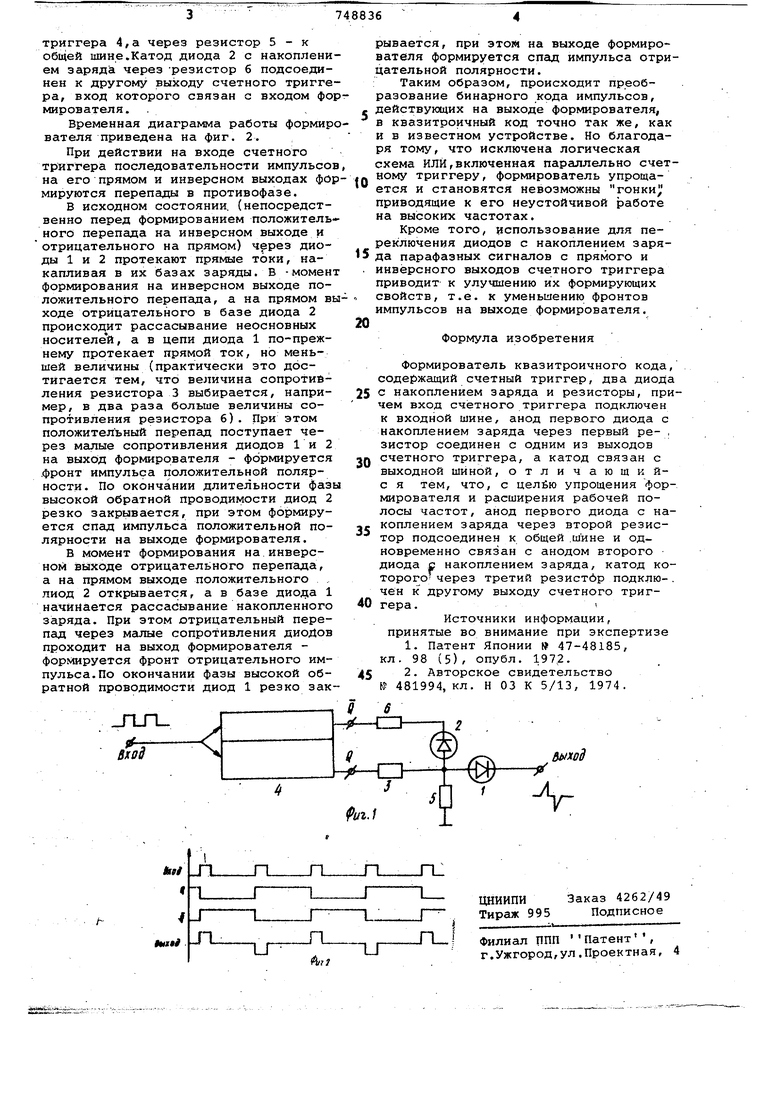

Изобретение относится к импульсно технике и может найти применение в л нейных трактах высокоскоростных систем связи с ИКМ, в устройствах автоматики и вычислительной техники. Известны устройства подобного тип содержащие триггеры и диоды с накоплением заряда ClJ. Недостаток этих устройств состоит в их сложности. Наиболее близким техническим решением к изобретению является формирователь квазитроичного кода, выполненный на счетном триггере и диодах с накоплением зарядаГ23. Наряду с многими положительными .достоинствами (возможность формирования квазитроичного кода, простота широкополосность и т.д.) известный формирователь имеет ограниченный диа пазон частот устойчивой работы, связанный с тем, что между входом и выходом счетного триггера включено дополнительное логическое устройство. Наличие задержек в параллельно включенных логических cxeMaix (счетного триггера и схемы ИЛИ) между входом и выходом формирователя обуславливает возникновение гонок, что приводит к его неустойчивой работе на высоких частотах. Целью изобретения является упрощение формирователя и расширение рабочей полосы частот. Цель достигается тем, что в формирователе квазитроичного кода, содер-жащем счетный триггер, два диода с накоплением заряда и резисторы, причем вход счетного триггера подключен к. входной шине, анод первого диода с накоплением заряда через первый резистор соединен с одним из выходов счетного триггера, а катод связан с выходной шиной, анод, первого диода с накоплением заряда через второй резистор подсЪедине н к общей шине и одновременно связан с анодом второго диода с накоплением заряда, катод которого подключен через третий резне- тор к другому выходу счетного триггера . .«. Принципиальная схема предлагаемого формирователя приведена на фиг.1. Катод диода 1 с накоплением заряда подключен к выходу формирователя, а анод связан с анодом диода 2 с накоплением заряда, через резистор 3 подключен к одному из выходов счетного

триггера 4,а через резистор 5 - к общей шине.Катод диода 2 с накоплением заряда через -резистор б подсоединен к другому выходу счетного триггера, вход которого связан с входом формирователя. .

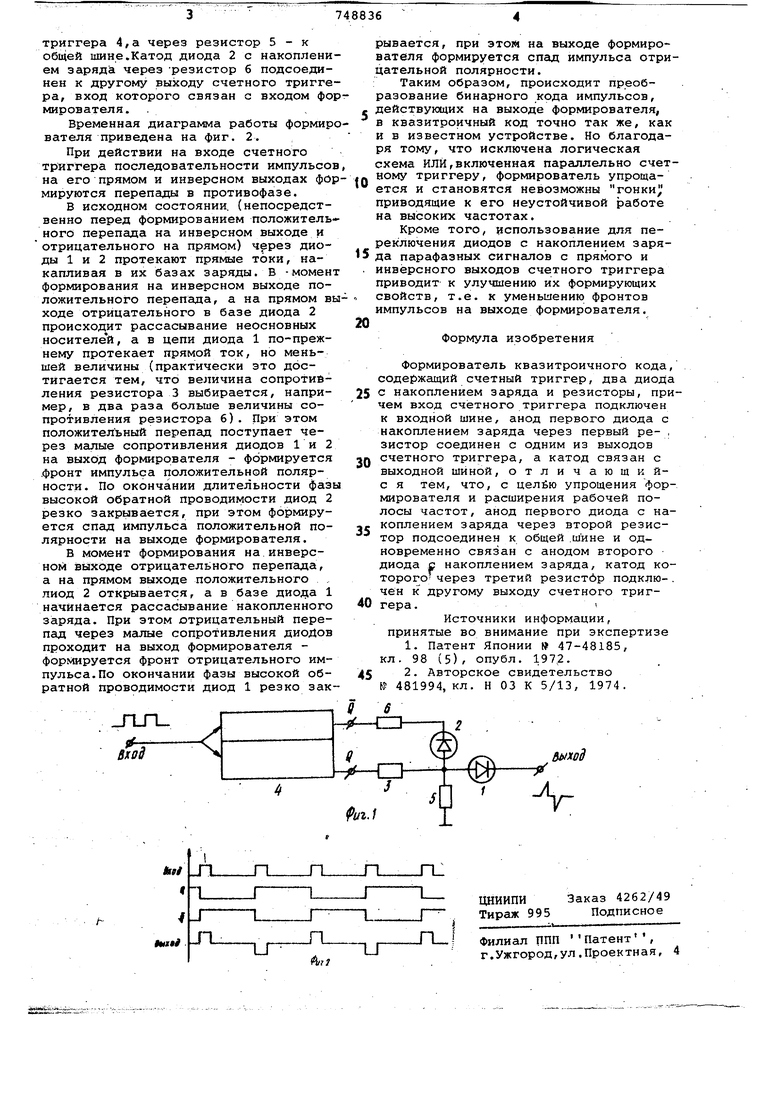

Временная диаграмма работы формирователя приведена на фиг. 2.

При действии на входе счетного триггера последовательности импульсов на его прямом и инверсном выходах формируются перепады в противофазе.

В исходном состоянии, (непосредственно перед формированием положительного перепада на инверсном выходе и отрицательного на прямом) диоды 1 и 2 протекают прямые токи, накапливая в их базах заряды. В -момент формирования на инверсном выходе положительного перепада, а на прямом выходе отрицательного в базе диода 2 происходит рассасывание неосновных носителей, а в цепи диода 1 по-прежнему протекает прямой ток, но меньшей величины (практически это достигается тем, что величина сопротийления резистора 3 выбирается, например, в два раза больше величины сопротивления резистора 6). При этом положительный перепад поступает через малые сопротивления диодов 1 и 2 на выход формирователя - формируется .фронт импульса положительной полярности. По окончании длительности фазы высокой обратной проводимости диод 2 резко закрывается, при этом формируется спад импульса положительной полярности на выходе формирователя.

В момент формирования на инверсном выходе отрицательного перепада, а на прямом выходе положительного лиод 2 открывается, а в базе диода 1 начинается рассасывание накопленного заряда. При этом отрицательный перепад через малые сопротивления диодов проходит на выход формирователя формируется фронт отрицательного импульса. По окончании фазы высокой обратной проводимости диод 1 резко закрывается, при этол на выходе формирователя формируется спад импульса отрицательной полярности. : Таким образом, происходит преобразование бинарного кода импульсов, , действующих на выходе формирователя, в квазитроичный код точно так же, как и в известном устройстве. Но благодаря тому, что исключена логическая схема ИЛИ,включенная параллельно счетному триггеру, формирователь упрощается и становятся невозможны гонки), приводящие к его неустойчивой работе на высоких частотах.

Кроме того, использование для переключения диодов с накоплением заряда парафазных сигналов с прямого и . инверсного выходов счетного триггера приводит к улучшению их формирующих свойств, т.е. к уменьшению фронтов импульсов на выходе формирователя.

Формула изобретения

Формирователь квазитроичного кода, содержащий счетный триггер, два диода 5 с накоплением заряда и резисторы, причем вход счётного триггера подключен к входной шине, анод первого диода с накоплением заряда через первый ре- , зистор соединен с одним из выходов счетного триггера, а катод связан с выходной шиной, отличающкйс я тем, что, с целбю упрощения формирователя и расширения рабочей полосы частот, анод первого диода с накоплением заряда через второй резистор подсоединен к общей .шине и одновременно связан с анодом второго диода с накоплением заряда, катод которого через третий резистбр подклю-. чен к другому выходу счетного триггера.

Источники информации, принятые во внимание при экспертизе

1.Патент Японии № 47-48185, кл. 98 (5), опубл. 197,2.

2.Авторское свидетельство

481994, кл. Н 03 К 5/13, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1973 |

|

SU493922A1 |

| Формирователь парных импульсов | 1973 |

|

SU450334A1 |

| Формирователь одиночных импульсов | 1983 |

|

SU1160548A1 |

| Формирователь импульсов | 1980 |

|

SU921065A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВВ ПТ Бi1П п!?рr-^rfi'"''- ' >& | 1971 |

|

SU422094A1 |

| Формирователь биполярных сигналов | 1990 |

|

SU1780156A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 1972 |

|

SU432678A1 |

| Формирователь сигналов | 1986 |

|

SU1368970A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1210215A1 |

| Формирователь ступенчатого напряжения | 1975 |

|

SU566325A1 |

Авторы

Даты

1980-07-15—Публикация

1978-01-05—Подача