(54) ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовращатель | 1983 |

|

SU1102026A2 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

| Цифровой фазовращатель | 1986 |

|

SU1394410A1 |

| Цифровой фазовращатель | 1984 |

|

SU1239630A1 |

| Фазосдвигающее устройство | 1984 |

|

SU1226340A1 |

| Ультразвуковое сканирующее и фокусирующее устройство | 1984 |

|

SU1250932A1 |

| Устройство обработки данных спектрометрического гамма-каротажа | 1985 |

|

SU1285422A1 |

| Устройство регулируемой задержки | 1984 |

|

SU1175020A1 |

| РАДИОЛОКАЦИОННОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАЛЬНОСТИ (ВАРИАНТЫ) | 1999 |

|

RU2154285C1 |

| Ультразвуковое сканирующее и фокусирующее устройство | 1987 |

|

SU1539647A1 |

1

изобретение относится к радиотех- нике, в частности используется в качестве исполнительного элемента систём автоматического сопровождения j сигнала по фазе, частоте или временной задержке.

Известен цифровой фазовращатель, содержащий счетчик, выходы которого соединены с первыми входами блока ю сравнения, вторые входы которого подключены к выходам фазозадающего блока, и т Зиггер, сигнал на выходе которого является выходным сигналом фазовращателя 1,«с

Недостаток известного устройства низкая точность установки фазы выходного сигнала из-за разброса и нестабильности сигнала в триггерах ; счетчика и логических схемах-блока jo : сравнения. Кроме того, влияние упомянутых факторов, а также конечного времени срабатывания элементов устройства приводит к возникновению ложных срабатываний выходного триггера. 25 К недостаткам данного устройства следует отнести снижение выходной частоты вдвое.по сравнению с частотой совпадения кодов на выходах счетчика и фэзрзадающегО1 блока. Из-за этого для Q

обеспечения заданной частоты на выходе фазовращателя частоту входного сигнсша приходится повышать в два раза, что приводит к необходимости использования в устройстве более высокочастотной элементной базы.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее счетчик, подключенный к выходу задающего генератора, блок сравнения, соединенный с выходами счетчика и фазозадающего блока, счетный триггер, подключенный к выходу последнего разряда счетчика, элементы однозначности и элементы неоднозначности, одни входы которых соединены с выходами счетного триггера и входом фильтра, а другие - с выходом фазозадающего блока, элементы совпадения, первые входы которых подключены к выходу блока сравнения, а вторые входы - к выходам, соответственно, элемент одйозначности и элемент неоднозначности, триггер с раздельным управлением, входы которого соединены с выходами элементов совпадения, а выход - с входом фильтра 2J .

Йедостаток этого устройства низкая точность установки фйзы и наличие ложных срабатываний.

Цель изобретения - повышение точности установки фазы и исключение ложных срабатываний.

Цель достигается тем, 4to в цифровой фазовращатель, содержащий счетчик выходы которого подключены к первым входам блока сравнения, вторые входы jKOTOporo соединены с выходами фазозадающего блока, триггер с раздельным управлением, введены два тактируемых фильтра с памятью, сигнальный вход каждого из которых «соединен с соответствующим выходом блока сравнения, а выходы каждого тактируемого фильтра с памятью подключены к соответствующи входам триггера с раздельным управлением, причем тактовые входы упомянуты фильтров соединены со счетным входом счётчика.

В указанном устройстве тактируемые фильтры с па1мятью могут быть выполнен в виде синхронных D-триггеров с двойной памятью.

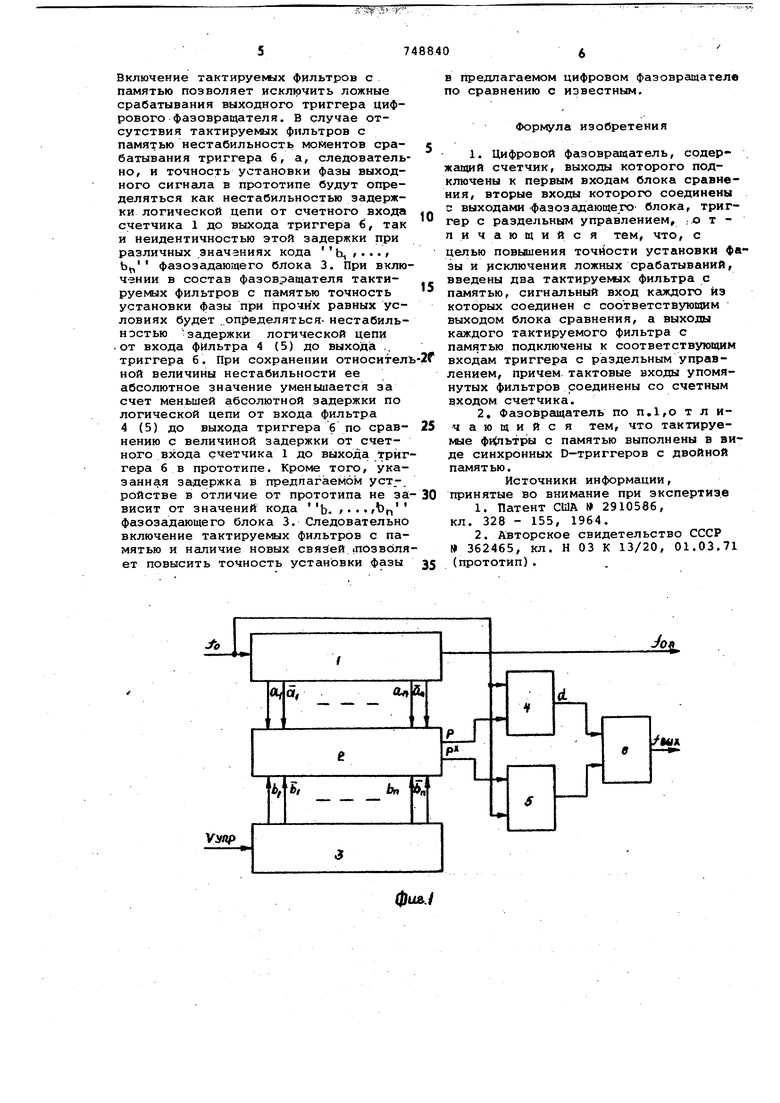

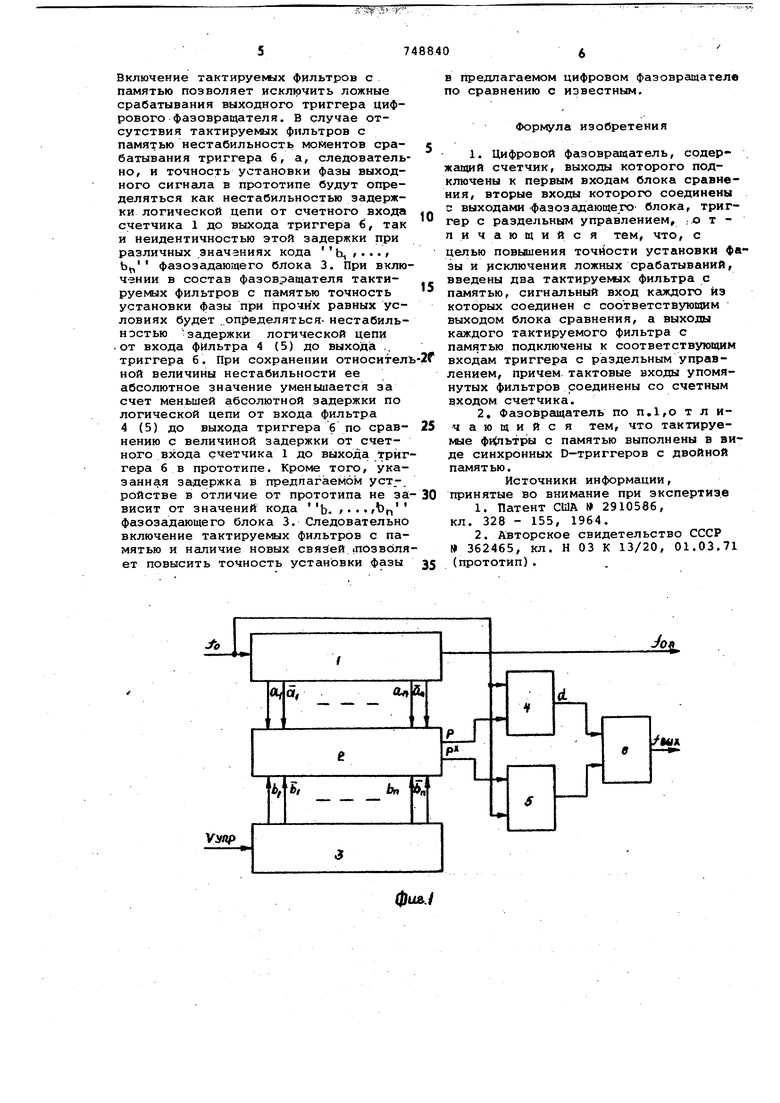

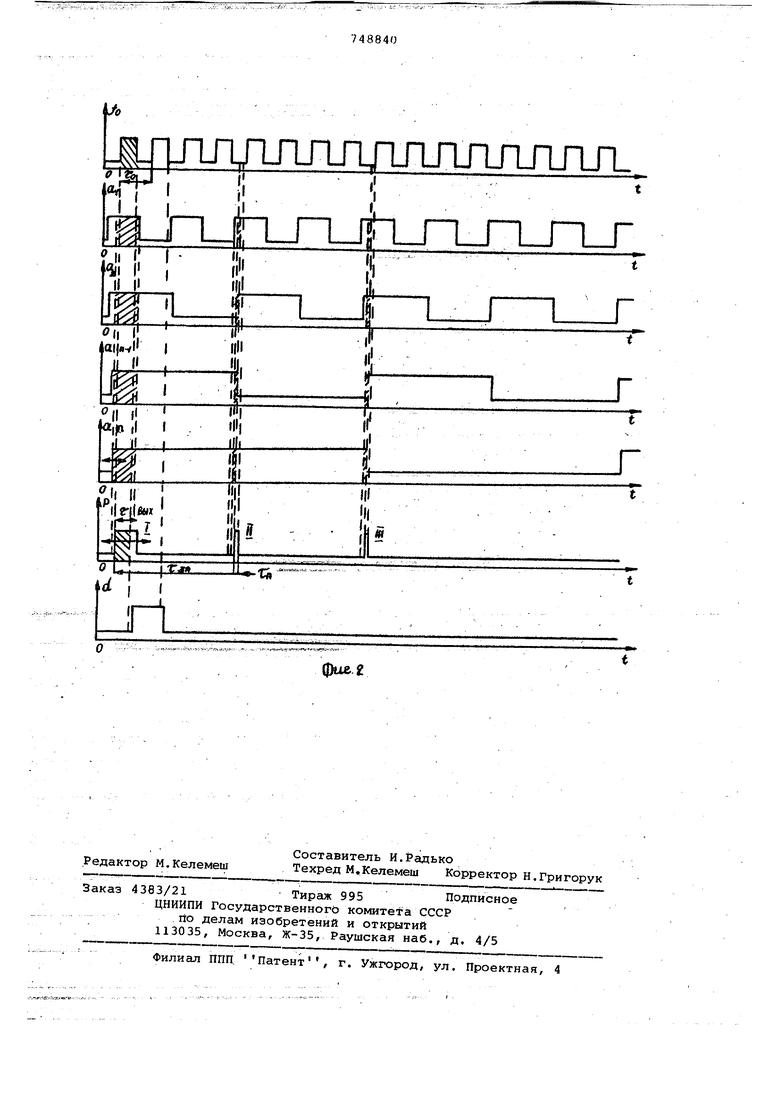

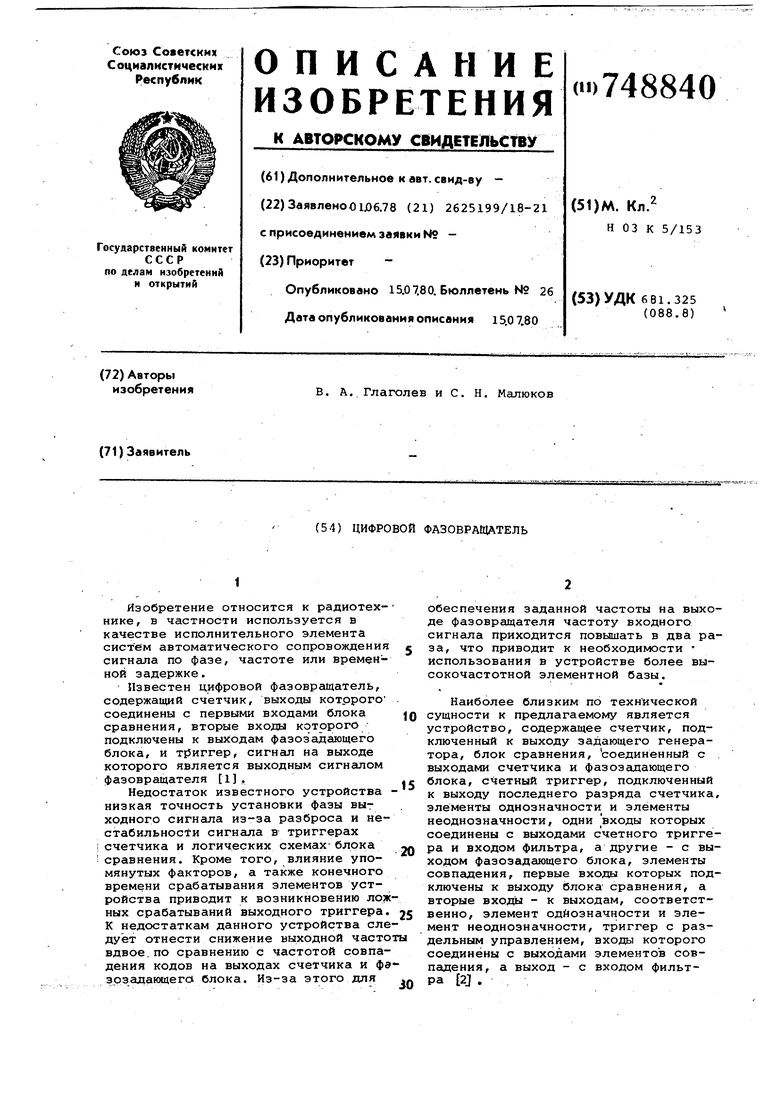

На фиг. 1 представлена функциональ ная схема устройства; на фиг. 2 эпюры импульсов.

Цифровой фазовращатель содержит счетчик 1, выходы которого подключены к первым входам блока 2 сравнения, вторые входы Которого соединены с выходами фазозадающего блока 3, а выходы блока 2 сравнения подключены к информационным входам тактируемых фильтров 4 и 5 с памятью, например, выполненных в виде синхронных D-триггеров с двойной памятью, причем тактовые входь фильтров 4 и 5 соединены со счетным-входом счетчика 1, а выходы упомянутых фильтров 4 и 5 пбдключены к выходам триггера с раздельным уп равлением 6.

Устройство работает следующим образом.

На счетный вход счетчика 1 постуfj T входные импульсы с частотой f и периодом (эпюра 1 на фиг. 2). При этом происходит периодическое изменение кода, записанного в счетчике i с периодом Трп где п - число разрядов счетчика 1. Изменяющийся код О, ...,Оп ходов разрядовсчетчика 1 поступает на первые входы блока 2 сравнения,на вторые входы которого поступает код ,..., Ь„ с выходов фазозадающего блока 3. На выходах Р т блока 2 сравнения синхронно с моментами совпадения кодов .формируются импульсы с частотой повторения (,ях о1 длительностью 7/to/2 , сдвинутые друг относительно друга на половину периода частоты fj,,, . Однако, кроме этих, импульсоа на выходах Р и Р будут присутствовать импульсы, наличие которых обусловлено влиянием конечных задержек и времени срабатывания реальных элементов цифрового фазовращателя (эпюра P-II,III фиг. 2) Паразитные импульсы на выходах блока 2 сравнения могут быть представлены в виде суммы последовательностей импульсов, имеющих ту же частоту повторения, что и полезные (эпюра P-I фиг. 2) но имеющих случайную длительность TO и случайную задержку tjr относительно полезных. В диапазоне рабочих частот цифрового фазовращателя су1.1марная максимальная задержка по самой длинной логической цепи фазовращателя с учетом максимального времени срабатывания элементов остается меньшей половины периода TO входных импульсов на величину, обеспечиваемую устойчивое срабатывание элементов фазовращателя: . В то же время длительность полезных импульсов остается большей длительности половины периода входных: tj, . В этом рлучае длительность паразитных импульсов существенно меньше длительности полезных. Смесь полезных и паразитных импульсов с выходов Р и Р блока

2сравнения поступает на сигнальные входы тактируемых фильтров 4 и 5 с памятью, на тактовые входы которых подаются входные импульсы частоты PQ. Изменение информации на выходах фильтров 4 и 5 будет происходить только в том случае, если импульс на сигнальном входе фильтра не только совпадает с тактовым, но и целиком перекрывает его,

С учетом различий в длительности плезных и паразитных импульсов становится очевидным, что информация на выходах тактируенмх фильтров 4 и 5 с памятью будет изменяться только при поступлении на их сигнальные входы полезных импульсов, что наглядно иллюстрируется эпюрами f, Р и d на фиг. 2. В качестве тактируемого фильтра с памятью может быть использован синхронный D-триггер с двойной памятью, серийно выпускаел«й промышленностью. При этом наличие в D-триггере двойной памяти будет обеспечивать неизменность его выходного состояния при попадении на его информационный D вход паразитного импульса и одновременном поступлении на его тактовый С вход входных импульсов.

Таким образом, на входы триггера с раздельным управлением 6 будут поступать последовательности только полезных импульсов, сдвинутые друг относительно друга на половину периода частоты fgibtx и Начальной фазой, определяемой моментом совпадения кодов на выходах счетчика 1 и фазозадающего блока.3. Изменение кода Ъ,,..., Ьп на выходе фазозадающего блока

3Судет вызывать изменение начальной фазы меандра на выходе триггера 6 с минимальным дискретом 360/2 Включение тактируемых фильтров с памятью позволяет исключить ложные срабатывания выходного триггера цифрового фазовращателя. В случае отсутствия тактируемых фильтров с памятью нестабильность моментов срабатывания триггера 6, а, следователь но, и точность установки фазы выходного сигнала в прототипе будут определяться как нестабильностью задержки логической цепи от счетного входа счетчика 1 до выхода триггера б, так и неидентичностью этой задержки при различных значениях кода h, . .. b, фазозадаюэдего блока 3. При вклю чении в состав фазовращателя тактируемых фильтров с памятью точность установки фазы при прочих равных условиях будет „определяться- нестабильностью задержки логической цепи от входа фильтра 4 (5) до выхода ,, триггера б. При сохранении относител ной величины нестабильности ее абсолютное значение уменьшается за счет меньшей абсолютной задержки по логической цепи от входа фильтра 4 (5) до выхода триггера б по сравнению с величиной задержки от счетного входа счетчика 1 до выхода триг гера б в прототипе. Кроме того, указан на,я задержка в предлагаемом уст-, ройстве в отличие от прототипа не за висит от значений кода Ь. ,...,Ъп фазозадающего блока 3. Следовательно включение тактируемых фильтров с памятью и наличие новых связей (позволя ет повысить точность установки фазы в предлагаемом цифровом Фазовращателе по сравнению с известным. Формула изобретения 1. Цифровой фазовращатель, содержащий счетчик, выходы которого подключены к первым входам блока сравнения, вторые входы которого соединены с выходами фазозадающего блока, триггер с раздельным управлением, .-.о т л и чающий с я тем, что, с целью повышения точйости установки фа зы и исключения ложных срабатываний, введены два тактируемых фильтра с памятью, сигнальный вход каждого из которых соединен с соответствующим выходом блока сравнения, а выходы каждого тактируемого фильтра с памятью подключены к соответствующим входам триггера с раздельным управлением, причем тактовые входы упомянутых фильтров соединены со счетным входом счетчика. 2, Фазойращатель по п.1,о т л ичающийся тем, что тактируемые фи1льтры с памятью выполнены в виде синхронных D-триггеров с двойной памятью. Источники информации, принятые во внимание при зкспертиз.е 1.Патент США 2910586, кл. 328 - 155, 1964. 2.Авторское свидетельство СССР 362465, кл. Н 03 К 13/20, 01.03.71 (прототип).

Л

Of

S/

УУпр

On

bn бп

П-П-Ги

е

|.Тлп..

фиг. 2

Авторы

Даты

1980-07-15—Публикация

1978-06-01—Подача