i ,

Изобретение относится к радиотехнике и может быть использовано в качестве исполнительного элемента систем ав томатического регулирования по фазе, частоте или временной задержке.

Цель изобретения - повышение надежности работы устройства достигается введением блоков, контролирующих возникновение ложной информации в элементах управления и исключ ающих прохождение сбоев в фа- зозадающий блок..

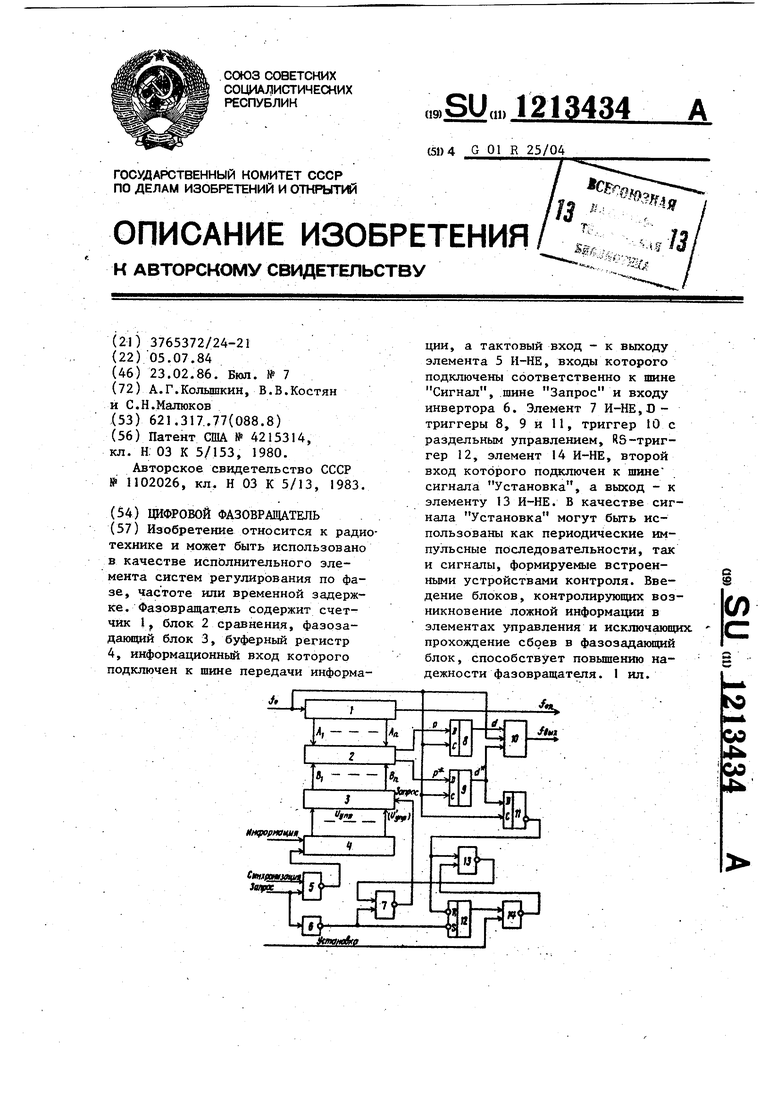

На чертеже приведена функциональная схема цифрового фазовращателя.

Устройство содержит счетчик 1, счетный вход которого подключен к шине входного опорного сигнала, а выходы - к первым входам блока 2 сравнения, вторые входы которого соединены с выходами фазозадающего блока 3, входы которого соединены с вьпсодами буферного регистра 4, информационный вход которого подключен к шине передачи информации, а тактовый вход соединен с выходом элемента И-НЕ 5, первый вход которого подключен к шине Синхросигнал , а второй его вход - к шине сигнала .Запрос и к входу инвертора 6, выход которого соединен с первым входом элемента И-НЕ 7, выход которого соединен с входом записи фазозадающего . блока 3, основной и сопряженный выходы блока 2 сравнения соединены с информационными входами первого и второго D-триггеров 8 и 9 соответственно, выходы которых подключены к входам триггера 10 с раздельным управлением, выход которого подключен к выходной шине, выход второго D-триг гера 9 соединен с входом третьего D-триггера 11, тактовый вход которого соединён с тактовьми входами первого и второго D-триггеров 8 и 9 с тактовьм входом триггера 10 с раздельным управлением и со счетным входом счетчика 1 ; инверсный вьпсод третьего D-триггера 11 соединен с R-входом RS-триггера 12 и первым входом элемента И-НЕ 13, а выход RS-триггера 12 соединен с вторым входом элемента И-НЕ 1А, второй вхо которого подключен .к шине сигнала Установка, выход элемента И-НЕ 14 соединен с вторым входом элемента

13434 ,2

И-НЕ 13, выход которого-соединен с вторым входом второго элемента И-НЕ 7, а выход инвертора 6 кроме того, соединен с входом S-тригге- 5 ра 12.

Предлагаемое устройство работает следующим образом.

На счетный вход счетчика 1 по- JO ступают входные импульсы с частотой повторения f. При этом происходит периодическое изменение кода, записанного в счетчике 1 с периодом K/fд, где К - коэффициент пересче- )5 та. счетчика 1 . Изменяющийся код А; с выходов разрядов счетчика 1 поступает на первые входы блока 2 сравнения, на вторые входы которого поступает код Bj с выходов фазозада- 2Q ющего блока 3.На выходах Р и Р блока 2 сравнения синхронно с моментами совпадения входных кодов формируются импульсы с частотой повторения f.., fn/K, сдвинутые один

вы л U

25 относительно другого на половину периода частоты fftbi .. Однако, кроме .полезных импульсов, на выходах Р и Р блока сравнения могут присутствовать паразитные импульсы, наэд личие которых обусловлено влиянием конечных задержек и времени срабатывания реальных элементов устройства. Дпя фильтрации паразитных импульсов сигналы с выходов блока 2 сравнения подаются на информационные входы двух тактируемых фильтров с памятью, на тактовые входы которых поступает сигнал опорной частоты f. В качестве тактируемых фильтров с памятью могут быть использованы синхронные D-триггеры с дяойной памятью. Вследствие того, что длительность паразитных импульсов существенно меньше длительности полезных, на выхо дах d и d D-триггеров 8 и 9 формируются импульсы, соответствующие только полезным составляющим сигналов совпадения Р и Р . Таким образом, на входы триггера 10 с раз-

5 дельным управлением поступают последовательности только полезных импульсов, сдвинутые один относительно другого на половину периода частоты с начальной фазой, оп55 ределяемой моментом совпадения

кодов на выходах счетчика 1 и фазозадающего блока 3 в соответствии с поступающими на его вход сигна35

40

лами управления U , и сигнал с выходов буферного регистра 4 вызывает изменение фазы.меандра, следующего с частотой , , на выходе .триггера 10 с раздельньм управле- нием с минимальным дискретом

utf л«ии 360 /К

(1)

При поступлении сигнала Запрос на вход элемента И-НЕ 5 разрешает- ся прохождение сигнала Синхронизация через этот элемент на тактовый вход буферного регистра 4, что обеспечивает запись информации поступающей по шине Информация, последовательно во времени в буферный регистр 4. К моменту окончания сигнала Запрос в буферном регистре 4 записывается код управления фазой Uynp. По окончании сигнала Запрос на первый вход элемента И-НЕ 7 поступает разрешающий потенциал с выхода инвертора 6.

Кроме того, сигнал Запрос, поступает на S-вход R-S-триггера 12 и устанавливает его выход в состояние логической единицы, которая поступает на первый вход элемента И-НЕ 14, на второй вход ко- торог о поступает сигнал логического нуля с шины Установка. При эт на выходе элемента И-НЕ 14 действует уровень логической единицы, поступающий на второй вход элемента И-НЕ 13.

Сигнал совпадения d с выхода D-триггера 9 поступает на информа- ционный вход D-триггера 11, в результате чего на выходе последнего формируется импульс, сдвинутый относительно основного импульса совпадения d на величину (2н-1 )fp и синхронизированный с импульсами опорной частоты f . Сигнал с инверного выхода D-триггера 11 чере элементы И-НЕ 13 и 7 поступают на вход Запись фазозадающего блока 3 и обеспечивает изменение управляющего кода В: на его выходе в соответствии с вновь записанньм в буферном регистре 4 кодом управления фазой Uunp . Кроме того, сигнал с инверсного выхода D-триггера 1 1 поступает на R-вход R-S.-триггера 12 и устанавливает его выход в состояние Логический нуль. При этом изменение кода Bj на выходе фазозадающего блока 3 происходит с за13434 ..

держкой V относительно импульсов опорной частоты f, действующих на тактовом входе D-триггера 11. С точностью до величины высшего по- 5 рядка малости у равно у .

Таким образом, изменение кода В происходит синхронно с импульсами, сдвинутыми относительно основного импульса совпадения d на вели- 10 чину

йТ, T(2+l)f +у . (2)

Из сравнения выражений (l) и (2) видно, что они равны. Следовательно,

введение в цепь формирования сигнала Запись в предлагаемом устройстве по сравнению с известным дополнительного элемента И-НЕ 13 не приводит к ухудшению динамических .

свойств фазовращателя и снижению надежности его работы при значениях изменения фазы выходного сигнала, близких к ir . Это достигается за счет подачи сигнала Запись непосредственно на вход записи фазоза--- дающего блока 3 при одновременном исключении из состава предпагаемо- го устройства и схем совпадения, входящих в буферный блок известног

го. При этом в фазозадающий блок

3конструктивных изменений не вносится.

В том случае, если по очередному сигналу Запрос в буферный реглстр

4был записан запрещенный код управления фазой UN , то по сигналу совпадения d с задержкой на один период частоты следования f, этот код переписывается в фазозадающий блок 3. Значение этого кода В| находится в интервале запрещенных кодов Ag...A, при этом совпадения кодов в блоке 2 сравнения не происходит, и, следовательно, не формируются импульсы совпадения d

и d, что приводит к блокировке выхода устройства.

При следующем обращении к устройству по сигналу Запрос в буферный регистр 4 записывается

разрешенный код, но переписи его в фазозадающий блок не происходит, поскольку отсутствуют импульсы d . Одновременно сигнал Запрос, проходя через инвертор 6 поступает на S-Bxofl R-S-триггера и устанавливает его выход в состояние логической единицы, которая поступает

наПТервый вход элемента И-НЕ 14, разрешая прохождение сигнала Установка с второго входа элемента И-НЕ 14 на его выход. Через элементы И-НЕ 13 и 7 он поступает на вход Запись фазозадающего блока и обеспечивает перепись разрешенного кода управления фазой U

З

фазозадающий блок 3. При этом на выходе блока 2 сравнения появляются импульсы совпадения Р и Р, которые, проходя D-триггеры 8 и 9, поступают на триггер 10 с раздельным управлением, на выходе которого появляется меандр с частотой следования f ц, , и предлагаемое устройство разблокируется. Кроме того, сигнал с инверсного выхода D-триггера 11 поступает на R-вход R-S-триггера 12 и возвращает его выход в исходное состояние логического нуля.

В качестве сигнала Установка могут быть использованы как периодические импульсные последовательности, так и сигналы, формируемые встроенными устройствами контроля.

Формула изобретени

Цифровой фазовращатель, содержащий счетчик, элемент совпадения, фазозадающий блок, буферный регистр, три D-триггера, триггер с раздельным управлением, два элемента И-НЕ и инвертор, вход которого соединен с шиной Запрос и первым входом первого элемента И- НЕ, второй вход которого подключен к шине Синхросигнап, а выход перСоставитель В.Шубин Редактор Т.Кугрьш1ева Техред м.Пароцай, Корректор-С.Шек мар

779/56

Тираж 730Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

вого элемента И-НЕ соединен с тактовым входом буферного регистра, информационный вход которого сое- динен с шиной Информация, причем счетный вход счетчика подключён к шине опорного сигнала, к счетным входам трех D-триггеров и к счетному входу триггера с раздельным уп- равлением, выход которого подключен к шине выходного сигнала, а его входы соединены с выходами первого и второго Л-триггеров, информационные входы которых подключены к ос- новному и сопряженному выходам элемента совпадения, первые и вторые входы которого соединены соответственно с выходами счетчика и с выходами фазозадающего блока, а выход

второго D-триггера соединен с информационным входом третьего D-триггера, отличающийся тем, что, с целью повьшения надежности, в него дополнительно введены третий и четвертый элементы И НЕ и RS-триггер, S-вход которого подключен к выходу инвертора, а Н-вход соединен с инверсным выходом третьего D-триггера и с первым входом третьего элемента И-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого подключен к входу Запись фазозадающего блока, входы которого

подключень к выходам буферного регистра, причем второй вход третьего элемента И-НЕ соединен с выходом четвертого элемента И-НЕ, первый вход которого соединен с выходом

RS-триггера, а второй его вход соединен с шиной сигнала Установка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовращатель | 1986 |

|

SU1394410A1 |

| Цифровой фазовращатель | 1983 |

|

SU1102026A2 |

| Устройство регулируемой задержки | 1984 |

|

SU1175020A1 |

| Цифровой фазовращатель | 1984 |

|

SU1239630A1 |

| Цифровой фазовращатель | 1978 |

|

SU748840A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Измеритель временных интервалов | 1988 |

|

SU1672411A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ГРУППОВЫХ КОДОВ | 1990 |

|

RU2025049C1 |

| Управляемый делитель частотыСлЕдОВАНия иМпульСОВ | 1979 |

|

SU815922A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

Изобретение относится к радиотехнике и может быть использовано в качестве исполнительного элемента систем регулирования по фазе, частоте или временной задержке. Фазовращатель содержит счетчик 1, блок 2 сравнения, фазоза- дающий блок 3, буферный регистр 4, информационный вход которого подключен к шине передачи информации, а тактовый вход - к выходу элемента 5 И-НЕ, входы которого подключены соответственно к шине Сигнал, шине Запрос и входу инвертора 6. Элемент 7 И-НЕ,О - триггеры 8, 9 и 11, триггер 10 с раздельным управлением, RS-триггер 12, элемент 14 И-НЕ, второй вход которого подключен к шине сигнала Установка, а выход - к элементу 13 И-НЕ. В качестве сигнала Установка могут быть использованы как периодические импульсные последовательности, так и сигналы, формируемые встроенными устройствами контроля. Введение блоков, контролирующих возникновение ложной информации в элементах управления и исключающих, прохождение сбоев в фазозадающий блок, способствует повышению надежности фазовращателя. I ил. § (Л ИтвнаЛю

| Патент США № 4215314, кл | |||

| Н | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фазовращатель | 1983 |

|

SU1102026A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-23—Публикация

1984-07-05—Подача