1

Изобретение относится к радиотехнике и может быть использовано в качестве исполнительного элемента систем автоматического регулирования по частоте, фазе, или временной задержке.

Цель изобретения - увеличение допустимой скорости изменения задержки выходного сигнала при одновременном уменьшении аппаратурного объема.

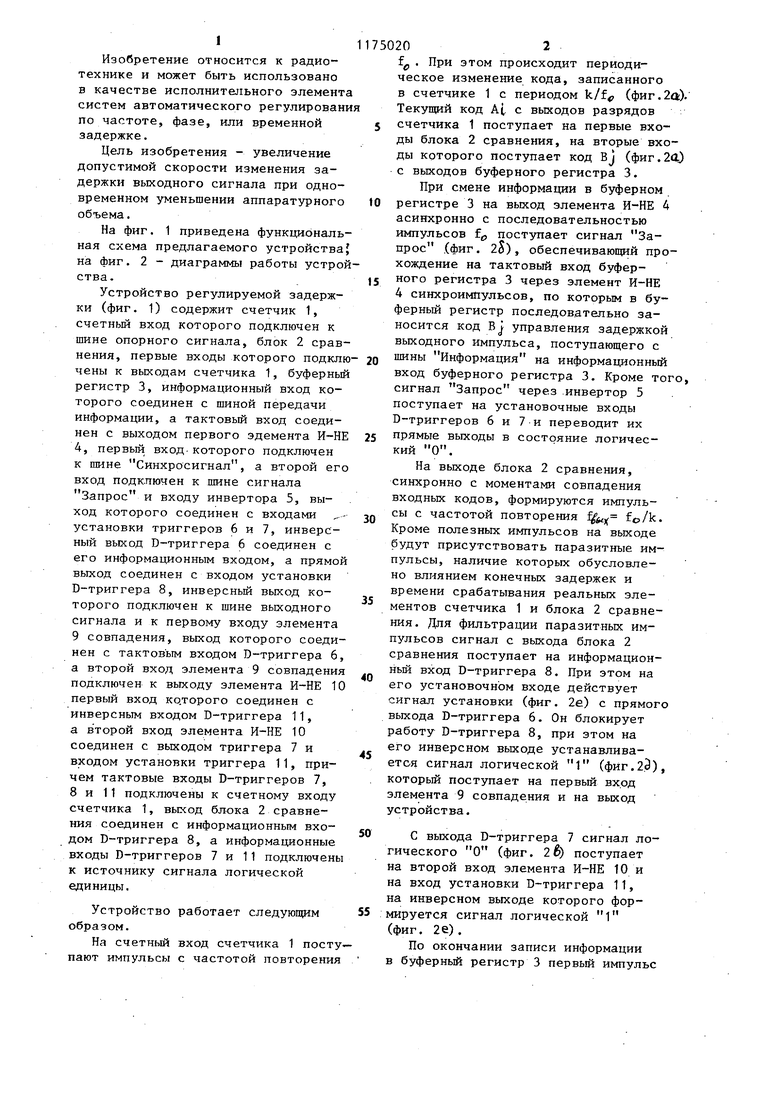

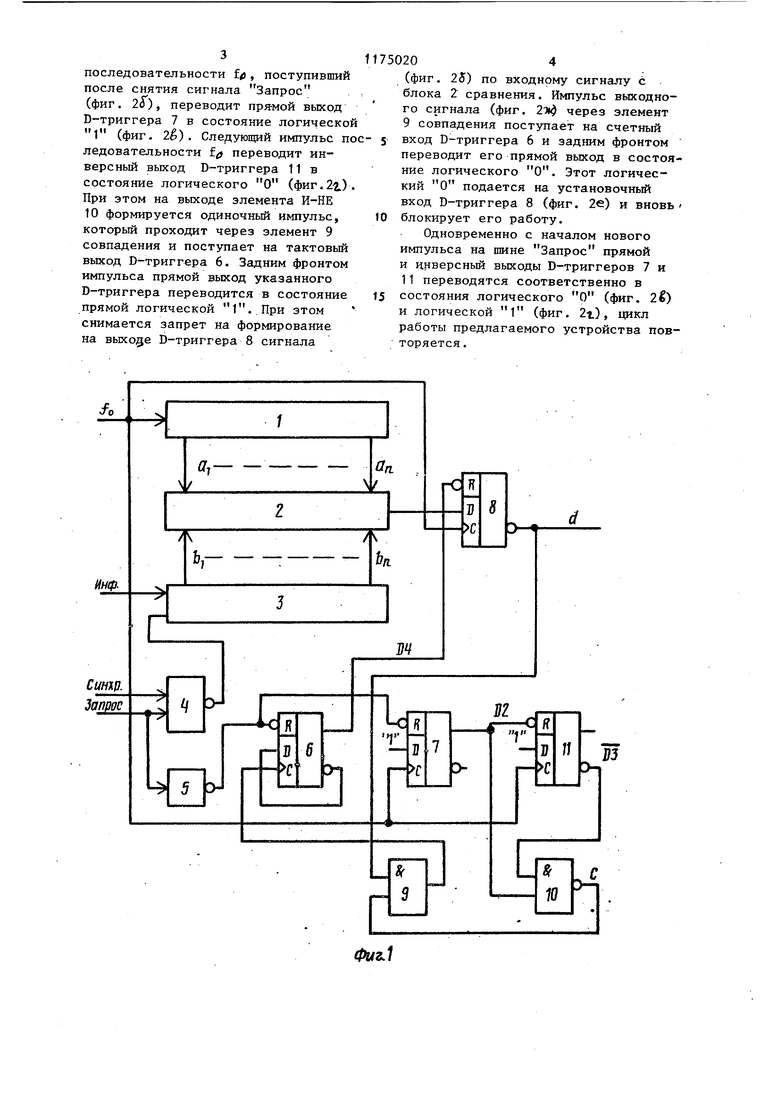

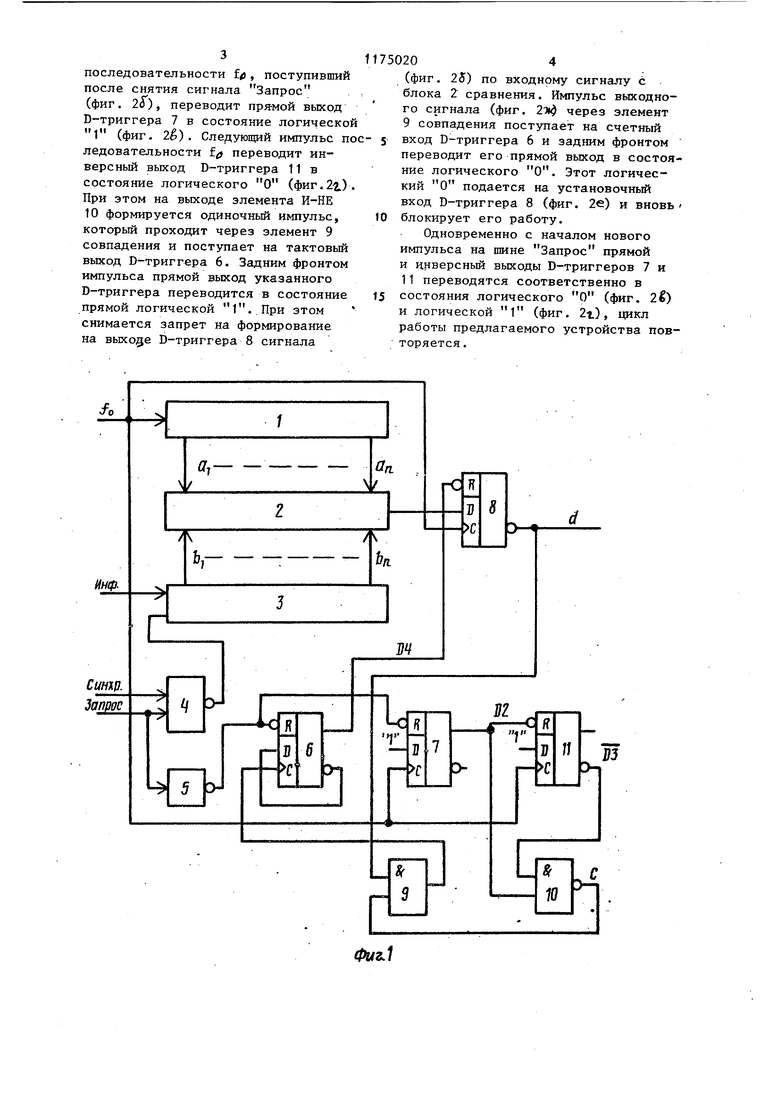

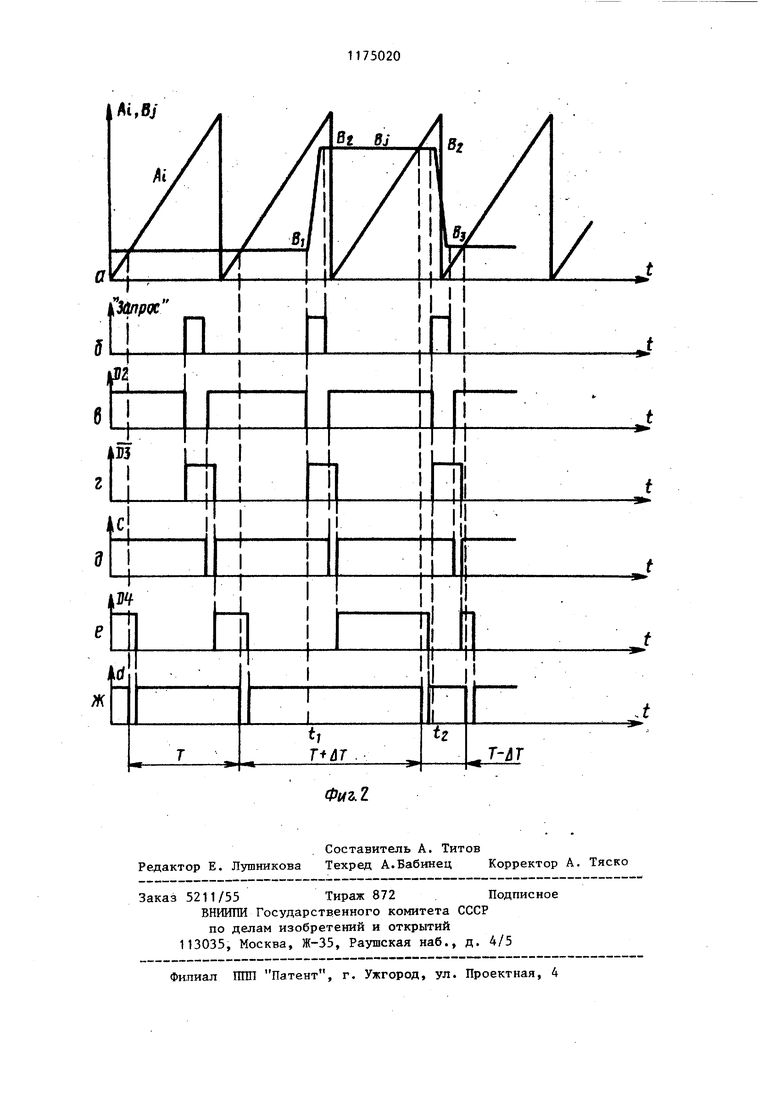

На фиг. 1 приведена функциональная схема предлагаемого устройстваJ на фиг. 2 - диаграммы работы устройства.

Устройство регулируемой задержки (фиг. 1) содержит счетчик 1, счетный вход которого подключен к шине опорного сигнала, блок 2 сравнения, первые входы которого подключены к выходам счетчика 1, буферный регистр 3, информационный вход которого соединен с шиной передачи информации, а тактовый вход соединен с выходом первого эдемента И-НЕ 4, первый вход-которого подключен к шине Синхросигнал, а второй его вход подключен к шине сигнала Запрос и входу инвертора 5, выход которого соединен с входами установки триггеров 6 и 7, инверсный выход D-триггера 6 соединен с его информационным входом, а прямой выход соединен с входом установки D-триггера 8, инверсный выход которого подключен к шине выходного сигнала и к первому входу элемента 9 совпадения, выход которого соединен с тактовым входом D-триггера 6, а второй вход элемента 9 совпадения подключен к выходу элемента И-НЕ 10 первый вход ко.торого соединен с инверсным входом D-триггера 11, а второй вход элемента И-НЕ 10 соединен с выходом триггера 7 и входом установки триггера 11, причем тактовые входы В-триггеров 7, 8 и 11 подключены к счетному входу счетчика 1, выход бл-ока 2 сравнения соединен с информационньпу входом D-триггера 8, а информационные входы D-триггеров 7 и 11 подключены к источнику сигнала логической единицы.

Устройство работает следующим образом.

На счетный вход счетчика 1 поступают импульсы с частотой повторения

750202

f . При этом происходит периодическое изменение кода, записанного в счетчике 1 с периодом k/f (фиг.2а:). Текущий код At с выходов разрядов 5 счетчика 1 поступает на первые входы блока 2 сравнения, на вторые входы которого поступает код Вj (фиг.24) с выходов буферного регистра 3. При смене информации в буферном

o регистре 3 на выход элемента И-НЕ А асинхронно с последовательностью импульсов f(, поступает сигнал Запрос .(фиг. 2о), обеспечивающий прохождение на тактовый вход буфер5 ного регистра 3 чар.ез элемент И-НЕ 4 синхроимпульсов, по которым в буферный регистр последовательно заносится код BJ управления задержкой выходного импульса, поступающего с

Q шины Информация на информационный вход буферного регистра 3. Кроме того, сигнал Запрос через инвертор 5 поступает на установочные входы D-триггеров 6 и 7 и переводит их

5 прямые выходы в состояние логический О.

На выходе блока 2 сравнения, синхронно с моментами совпадения входных кодов, формируются импуль- сы с частотой повторения j( fo/k. Кроме полезных импульсов на выходе будут присутствовать паразитные импульсы, наличие которых обусловлено влиянием конечных задержек и времени срабатывания реальных элементов счетчика 1 и блока 2 сравнения. Для фильтрации паразитных импульсов сигнал с выхода блока 2 сравнения поступает на информационный вход D-триггера 8. При этом на его установочном входе действует сигнал установки (фиг. 2е) с прямого выхода D-триггера 6. Он блокирует работу D-триггера 8, при этом на его инверсном выходе устанавливается сигнал логической 1 (фиг.2.3), . который поступает на первый вх.од элемента 9 совпадения и на выход устройства.

0 с выхода D-триггера 7 сигнал логического О (фиг. 2 и) поступает на второй вход элемента И-НЕ 10 и на вход установки D-триггера 11, на инверсном выходе которого формируется сигнал логической 1 (фиг. 2е).

По окончании записи информации в буферный регистр 3 первый импульс 3 последовательности ff, поступивший после снятия сигнала Запрос (фиг. 2), переводит пря-мой выход D-триггера 7 в состояние логической 1 (фиг. 2). Следующий импульс по ледовательности fff переводит инверсный выход D-триггера 11 в состояние логического О (фиг.2) При этом на выходе элемента И-НЕ 10 формируется одиночный импульс, который проходит через элемент 9 совпадения и поступает на тактовый выход D-триггера 6. Задним фронтом импульса прямой выход указанного D-триггера переводится в состояние прямой логической 1..При этом снимается запрет на формирование на выходе D-триггера 8 сигнала 204 (фиг. 25) по входному сигналу с блока 2 сравнения. Импульс выходного сигнала (фиг. 2К через элемент 9 совпадения поступает на счетный вход D-триггера 6 и задним фронтом переводит его прямой выход в состояние логического О. Этот логический О подается на установочный вход D-триггера 8 (фиг. 2е) и вновь блокирует его работу. Одновременно с началом нового импульса на шине Запрос прямой и инверсный выходы D-триггеров 7 и 11 переводятся соответственно в состояния логического О (фиг. 21) и логической 1 (фиг. 2г), цикл работы предлагаемого устройства повторяется.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовращатель | 1986 |

|

SU1394410A1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

| Имитатор провалов напряжения сети | 1989 |

|

SU1691791A1 |

| Устройство сбора данных для оценки числа событий | 1985 |

|

SU1347078A1 |

| Устройство ранжирования чисел | 1987 |

|

SU1425653A1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1596333A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

УСТРОЙСТВО РЕГУЛИРУЕМОЙ ЗАДЕРЖКИ, содержащее счетчик, счетный вход которого подключен к шине входного опорного сигнала, блок сравнения, первые входы которого подключены к выходам счетчика, буфер ный регистр, информационный вход ко- торогЪ соединен с шиной передачи информации, а тактовый вход соединен с выходом первого элемента И-НЕ, первый вход которого подключен к шине Синхросигнал, а второй его вход к шине сигнала Запрос и к входу инветора, причем выход блока сравнения соединен с информационным входом первого D-триггера, тактовый вход которого соединен с счетным входом счетчика и с тактовыми входами второго и третьего В-триггеров а инверсный выход третьего D-триггера подключен к первому входу второго элемента И-НЕ, отличающее,с я тем, что, с целью увеличения допустимой скорости изменения за-держки выходного сигнала при одновременной уменьшении аппаратурного объема, в устройство введены элемент совпадения и четвертый D-триггер, вход установки которого соединен с выходом инвертора и входом установки второго D-триггера, инверсный выход четвертого D-триггера соединен с его информационным входом, а прямой выход соединен с входом усI тановки первого D-триггера, инверсный выход которого подключен к (Л выходной шине устройства, и к перво-му входу элемента совпадения, выход которого соединен с тактовым входом четвертого D-триггера, а второй вход элемента совпадения подключен к выходу второго элемента И-НЕ, второй вход которого соединен с прямым выходом второго D-триггера и с входом установки третьего D-триггера, причем информационные входы второго и третьего D-тригге;ров подключены к источнику сигнала логической едияицы, а выходы буфер1ного регистра соединены с вторыми входами блока сравнения.

| Устройство регулируемой задержки | 1979 |

|

SU873396A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фазовращатель | 1983 |

|

SU1102026A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-23—Публикация

1984-03-27—Подача