Изобретение относится к рад иотех- нике и может быть использовано в качестве дополнительного элемента систем автоматического регулирования по частоте, фазе или временной держке

Цель изобретения - повышение точ™ ности регулировки фазы.

Указанная цель достигается тем, что осуществляется точное управление фазой сигнала низкой частоты на вы™ ходе управляемого делителя частоты. В выходном блоке реализуется цифро- вое суммирование или вычитание сиг- налов с точнорегулируемой фазой низ кой частоты и груборегулируемой фа ЗОЙ высокой частоты с выхода схемы, вращения. На выходе блока формируют- си импульсы, средняя частота следд- вания которых равна сумме или разности высокой и низкой частот, а точность регулировки фазы определяется минимальным дискретом управления фазы низкочастотного сигнала. Это позволяет уменьшить дискрет регулировки фазы сигнала без повьппения частоты опорного сигнала, .

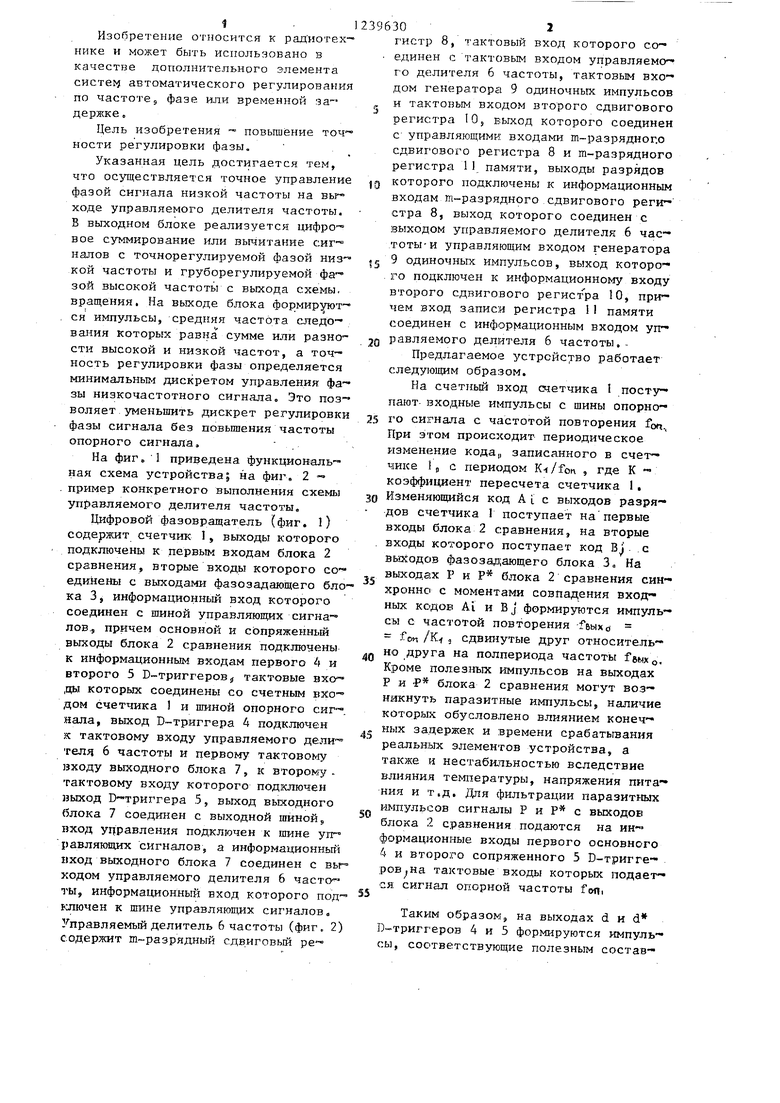

На фиг 1 приведена функциональная схема устройства; на , 2 - . пример конкретного выполнения схемы управляемого делителя частоты.

Цифровой фазовращатель фиг. 1) содержит счетчик 1, выходы которого подключены к первым входам блока 2 сравнения, вторые входы которого со единены с выходами фазозадающего блока 3, информационный вход которого соединен с шиной управляющих сигналов., причем основной и сопряженный выходы блока 2 сравнения подключены к информационным входам первого 4 и второго 5 В-триггеров5, тактовые вхо- ,цы которых соединены со счетным входом счетчика 1 и шиной опорного сигнала, выход В триггера 4 подключен к тактовому входу управляемого теля 6 частоты и первому тактовому входу выходного блока 7, к второму - тактовому входу которого подключен ныход D-триггера 5, выход выходного блока 7 соединен с выходной шиной, вход управления подключен к шине угг° равляющих сигналов, а информационньгй икод выходного блока 7 соединен с вы ходом управляемого делителя 6 часто- ты, информационный вход которого подключен к шине управляющих сигналов Управляемый делитель 6 частоты (фиг 2 содержит т разрядный сдвиговый ре

S

0

5

0

5

0

3

0

5

гистр 8, тактовый вход которого соединен с тактовым входом уп равляемо- го делителя 6 частоты, тактовым входом генератора 9 одиночных импульсов к тактовым входом второго сдвигового регистра 10, выход которого соединен с управляющими: входами т-разрядиог.о сдвигового регистра 8 и т-разрядного регистра 11 памяти, выходы разрядов которого подключены к информационным входам т-разрядного.сдвигового реги- стра 8, выход которого соединен с выходом управляемого делителя 6 час- .тоты-и управляющим входом генератора 9 одиночных импульсов, выход которо- .го подключен к информационному входу второго сдвигового регист ра 10, причем вход записи регистра 11 памяти соединен с информационным входом управляемого делителя 6 частоты. Предлагаемое устройство работает следующим образом.

На счатный вход счетчика I поступают- входные импульсы с шины опорного сигнала с частотой повторения foa., При этом происходит периодическое изменение кода,, записанного в счетчике :t J с периодом K-(/fon , где К - коэффициент пересчета счетчика 1. Изменяющийся код Ale выходов разрядов счетчика 1 поступает на первые входы блока 2 сравнения, на вторые входы которого поступает код - с вьогодов фазозадающего блока 3, На выходах Р и Р блока 2 сравнения синхронно с моментами совпадения входных кодов Ai и Bj формируются импульсы с частотой повторения febtxo fen /К 3 сдвинутые друг относительно друга на полпериода частоты fenxo. Кроме полезз1Ьж импульсов на выходах Р и -Р блока 2 сравнения могут возникнуть паразитные импульсы, наличие которых обусловлено влиянием конечных за.держек и времени срабатьгаання реальных элементов устройства, а также и нзстаби ньностью вследстви« влияния температуры, напряжения пита- НИН и т.д. Для фильтрации паразитных 1 пульсов сигналы Р и Р с выходов блока 2 сравнени.я подаются на ин- формацнонные входы первого основного 4 и второго сопряженного 5 D-тригге- . ровика тактовые входы которых подается: сигнал опорной частоты fon.

Таким образом, на выходах d и d D-триггеров 4 и 5 формируются импульсы, соответствующие полезным соста:в-

ляющим сигналов Р и Р с выходов блока 2 сравнения.

Изменение кода на выходах фазоза- дающего блока 3 в соответствии с поступающим на его вход управлякяцим кодом с шины управляющих сигналов вызывает изменение фазы сигналов d и d на входах D-триггеров 4 и 5 с минимальным дискретом

360 ТГ

хода D-триггера 4 последовательность импульсов поступает на тактовый вход управляемого делителя 6 частоты (фиг. 2) и с него на вход т-разряд- ного сдвигового регистра 8, у кото- m

рого

разрядов, взятых подряд

/m Зшч

1например, от -г- до -г), находятся

в состоянии логической единицы, а остальные его разряды - в состоянии логического нуля. Синхронно с импульсами сигнала d, имеющими частоту следования Гьыхо. происходит последовательное перемещение области еди- ничных состояний к выходу сдвигового регистра 8. Через m периодов час4

тоты -fbbixb выходе последнего разряда т-разрядного сдвигового регистра а следовательно, и на выходе управляемого делителя частоты нулевое логическое состояние изменится на единичное, которое подтверждается в

m

течение у. периодов частоты

Затем вновь на выходе сдвигового регистра 8 и соответственно на выходе управляемого делителя 6 частоты установится состояние логического нуля. При этом синхронно с последующим им™ пульсом последовательности d запустится генератор 9 одиночного импульса, на выходе которого сформируется одиночный импульс длительностью, равной периоду Гьыхо i который поступит на вход второго сдвигового регистра 10,

и с задержкой, равной т 2 периодов

частоты Гьыко , логическая единица по- явится на выходе второго сдвигового регистра 10.и, поступив на управляющие входы сдвигового регистра 8 и регистра 11 памяти, разрешит установку сдвигового регистра 8 в нормальное состояние, и заблокирует изменение информации, записанной в регистр памяти. Следующим импульсом сигнала d

10

(m-й импульс от начала рабочего цикла управляемого делителя 6 частоты) в сдвиговый регистр 8 перепишется начальный код из регистра 11 памяти и цикл работы управляемого делителя частоты повторится сначала При этом на выходе управляемого делителя 6 частоты формируется последовательность импульсов со скважностью Q-2 и частотой следования

, f&blXq ,Г -

m

где Kj - коэффициент деления управляемого делителя частоты, при данной конкретной реализации равен числу разрядов сдвигового регистра 8

Для изменения фазы сигнала частоты F на выходе управляемого делителя 6 частоты достаточно сдвинуть исходное положение области единичного состояния в сдвиговом регистре 8 влево или вправо путем соответствуняцего изменения кода управления фазой в регистре 11 памяти. При этом минимальный дискрет управления фазой сигнала F на выходе управляемого делителя 6 .частоты определяется сдвигом области единичного состояния в сдвиговом регистре 8 на один разряд, что соответствует изменению временного положения импульсов сигнала F относительно исходного на период следования импульсов сигнала d Следовательно, значение минимального дискрета управления фазой сигнала F можно определить из выражения

ITF j

2Т ЛГ m Kj

С выхода управляемого делителя 6 частоты сигнала низкой частоты F подается яа информационный вход выходного блока 7, на тактовые входы которых подаются сигналы d и d с выходов D-триггеров 4 и 5 частотой следования fftbWo 3 на вход управления выходного блока 7 подается сигнал с шины управления, определяющий сумм1г рование или вычитание частот fbbixo F. В случае сложения частот в соответствии с описанием работы выходного блока 7 среднее значение

частоты на выходе вь1ходного блока 7 равно заданному значению частоты fcp

iRbtX

ffrbixo + F fcp ,

a среднее за период частоты F значе ние фазы сигнала частоты fbux относительно сигнала частоты f cip. равно

Hjfl

. i iH

УК. + 1

где 1 - разность фаз попарно взятых импульсов частоты fcp и f е,ых, При изменении фазы сигнала часто- ты F с минимальным дискретом 21

.Кг.

произойдет изменение на единицу зна- чения, равную ;, в зтом случае сред нее значение фазы сигнала частоты fawx -также изменится с минимальным дискретом

(l)-f {,-0 -

Kj. - . 2ТС -1 - - 11

К,

К:

г F

ffiWXo

чек меньше, чем 4 f 2Т

Причем величина изменения фазы А f может быть получена сколь угод но малой при F О, в то время как для известного устройства дискрет регулировки фазы ц может быть полу

f бЫКо. ., f ОН Следовательно, при равных fan и f ъык предпагаемое устройство обеспе- чивайт -повышение точности регулировки фазы..

Формула изобретения

I. Цифровой фазовращатель, содер- жащий счетчик, выходы которого под ключены к первым входам блока срав- нения, вторые входы которого соеди

нены с выходами фазозадающего блока, информационный вход которого соединен с шиной управляющих сигналов, причем основной и сопряженный выходы блока сравнения подключены к информа- ционным входам первого и второго D-трнггеров, тактовые входы которых соедин ены со счетным входом счетчика

О и шиной опорного сигнала, выходы первого и второго D-триггеров подключены соответственно к первому и второ- , му тактовым входам выходного блока, вход уп)авления которого подключен

5 к шине управлугющих сиг налов, а выход выходного блока является выходом фа- зовраш;ателя, отличающий - с я тем, что, с целью повышения точности ретух(ировки фазы, введен

0 управляемый делитель частоты, такто- вый вход которого соединен с выходом первого ЕЬ-триггера, информационный вход управляемого делителя частоты подключен к шине управляющих сигна5 лов, а его выход соединен с информационным входом выходного блока.

2. Фазовращатель по п, 1, о т - ли ч а ю щ и-й,с я тем, что управляемый делитель частоты состоит

0 из первого сдвигового регистра, тактовый вход которого соединен с тактовым входом управляемого делителя частоты, тактовым входом генератора одиночных импульсов и тактовым вхо-

дом второго сдвигового регистра, выход которого соединен с управляющими входами первого сдвигового регистра и регистра памяти,. выходы разрядов которого подключены к инфор

мационным входам первого сдвигового регистра, выход которого соединен с выходом управляемого делителя частоты и управляющим входом;генератора одиночны: : импульсов, выход которого

, подключен к информационному входу второго сдвигового регистра, причем вход записи регистра памяти соединен с информационным входом управляемого

делителя частоты.

Составитель В. Шубин Редактор Л. Гратилло Техред М.Ходанич Корректор Г. Решетник

3391/45

Тираж 728 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. А/5

Производственно «полиграфическое предприятие, г. Ужгород, ул. Проектная 4

Фи&2

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретное фазосдвигающее устройство | 1990 |

|

SU1758582A1 |

| Устройство для анализа неисправностей ЭВМ | 1981 |

|

SU957213A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

| Цифровой фазовращатель | 1986 |

|

SU1394410A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Дискретное фазосдвигающее устройство | 1989 |

|

SU1666970A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

Изобретение относится к радио- технике и может быть использовано в качестве дополнительного элемента систем автоматического регулирования по частоте, фазе или временной задержке. Цель изобретения - повышение точности регулирования фазы. Устройство содержит счетчик 1, блок 2 сравнения, фазозадакнций бЛок 3, D-триг- геры 4 и 5, делитель 6 частоты и выходной блок 7. Цель изобретения достигается благодаря тому, что осуществляется точное управление фазой сигнала низкой частоты на выходе управляемого делителя 6 частоты. В выходном блоке 7 реализуется цифровое суммирование или вычитание сигналов с точнорегулируемой фазой ииз- кой частоты и груборегулируемой фазой высокой частоты с выхода схемы вращения. На выходе блока формируйт- ся импульсы, средняя частота следования которых равна сумме или разности высокой или низкой частот. Точность регулировки фазы определяется минимальным дискретом управления фазы низкочастотного сигнала. Это позволяет уменьшить дискрет ре- . гулировки фазы сигнала без повышения частоты опорного сигнала. 1 з.п. ф-ы, 2 ил. (Л tc со со О) со

| Фазосдвигающее устройство | 1980 |

|

SU1084971A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для освобождения с поста управляемой вручную стрелки | 1933 |

|

SU50576A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-06-23—Публикация

1984-12-17—Подача