которого соединен с входом распределителя импульсов , и блок управления, выходы которого подключены к управляю1 щим входам распределителя импульсов, буферного регистра счетчика числи,теля и блока сравнения кодов, а вход/ соёдинейс входами счетчика коэффициентов цепной дроби, счетчика знамеиатёля и с выходом блока сравнения кодов.

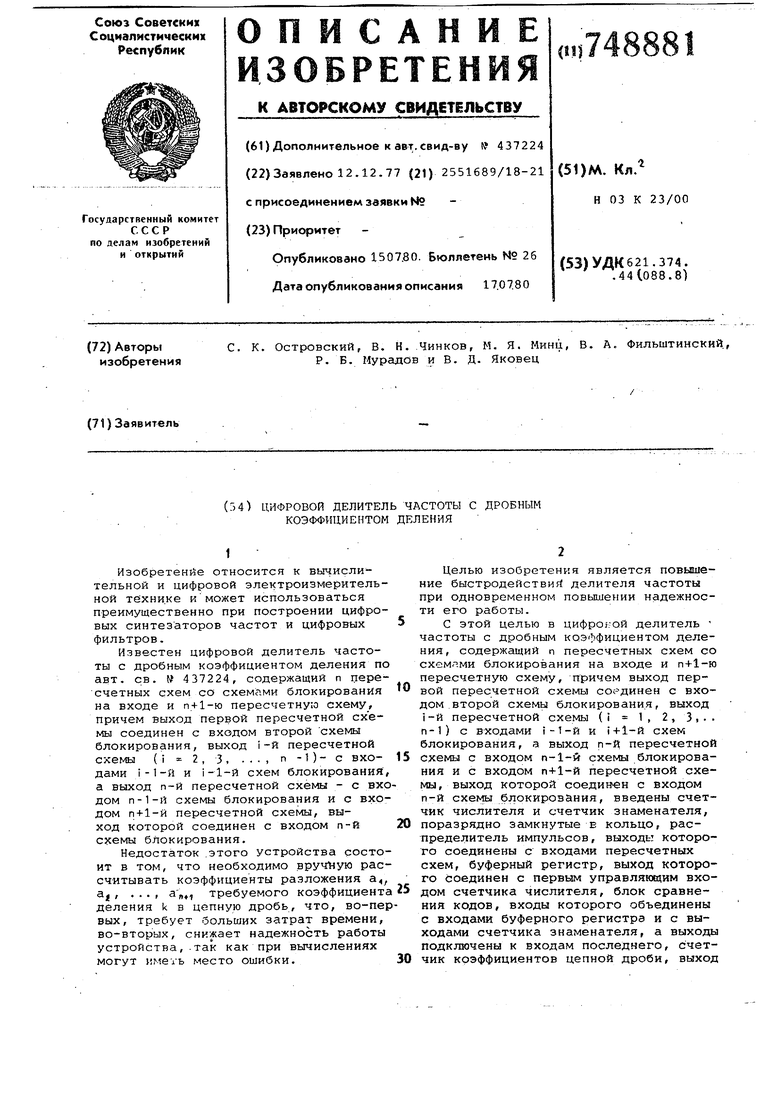

.На чертеже приведена структурная электрическая блок-схема делителя частоты, включающего счетчик 1 числителя, счетчик 2 знаменателя, блок 3 сравнения кодов, буферный регистр 4, счетчик 5 коэффициентов цепной дроби, распределитель б импульсов, блок 7 управления схемы блокирования 8-1-8-п и пересчетные схемы 9-19-(n-f 1) .,:,.,;„-, :

Счетчики 1 и 2 числителя и знаменателя поразрядно связаны, во-первых, друг с другом в замкнутую цепь, вот- вторых, с блоком 3 сравнения кодов. Кроме того, ыходы счетчика знаменателя поразрядно соединены с входами буферного регистра 4. Распределитель б импульсов входом подключён к счетчику 5 коэффициентов цепной дроби, а выходами - к пересчетным схамам 9-1-9-(п+1 ) . -- .

Блок 3 сравнения кодов осуществляет сравнение числителя и знамёнателя коэффициента деления и формирует управляющие воздействие в счетчик 5 коэффициентов цепной дроби. Блок 7 управления предназначен для временной селекции импульсов, обеспечивающих прохождение сигналов в делителе частоты.

Принцип действия описываемого делителя частоты заключается в следующем.

В исходном состоянии счетчик 5 коэффициентов цепной дроби находится в нулевом состоянии, а в счетчики 1 и 2 внесены соответственно знаменатель и числитель дробной части коэффициента деления k.

Первый управляющий импульс поступает в блок 3 сравнения кодов, который сравнивает содержимое счетчика 1 числителя и счетчика 2 знаменателя и формирует управляющие воздействия в зависимости от их величин. Если чиситель больще знаменателя, то блок равнения кодов формирует импульс для переноса значения знаменателя в счетик числителя на вычитание, а также ля записи единицы в счетчик 5.

С помощью второго и последующих мпульсов управления производится поледовательное вычитание знаменателя из величины числителя до тех пор, пока числитель не станет меньше знаменателя. В этом случае блок 3. сравнения кодов формирует импульс конец цикла, который осуществляет пересылку содержимого счетчика 5 коэффициентов цепной дроби в распредепитель 6 импульсов, а счетчика 2 знаменателя в буферный регистр 4.

Следующие два управляющих импульса с помощью буферного регистра производят замену числителя знаменателем и наоборот, т.е. числитель и знаменатель поменяются местами в счет- чиках 1 и 2 и процесс деления может быть продолжен.

Описанное формирование элементов цепной дроби повторяется до появления нуля в счетчике числителя, что свидетельствует о полном разложении заданного коэффициента деления в цепную дробь. При этом управляющий импульс, поступивший в распределитель 6, производит считывание коэффициентов разложения а, а ,..., а„ и перезапись их из задатчика Коэффициентов цепной дроби в пересчетные схемы 9-1-9-(п+1),после чего деЛитель частоты работает аналогично деителю частоты по основному авторскому свидетельству.

Формула изобретения

Цифровой делитель частоты с дробным коэффициейтом деления по авт. св №437224, отличающийся тем, что, с целью повышения быстродействия делителя при одновременном повышении надежности его работы, в нго введены счетчик числителя и счетчик знаменателя, поразрядно замкнутые в кольцо, распределитель импульсов, выходы которого соединены с входами пересчетных схем, буферный регистр, выход которого соединен с первым управляющим входом счетчика числителя, блок сравнения кодов, входы которого объединены с входами буферного регистра и с выходами счетчика знаменателя, а выходы подключены к входам последнего, счётчик коэффициентов цепной дроби, выход которого соединен с входом распределителя импульсов, и блок управления,выходы которого подключены к управляющим вхдам распределителя импульсов, буферного регистра, счетчика чцслите ля и блока сравнения кодов, а вход соединен с входами счетчика коэффициентов цепной дроби, счетчика знаменателя и с выходом блока сравнения кодов.

JkBi tiro3

}- S-f

Jk

9t |e-fg-f

|7-3|-I 3-3

t

3L

h-lSJ#-i

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1977 |

|

SU684744A1 |

| Программируемый делитель частоты следования импульсов | 1980 |

|

SU945998A1 |

| Устройство для деления частоты импульсов с дробным коэффициентом деления | 1977 |

|

SU621101A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1003352A1 |

| Делитель частоты следования импульсов с переменным дробным коэффициентом деления | 1981 |

|

SU953739A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1983 |

|

SU1156252A1 |

| Делитель частоты с дробным коэффициентом деления | 1978 |

|

SU750744A1 |

Авторы

Даты

1980-07-15—Публикация

1977-12-12—Подача