1

Изобретение относится к цифровой вычислительной технике и предназначено для использования в мультипроцессорных системах.

Известны устройства, обеспечивающие последовательный доступ процессоров к общему блоку памяти l . Однако это устройство не может обеспечить неделимого выполнения цикла, состоящего из нескольких обращений процессора к памяти.

Наиболее близким по технической сущности к данному изобретению является устройство, содержащее память, регистры адреса зон, регистр адреса, регистр записи считывания, память команд, блок управления, интерфейс, триггер, элементы И .

Недостатком известного устройства является неэффективное использование памяти и большой объем аппаратуры.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство, содержащее счетчик, первый блок сравнения, четыре элемента ИЛИ, шесть элементов И, содержит приоритетный блок, второй .блок сравнения, пятый элемент ИЛИ,

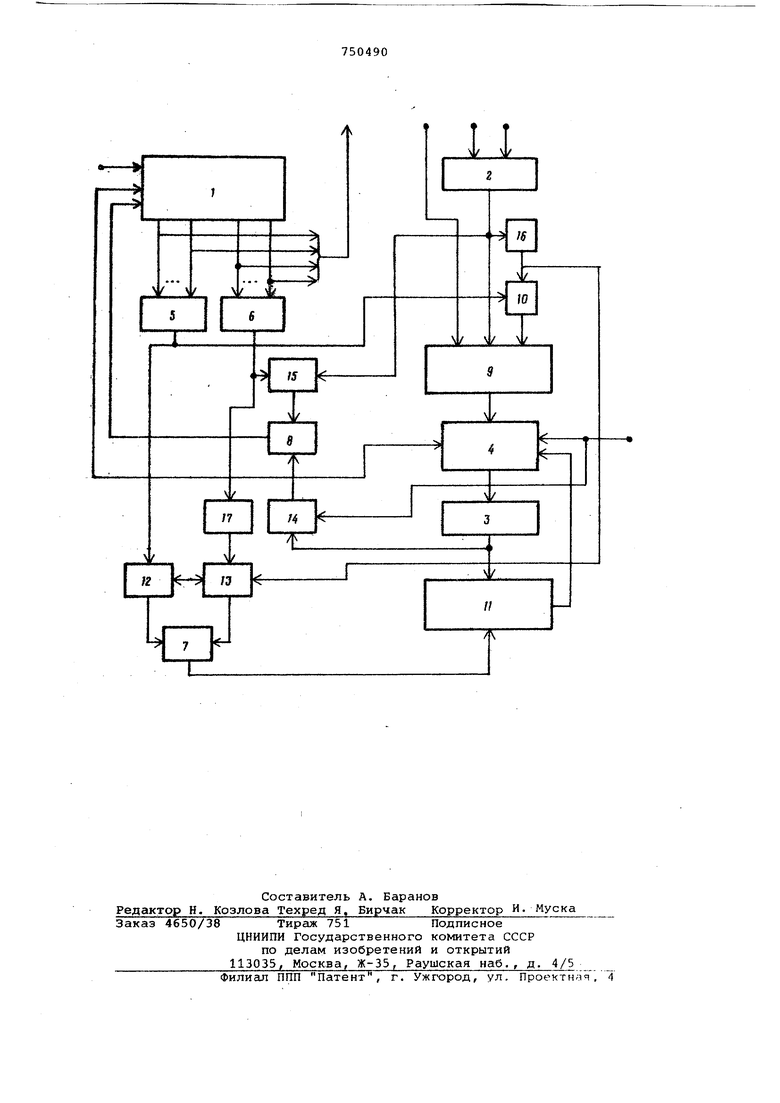

элемент задержки, причем первый вход приоритетного блока является первым входом устройства, второй вход приоритетного блока соединен с первым входом счетчика и является вторым входом устройства, третий вход приоритетного блока подключен к выходу первого элемента ИЛИ, первая группа выходов приоритетного блока соединена со входами элемента ИЛИ и является первой группой выходов устройства, вторая группа выходов приоритетного блока подключена ко входам третьего элемента ИЛИ и является, второй группой выходов устройства, выход второго элемента ИЛИ соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход первого и первый вход третьего элементов И объединены и являются третьим входом устройства, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И и является выходом устройства, второй вход четвертого элемента И объединен с первым входом пятого элемента И и подключен к выходу второго блока сравнения, а выход четвертого элемента И соединен со вторым входом счетчика, третий вход которо объединен со вторьом входом пятого э мента И и является четвертым входом устройства, четвертый вход счетчика соединен с выходом пятого элемента ИЛИ, а выход счетчика подключен ко входу второго блока сравнения, пер вый и второй входы первого блока сравнения являются соответственно пятым и шестым входом устройства, выход первого блока сравнения подключен ко входу элемента НЕ, первому входу шестого элемента И и пе вому входу пятого элемента ИЛИ, вт рой вход которого является седьмым входом устройства, а третий вход п того элемента ИЛИ подключен к выходу второго элемента И, второй вх которого объединен со вторым входом третьего элемента И и подключен к выходу элемента НЕ, третий вход тр тьего элемента И соединен с выходом элемента задержки, вход которого о единен со вторым входом шестого эл мента И и соединен с выходом треть его элемента ИЛИ, выход шестого эле мента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента и. На чертеже представлена блок-схе ма устройства. Устройство содержит приоритетный блок 1, выполненный на основе приоритетной, кольцевой или иной схемы временного разделения, первый блок сравнения 2, второй блок сравнения счетчик 4, элементы ИЛИ 5-8, многоразрядную схему ИЛИ 9, элементы И 10-15, элемент НЕ 16, элемент задержки 17, Устройство работает следующим образом. Блок 2 осуществляет селекцию зая вок по их направленности во флажковую зону ЗУ (запоминающее устройство) , а элементы ИЛИ 5,6 - по их принадлежности-соответственно к процессорам или ВУ (внешние устройства) , элементы 9, 10, 11, 16 осуществляют формирование и запись в счетчик 4 установочного кода количества циклов обмена в соответствии с видом обслуживаемой заявки:1 для работы процессора в зоне флажков, 2 - для работы процессора в зоне флажков. Здесь N для работы ВУ вне зоны флажков. Здесь N - код количества циклов обмена, запрашиваемый ВУ. Быстродействие элементов 4 и 11 выбирается таким, чтобы создаваемая или суммарная задержка не превосходила длительности рабочего цикла ЗУ . Элементы 7, 12, 13 осуществляют выдачу в ЗУ управляющего сигнала запроса и блокировку выдачи запроса при выявлении попытки обращений во флажковую зону со стороны ВУ. Элемент задержки 17 предназначен для задержки логического сигнала принадлежности выбранной заявки к ВУ на время работы цепи селекции адреса запроса в ЗУ с целью исключения возможности вьщачи запроса во флажковую зону ЗУ от ВУ. Длительность задержки, создаваемой элементом 17, определяется следующим соотношением: - время срабатывания v-ro элемента; t - время коммутации адресных и управляющих шин ВУ. Блок 3 фиксирует моменты обнуления счетчика 4, а элементы 8, 14,15 осуществляют сброс обслуженной заявки в блоке 1. Быстродействие счетчика 4, блока 3 и элемента И 14 должно быть выбрано таким образом, чтобы создаваемая ими суммарная задержка была бы меньше длительности сигнала ответа ЗУ. Сигнал начального сброса счетчика 4,поступающий на входы общего сброса блока 1, осуществляет установку в ноль регистров этих блоков. При поступлении запросов к ЗУ на вход устройства блок 1 выбирает один из них в соответствии с принятой в нем очередностью и вырабатывает сигнал управления коммутацией, поступающий на выход устройства, осуществляя подключение к ЗУ информационных, адресных и управляющих шин соответствующего процессора или ВУ. Одновременно с этим сигнал с выхода блока 1 поступает- на вход элемента ИЛИ 5, если выбранная заявка исходит от процессора, или на вход элемента ИЛИ 6, если заявка исходит от ВУ. С выхода элемента ИЛИ 5 сигнал поступает на вход элемента ИЛИ 12, подготавливая выдачу в ЗУ сигнала запроса, поступшощего на вход элемента ИЛИ 12 и на вход элемента И 10. С выхода элемента ИЛИ 6 единичный сигнал поступает на вход элемента И 15, подготавливая сброс заявки Вблоке 1 в том случае, если запрос от ВУ направлен в зону флажков, и,через элемент задержки 17, на вход элемента И 13. Адрес запроса в ЗУ, подключенного к нему процессора или ВУ, поступает на вход блока 2 по признаку принещлежности запрашиваемой ячейки к флажковой зоне ЗУ. Единичный сигнал с выхода блока 2, имеющий место в том случае, если адрес запроса в ЗУ принадлежит к зоне флажков, поступает во второй разряд многоразрядного элемента ИЛИ 9,подготавливая на установочном входе счетчика 4 код требуемого в этом случае количества циклов обмена с ЗУ, равный 2, а также на вход элемента НЕ 16 и на вход элемента И 15, с выхода которого он передается через элемент ИЛИ 8 на вход поразрядного сброса блока 1 в том случае, если выбранная заявка, идущая в зону флажков, происходит от ВУ. Если адрес запроса в ЗУ находится вне зоны флажков то нулевой сигнал с выхода блока 2 инвертируется элементом НЕ 16 и поступает на вход эле мента И 10, подготавливая запись в счетчик установочного кода,равного 1, а также на вход элемента И 13. В том случае, если выбранная для обслуживания блоком 1 заявка исходит от ВУ, селекция адресов не производится, а требуемое количество циклов обмена с ЗУ поступает на входы элемента ИЛИ 9 непосредственно от ВУ. Так исходным состоянием счетчик 4 является нулевое состояние, то на выходе блока сравнения на ноль 3 имеет место единичный сигнал, который поступает на входы элементов И 14 и 11, подготавливая последний к выдаче единичного сигнала на вход з писи счетчика 4 после появления на другом его входе сигнала запроса ЗУ, поступающего также на выход уст ройства с выхода элемента ИЛИ 7 в м мент завершения коммутации управляю щих шин выбранного процессора. После записи установочного кода в счет чик 4 нулевой сигнал с выхода блока 2 блокирует передачу сигнала ответа ЗУ, поступающего с входной линии на счетный вход счетчика 4 и на вход элемента И 14, т.е. через элемент ИЛИ 8 на вход поразрядного бло сброса 1 не поступает единичный сигнал до момента повторного обнуле ния счетчика после выполнения установленного счетчиком количества цик лов обмена с ЗУ. После сброса обслу женной заявки в блоке 1 работа устройства повторяется. Применение устройства позволит значительно сократить объем дополнительных аппаратных средств за сч максимального использования аппаратуры, имеющийся в каждом процессоре Формула изобретения Устройство управления доступом к общей памяти, содержащее счетчик, первый блок сравнения, четыре элеме та ИЛИ, шесть элементов И, о т л ичающееся тем, что, с целью упрощения устройства оно содержит приоритетный блок, второй блок срав нения, элемент ИЛИ, элемент задержки, причем первый вход приоритетног блока является первым входом устрой ства, второй вход приоритетного бло ка соединен с первым входом счетчика, и является вторым входом устройства, третий вход приоритетного блока подключен к выходу первого элемента ИЛИ, первая группа выходов приоритетного блока соединена со входами второго элемента ИЛИ и является первой группой выходов устройства, вторая группа выходов приоритетного блока подключена ко входам третьего элемента ИЛИ и является второй группой выходов устройства, выход Второго элемента ИЛИ соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход первого и первый вход третьего элементов ИЛИ объединены и являются третьим входом устройства, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами четвертого элемента.ИЛИ, выход которого соединен с первым входом четвертого элемента И и является выходом устройства, второй вход четвертого элемента И подключен к выходу второго блока сравнения, а выход четвертого элемента И соединен со вторым входом счетчика, третий вход которого объединен со вторым входом пятого элемента И и является четвертым входом устройства, четвертый вход счетчика соединен с выходом пятого элемента ИЛИ, а выход счетчика подключен ко входу второго блока сравнения, первый и второй входы первого блока сравнения являются соответственно пятым и шестым входом устройства, а выход первого блока сравнения подключен ко входу элемента НЕ, первому входу шестого, элемента И и первому входу пятого элемента или; второй вход которого является седьмым входом устройства, а третий вход пятого элемента ИЛИ подключен к выходу второго элемента И, второй вход которого объединен со вторым входом третьего элемента И и подключен к выходу элемента НЕ, третий вход третьего элемента И соединен с выходом элемента задержки, вход которого .объединен со вторым входом шестого элемента И и соединен с выходом третьего элемента ИЛИ, выход шестого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 304580, кл. G 06 F 15/16, 1972. 2.Патент Франции 2123833, кл. G 06 F 15/16, опублик. 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритетного обращения процессоров к общему блоку памяти данных | 1976 |

|

SU682898A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Устройство для временного контроля сигналов интерфейса | 1986 |

|

SU1324028A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

| Электронный мини-орган | 1988 |

|

SU1559376A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

Авторы

Даты

1980-07-23—Публикация

1977-10-04—Подача