Изобретение относится к вычислительной технике и предназначено дпя автоматическбй диагностики сигналов интерфейса Общая шина между вычис- литальными средствами и процессором ЭВМ, а также может быть использовано для настройки вычислительного комплекса, когда интерфейс достигает максимально допустимую дойну.

Цель изобретения - повышение дос- товерности контроля.

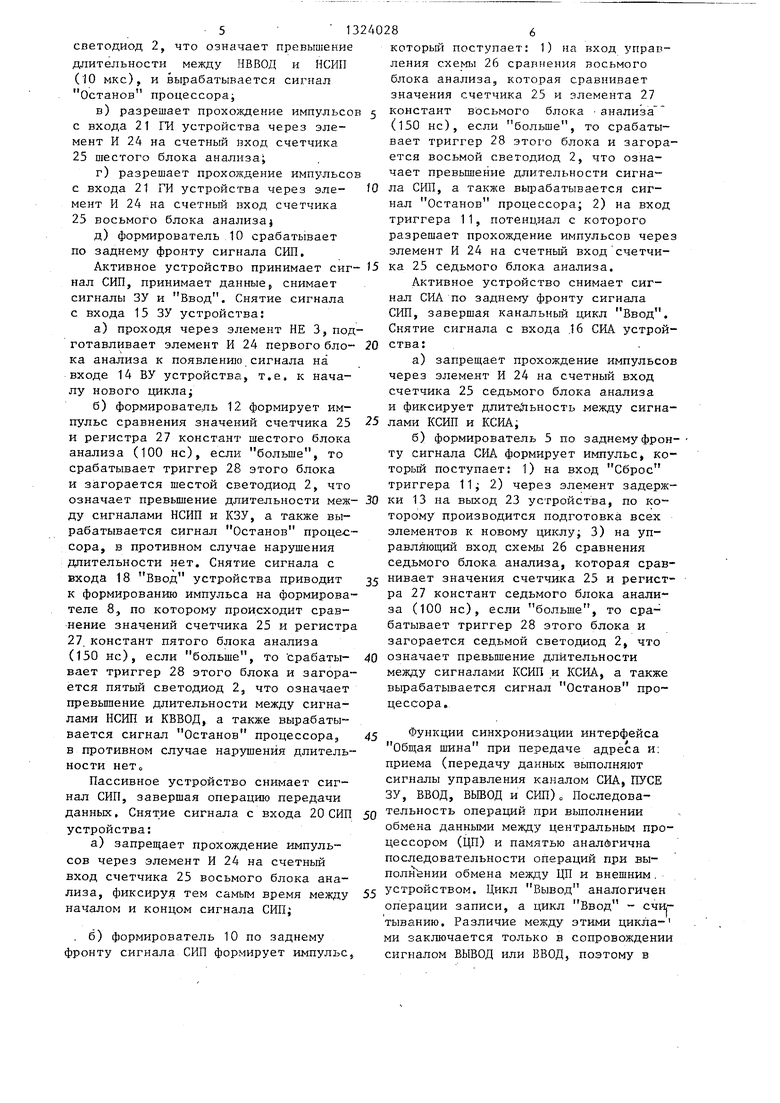

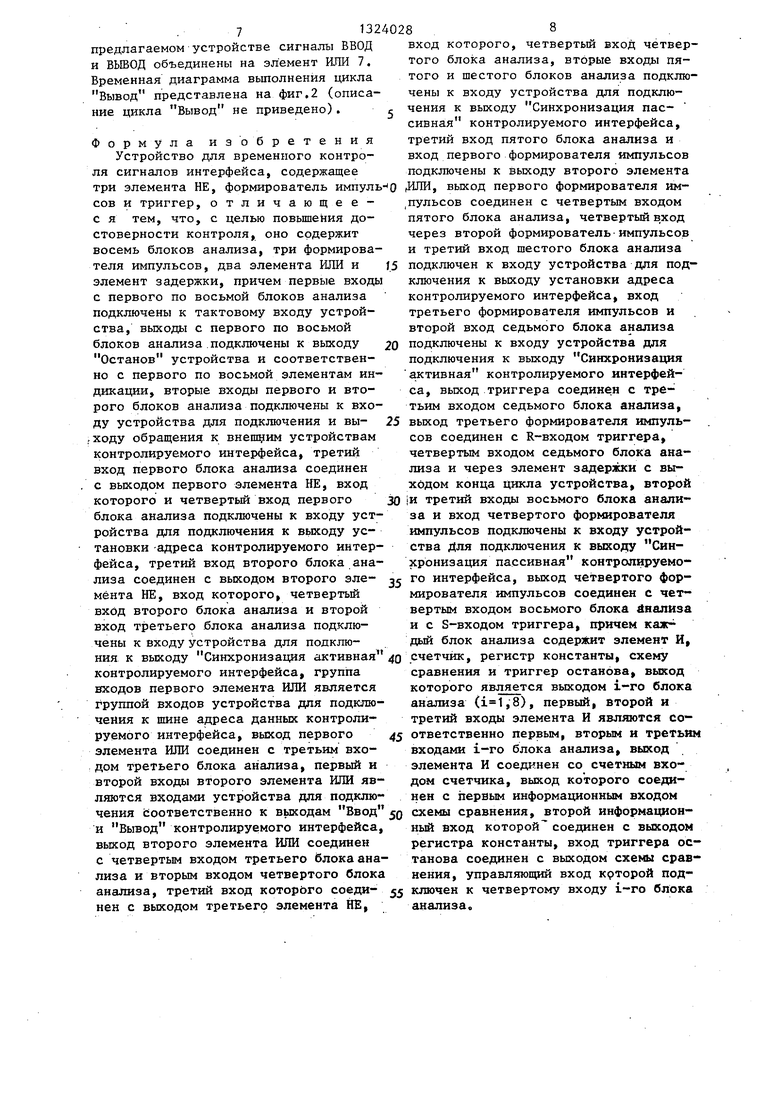

На фиг.1 представлена структурная схема устройства для временного контроля сигналов интерфейса; на фиг.2- временные диаграммы работы устройс т- ва в циклах Ввод и Вывод интерфейса Общая

Устройство содержит восемь блоков анализа 1.1-1.8, восемь элементов 2„1-2,8 индикации, первый 3 и второй

4элементы НЕ, первьш: формирователь

5импульсов, два элемента ИЛИ 6 и 7, третий формирователь 8 импульсов, третий элемент НЕ 9, четвертьлй формирователь 10 импульсов, триггер 11, второй формирователь 12 импульсов, элемент 13 задержки, входы с 14 по

20устройства подключены к выходам контролируемого интерфейса Общая шина, за сигналами которой осущест- вляет контроль предлагаемое устройство г.вьк од 14 ВУ - обращение к внешним устройствам, выход 15 ЗУ установки адреса сигнализирует о том, что

a линиях ДА (00 +15) интерфейса установлен адресу выход 16 СИЛ (Синхронизация активная) предназначен для запоминания адреса во входной логике выбранного устройства; выход 17 ДА - 16 линий адреса (данные)j выход 18 Ввод - готовность принять данные- выход 19 Вывод - на линиях ДА (00 + 15) помещены истинные данные j выход 20 СИП (Синхронизация пассивная) - завершение операции передачи приема данньк тактовый вход

21ГИ устройства подключен к генератору импульсов (не показан); выход 22 останов устройства останавливает работу процессораi вьгкод 23 Конец цикла устройства - подготовка устройства к HOBoijry циклу работы.

На структурной схеме устройства линии сброса не показаны.

Д-й блок 1 анализа содержит элемент И 24, счетчик 25, схему 26 сравнения, регистр 27 константы и триггер 28 останова.

Устройство для временного контроля сигналов интерфейса работает следующим образом.

В начальный момент все счетчики и триггеры установлены в нулевое состояние (цепи установки не показаны) при этом на шинах интерфейса имеет место нулевой потенциал. Регистры констант имеют различные значения и зависят от контролируемого временного интервала.

Для выполнения любой команды процессору требуется вьшолнить хотя бы одну операцию обращения к интерфейсу Направление передачи при выполнении операций обмена данными определяется по отношению к активному устройству. При выполнении цикла Ввод данные передаются от пассивного устройства к активному. Предлагаемое устройство всегда остается пассивным наблюдателем при правильной последовательности сигналов, а при нарушении ее вырабатывает сигнал Останов, который останавливает работу процессора,

Сигналы по ходу 21 ГИ устройства поступают постоянно, Из интерфейса Общая шина на вход 17 ДА и вход 14 ВУ устройства одновременно поступают сигналы. Сигналы входа. 17 ДА через элемент ИЛИ 6 поступают на третий вход третьего блока анализа и подготавливают его элемент И 24 к работе, а сигнал с входа 14 ВУ устройства:

а)разрешает прохождение импульсов (с входа 21 ГИ) через элемент И 24 первого блока анализа, так как синал на входе 15 ЗУ устройства отсутствует, на счетный вход счетчика 25 импульсов, значение которого определяет временной интервал между началом сигналов на входах 14 ВУ и 15 ЗУ (НВУ - НЗУ) в текущем цикле работы устройства}

б)разрешает прохождение импульсов через элемент И 24 второго блока анализа, так как сигнал на входе 16 СИА устройства отсутствует, на счетный вход счетчика 25 импульсов, значение которого определяет временной интервал между началом сигналов на входах 14 ВУ и 16 СИА (НВУ - НСИА) в текущем цикле работы устройства.

Затем с интервалом не менее 75 не активное устройство вьфабатывает сигнал ЗУ, который поступает на вход 15 ЗУ устройства:

-j5

а)проходит через элемент НЕ 3 и запрещает прохождение импульсов через элемент И 24 первого блока анализаj

б)подготавливает элемент И 24 шестого блока анализаj

в)формирователь 12 вьфабатывает импульс по заднему фронту сигнала ЗУ;

г)разрешает- сравнение текущего значения счетчика первого блока анализа с константой контролируемого ин-)о сигнал Ввод, сигнализируя о том, тервала (75 не). Если меньше или

равно, то срабатывает триггер 28 первого блока анализа, загорается первый светодиод 2, что свидетельствует о малой длительности между сигналами НВУ - НЗУ, и вырабатывается сигнал Останов процессора. По адре- су в счетчике команд процессора оператор устанавливает, с каким адресом внешнего устройства работала програм- д ма. Это помогает оператору установить участок интерфейса (от процессора до данного устройства), на котором произошло нарушение интервала. Сброс триггеров 28 всех блоков анализа про-25 тывает триггер 28 третьего блока ана- изводится оператором вручную. Если лиза л загорается третий светодиод 2, больше, то нарушения в последова- что свидетельствует о малой длитель- тельности сигналов НВУ - НЗУ нет. ности между сигналами НСИА и КДА, а

Не менее чем через 150 не после также вырабатывается сигнал Останов установки адреса активное устройство зо процессора, если больше то.нару- вьфабатывает сигнал СИА, который по шения последовательности сигналов ступает на вход 16 СИА устройства:

а) проходя через элемент НЕ 4, запрещает прохождение импульсов через

д) при этом формирователь 5 не срабатывает, так как он вырабатывает импульс по заднему фронту сигнала СИА.

Пассивное устройство начинает дешифрировать адрес и запоминает его. Активное устройство через 100 не после выработки СИА снимает адрес с ДА, очищает линию ВУ и вырабатывает

что оно готово принять данные от пассивного устройства, и ожидает поступления сигнала СИП. Снятие адреса с входа 17 ДА устройства запрещает про- J5 хождение импульсов через элемент И 24 в счетчик 25 в третьем блоке анавремени между началом CliA и концом ДА. Сигнал с входа 18 Ввод устройства через элемент 7:

а) разрешает сравнение значений счетчика 25 и регистра 27 констант в третьем блоке анализа и если меньше или равно (100 не), то ерабаНСИА и КДА HeTj

б)разрешает прохождение импульсов через элемент И 24 на счетный вход счетчика 25 четвертого блока анализа, так как инвертирован сигнал входа 20 СИП;

элемент И 24 второго блока анализа, фиксируя время в счетчике между сигналами входа 14. ВУ и началом сигнала по входу 16 СИА;

б)разрешает сравнение значений счетчика 25 и регистра 27 констант (150 не) во втором блоке анализа и если меньше или равно, то ераба- тывает триггер 28 и загорается второй светодиод 2, что свидетельствует о малой длительности между сигналами начало ВУ (НВУ) - начало СИА (НСИА), и вырабатывается сигнал Останов, а если больше то нарушения в последовательности сигналов НВУ и НСИА нет

.

в)разрешает прохождение импульеов с входа 21 ГИ через элемент И 24 на счетный вход счетчика 25 третьего блока анализа, которьй начинает отсчет контрольного времени от начала СИА (НСИА) до конца ДА (КДАТ}

г)подготавливает элемент И 24 седьмого блока анализа к работеj

сигнал Ввод, сигнализируя о том,

д) при этом формирователь 5 не срабатывает, так как он вырабатывает импульс по заднему фронту сигнала СИА.

Пассивное устройство начинает дешифрировать адрес и запоминает его. Активное устройство через 100 не после выработки СИА снимает адрес с ДА, очищает линию ВУ и вырабатывает

сигнал Ввод, сигнализируя о том,

тывает триггер 28 третьего блока ана- лиза л загорается третий светодиод 2, что свидетельствует о малой длитель- ности между сигналами НСИА и КДА, а

что оно готово принять данные от пассивного устройства, и ожидает поступления сигнала СИП. Снятие адреса с входа 17 ДА устройства запрещает про- хождение импульсов через элемент И 24 в счетчик 25 в третьем блоке анатывает триггер 28 третьего блока ана- лиза л загорается третий светодиод 2, что свидетельствует о малой длитель- ности между сигналами НСИА и КДА, а

времени между началом CliA и концом ДА. Сигнал с входа 18 Ввод устройства через элемент 7:

а) разрешает сравнение значений счетчика 25 и регистра 27 констант в третьем блоке анализа и если меньше или равно (100 не), то ерабатакже вырабатывается сигнал Останов о процессора, если больше то.нару- шения последовательности сигналов

0

0

НСИА и КДА HeTj

б)разрешает прохождение импульсов через элемент И 24 на счетный вход счетчика 25 четвертого блока анализа, так как инвертирован сигнал входа 20 СИП;

в)подготавливает элемент И 24 пятого блока анализа;

г)формирователь 8 работает по заднему фронту сигнала Ввод.

Пассивное устройство помещает данные по линии ДА, которые не поступают на вход предлагаемого устройства, и вырабатывает сигнал СИП, поетупаю- :щий на вход 20 СИП уетройетва и еиг-, нализирующий о том, что данные нахо- дятся в канале.

Сигнал с входа 20 СИП уетройетва:

а)проходя через элемент НЕ 9, запрещает прохождение импульеов через элемент И 24 четвертого блока анализа, т.е. оетанавливает счетчик 25 этого блока;

б)разрешает сравнение значений счетчика 25 и элемента 27 констант четвертого блока анализа, если больше (10 мкс), то срабатывает триггер этого блока, загорается четвертый

5

светодиод 2, что означает превышение длительности между НВВОД и НСИП (10 мкс), и вырабатывается сигнал Останов процессора;

в)разрешает прохождение импульсов с входа 21 ГИ устройства через элемент И 24 на счетный вход счетчика

25 шестого блока анализа

г)разрешает прохождение импульсов с входа 21 ГИ устройства через элемент И 24 на счетный вход счетчика

25 восьмого блока анализаj

д)формирователь 10 срабатывает по заднему фронту сигнала СИП,

которьш поступает: 1) на вход управления схемы 26 сравнения восьмого блока анализа., которая сравнивает значения счетчика 25 и элемента 27

констант восьмого блока -анализа (150 не), если больше, то срабатывает триггер 28 этого блока и загорается восьмой свегодиод 2, что означает превьшгение длительности сигна-

10 ла СИП, а также вырабатывается сигнал Останов процессора; 2) на вход триггера 11, потенциал с которого разрешает прохождение импульсов через элемент И 24 на счетный вход счетчиАктивное устройство принимает сиг- )5 ка 25 седьмого блока анализа, нал СИП, принимает данные снимает Активное устройство снимает сигсигналы ЗУ и Ввод. Снятие сигнала с входа 15 ЗУ устройства:

а)проходя через элемент НЕ 3, подготавливает элемент И 24 первого бло- 20 ка анализа к появлению сигнала на входе 14 ВУ устройства, т.е. к началу нового цикла

б)формирователь 12 формирует импульс сравнения значений счетчика 25 и регистра 27 констант шестого блока анализа (100 не), если больше, то срабатывает триггер 28 этого блока

и за.горается шестой светодиод 2, что означает превышение длительности между сигналами НСИП и КЗУ, а также вырабатывается сигнал Останов процессора, в противном случае нарушения длительности нет. Снятие сигнала с входа 18 Ввод устройства приводит к формированию импульса на формирователе 8, по которому происходит сравнал СИА по заднему фронту сигнала СИП, завершая канальный цикл Ввод. Снятие сигнала с входа .16 СИА устройства:

а)запрещает прохождение импульсов через элемент И 24 на счетный вход счетчика 25 седьмого блока анализа

и фиксирует длительность между сигиа- 25 лами КСИП и KCИAi

б)формирователь 5 по заднему фрон ту сигнала СИА формирует импульс, ко торый поступает: 1) на вход Сброс триггера 11 2) через элемент задерж

30 ки 13 на выход 23 устройства, по ко торому производится подготовка всех элементов к новому циклу; 3) на управляющий вход схемы 26 сравнения седьмого блока анализа, которая срав

j нивает значения счетчика 25 и регист ра 27 констант седьмого блока анализа (100 не), если больше, то сранение значений счетчика 25 и регистра батывает триггер 28 этого блока и 27. констант пятого блока анализа загорается седьмой светодиод 2, что (150 не), если больше, то срабаты- 40 означает превьшение длительности вает триггер 28 этого блока и загора- между сигналами КСИП и КСИА, а также ется пятый светодиод 2, что означает превьппение длительности между сигналами НСИП и КЕВОД, а также вырабаты45

вырабатывается сигнал Останов про цессора.

вается сигнал Останов процессора, в противном случае нарушения длительности нет о

Пассивное устройство снимает сигнал СИП, завершая операцию передачи данных. Снятие сигнала с входа 20 СИП устройства:

а) запрещает прохождение импульсов через элемент И 24 на счетный вход счетчика 25 восьмого блока анализа, фиксируя тем самым время между началом и концом сигнала СИП;

. б) формирователь 10 по заднему фронту сигнала СИП формирует импул1зС5

50

Функции синхронизации интерфейса Общая шина при передаче адреса и: приема (передачу данных вьтолняют сигналы управления каналом СИА, ПУСЕ ЗУ, ВВОД, ВЫВОД и СШ)о Последовательность операций при выполнении обмена данными между центральным процессором (ЦП) и памятью аналйгична последовательности операций при вы- полн ении обмена между ЦП и внешним . г устройством. Цикл Вывод аналогичен операции записи, а цикл Ввод - счи,- тыванию. Различие между этими циклами заключается только в сопровождении сигналом ВЫВОД или ВВОД, поэтому в

которьш поступает: 1) на вход управления схемы 26 сравнения восьмого блока анализа., которая сравнивает значения счетчика 25 и элемента 27

констант восьмого блока -анализа (150 не), если больше, то срабатывает триггер 28 этого блока и загорается восьмой свегодиод 2, что означает превьшгение длительности сигна-

ла СИП, а также вырабатывается сигнал Останов процессора; 2) на вход триггера 11, потенциал с которого разрешает прохождение импульсов через элемент И 24 на счетный вход счетчи

нал СИА по заднему фронту сигнала СИП, завершая канальный цикл Ввод. Снятие сигнала с входа .16 СИА устройства:

а)запрещает прохождение импульсов через элемент И 24 на счетный вход счетчика 25 седьмого блока анализа

и фиксирует длительность между сигиа- лами КСИП и KCИAi

б)формирователь 5 по заднему фронту сигнала СИА формирует импульс, который поступает: 1) на вход Сброс триггера 11 2) через элемент задерж

ки 13 на выход 23 устройства, по ко торому производится подготовка всех элементов к новому циклу; 3) на управляющий вход схемы 26 сравнения седьмого блока анализа, которая сравнивает значения счетчика 25 и регистра 27 констант седьмого блока анализа (100 не), если больше, то срабатывает триггер 28 этого блока и загорается седьмой светодиод 2, что означает превьшение длительности между сигналами КСИП и КСИА, а также

вырабатывается сигнал Останов про цессора.

батывает триггер 28 этого блока и загорается седьмой светодиод 2, что означает превьшение длительности между сигналами КСИП и КСИА, а также

Функции синхронизации интерфейса Общая шина при передаче адреса и: приема (передачу данных вьтолняют сигналы управления каналом СИА, ПУСЕ ЗУ, ВВОД, ВЫВОД и СШ)о Последовательность операций при выполнении обмена данными между центральным процессором (ЦП) и памятью аналйгична последовательности операций при вы- олн ении обмена между ЦП и внешним . устройством. Цикл Вывод аналогичен операции записи, а цикл Ввод - счи,- тыванию. Различие между этими цикла и заключается только в сопровождении сигналом ВЫВОД или ВВОД, поэтому в

предлагаемом устройстве сигналы ВВОД и ВЫВОД объединены на элемент КПИ 7. Временная диаграмма выполнения цикла Вывод представлена на фиг,2 (описание цикла Вывод не приведено).

Формула изобретения Устройство для временного контроля сигналов интерфейса, содержащее

три элемента НЕ, формирователь импуль- о ДЛИ, выход первого формирователя имсов и триггер, отличающее- с я тем, что, с целью повьшейия достоверности контроля, оно содержит восемь блоков анализа, три формирователя импульсов, два элемента ИЛИ и J5 подключен к входу устройства для под- элемент задержки, причем первые входы ключения к выходу установки адреса с первого по восьмой блоков анализа контролируемого интерфейса, вход подключены к тактовому входу устройства, выходы с первого по восьмой

третьего формирователя импульсов и второй вход седьмого блока анализа

20 подключены к входу устройства для

блоков анализа.подключены к выходу Останов устройства и соответственно с первого по восьмой элементам индикации, вторые входы первого и второго блоков анализа подключены к входу устройства для подключения и вы- 25 выход третьего формирователя импуль- ,ходу обращения к внепщим устройствам сов соединен с R-входом триггера контролируемого интерфейса, третий вход первого блока анализа соединен . с выходом первого элемента НЕ, вход которого и четвертый вход первого блока анализа подключены к входу устройства для подключения к вькоду установки адреса контролируемого интерфейса, третий вход второго блока анаподключения к выходу Синхронизация активная контролируемого интерфейса, выход триггера соединен с третьим входом седьмого блока анализа,

четвертым входом седьмого блока анализа и через элемент задержки с выходом конца Цикла устройства, второй 30 {И третий входы восьмого блока анализа и вход четвертого формирователя импульсов подключены к входу устройства Для подключения к выходу Синхронизация пассивная контролируемо- лиза соединен с выходом второго эле- эс го интерфейса, выход четвертого фермента НЕ, вход которого, четвертый мирователя импульсов соединен с чет- вход второго блока анализа и второй вертым входом восьмого блока Анализа вход третьего блока анализа подклю- и с S-входом триггера, причем каж- чены к входу устройства для подклю- дый блок анализа содержит элемент И, ния к выходу Синхронизация активная 40 . ГЧ ИК регистр константы, схему контролируемого интерфейса, группа сравнения и триггер останова, выход входов первого элемента ИЛИ является которого является выходом i-ro блока группой входов устройства для подклю- анализа (,8), первый, второй и чения к шине адреса данных контроли- третий входы элемента И являются со- руемого интерфейса, выход первого 5 ответственно первым, вторым и третьим элемента ИЛИ соединен с третьим вхо- входами i-ro блока анализа, выход дом третьего блока анализа, первый и элемента И соединен со счетным вхо- второй входы второго элемента ИЛИ яв- дом счетчика, выход которого соеди- ляются входами устройства для подклю- ней с первым информационным входом чения Соответственно к выходам Ввод о схемы сравнения, второй информацион- и Вьгаод контролируемого интерфейса, ный вход которой соединен с выходом вькод второго элемента ИЛИ соединен регистра константы, вход триггера ос- с четвертым входом третьего блока ана- танова соединен с выходом схемы срав- лиза и вторым входом четвертого блока нения, управляющий вход крторой под- анализа, третий вход которого соеди- 5 ключен к четвертому входу i-ro блока нен с выходом третьего элемента НЕ, анализа.

вход которого, четвертый вход четвертого блока анализа, вторые входы пятого и шестого блоков анализа подключены к входу устройства для подключения к выходу Синхронизация пассивная контролируемого интерфейса, третий вход пятого блока анализа и вход первого формирователя импульсов подключены к выходу второго элемента

,пульсов соединен с четвертым входом пятого блока анализа, четвертый вход через второй формирователь-импульсов и третий вход шестого блока анализа

подключен к входу устройства для по ключения к выходу установки адреса контролируемого интерфейса, вход

третьего формирователя импульсов и второй вход седьмого блока анализа

20 подключены к входу устройства для

25 выход третьего формирователя импуль- сов соединен с R-входом триггера

подключения к выходу Синхронизация активная контролируемого интерфейса, выход триггера соединен с третьим входом седьмого блока анализа,

25 выход третьего формирователя импуль- сов соединен с R-входом триггера

четвертым входом седьмого блока анализа и через элемент задержки с выходом конца Цикла устройства, второй 30 {И третий входы восьмого блока анализа и вход четвертого формирователя импульсов подключены к входу устройства Для подключения к выходу Син

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительных машин | 1988 |

|

SU1580385A1 |

| Устройство для контроля последовательности выполнения модулей программ | 1986 |

|

SU1462325A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1988 |

|

SU1594555A2 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для контроля хода программы | 1983 |

|

SU1236487A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для отладки программ | 1984 |

|

SU1246100A1 |

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

| Устройство для сопряжения ЭВМ | 1991 |

|

SU1837306A1 |

Изобретение относится i вычислительной технике и предназначено для автоматической диагностики сигналов интерфей&а Общая шина. Цель изобре.тения - повышение достоверности контроля. Устройство для временного контроля сигналов интерфейса содержит три элемента НЕ 3,4,9, триггер 11, восемь блоков анализа 1.1-1.8, восемь .элементов индикации 2.1-2.8, формирователи импульсов 5,8,10 и 12, два элемента ИЛИ 6 и 7, элемент задержки 13. Устройство имеет возможность осуществлять временную диагностику взаимного расположения сигналов относительно друг друга, а также .контролировать их длительность, что приводит не только к значительному сокращению времени на настройку вычислительного комплекса, но и позволяет повысить устойчивость работы интерфейса к случайным обоям и помехам во время эксплуатации вычислительного комплекса. 2 ил. i (Л 75 1®гв

| Устройство для контроля последовательности импульсов | 1982 |

|

SU1070556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для программной диагностики каналов ввода-вывода и интерфейса | 1980 |

|

SU932498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-15—Публикация

1986-02-06—Подача