Изобретение относится к аналогоШ1фровой вычислительной технике и технике аналого-цифрового преобразования.

Известно устройство аналого-цифрового преобразования авойным интегрированием L МВ этом устройстве . преобрааование напряжения в коц осуществляется путем двухтактового интегрирования.

Недостатком устройства 5шляется низкая точность целения, обусловленная тем, что вьосоаной сигнал зависит от длительности интервала интегрирования.

Наиболее близким техническим решением является устройство оля целения сигналов, содержащее два ключа, интегратор, генератор интервала времени,компаратор, элемент И, генератор импульсов стандартной частоты, цифровой индикаторный блок и генератор тактовых импульсов 2.

Недостатком этого устройства также является невысокая точность деления-, так как зависимость выходного сигнала

ОТ длительности интервала интегрирования в данном устройстве устраняегся за счет введения в устройство генератора сздительности интервала Т COttSt. Это вызьюает и дополнительные аппаратурные затраты.

Целью изобретения является повышение точности целения путем исключения зависимости выходного сигнала от интервала интегрировани$).

10

Поставленная цель достигается тем, что в целительное устройство, содержащее первый ключ, первый вход которого является входом делимого устройства, второй ключ , первый вход которого является входом целителя устройства, первый интегратор, первый вход которого подключен к выходу первого ключа, компаратор, один вход которого подключен к

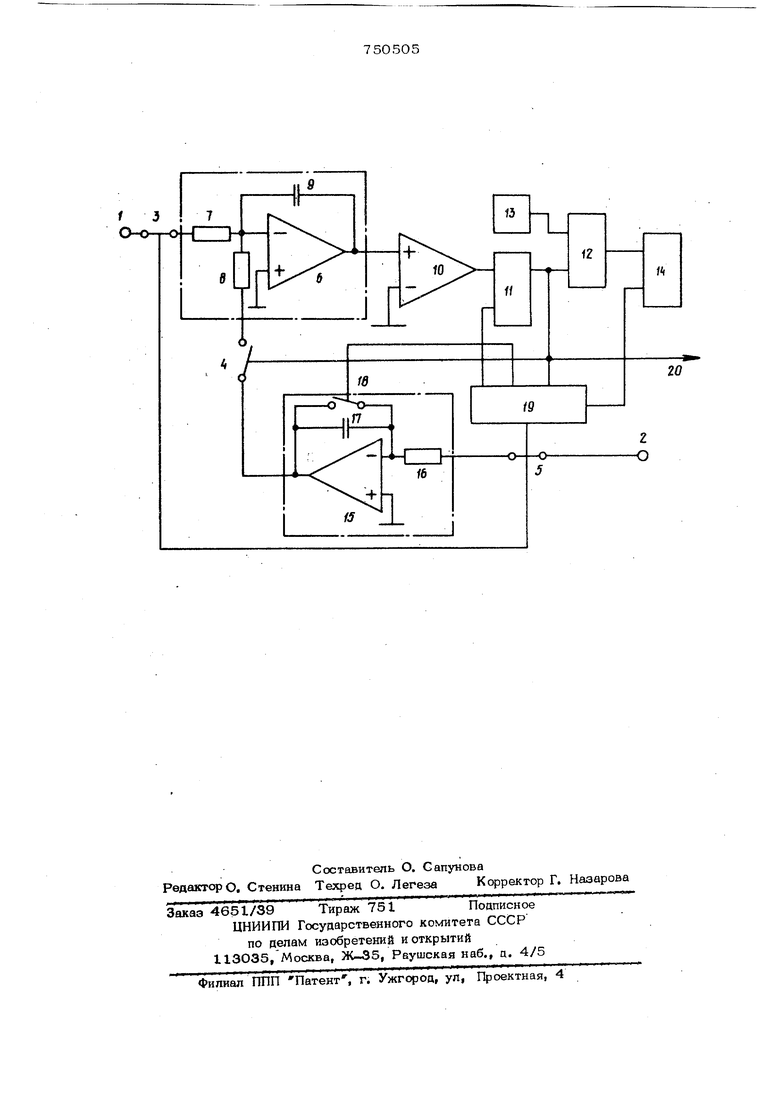

20 вьрсоду интегратора, а другой вход к ши- не нулевого потенциала, триггер , входкоторого подключен к выходу компаратора, элемент И, первый вход: которого подключен к выходу триггера, .генератор импуль сов стабильной частоты, выход которого подключен ко второму входу элемента И, выход которого подключен ко входу цифрового иншисагорного блока, генератор тактовых импульсов, вьссоаы которого подключены .к управляющим входам всех ключей, элемента И и цифрового индикатсрного блока, дополнительно введены вт рой интегратор, в обратную связь которо го включен ключ сброса, вход которого .подключен к выходу втфого ключа, третий ключ, первый вход которого подключе к выходу второго интегратфа, а выход ко второму входу первого интегратора. Блок-ч;хема делительного устройства представлена на чертеже. Устройство содержит вход I напряжения делимого, вход 2 напряжения делител ключи 3, 4 и 5, первый интегратор 6 входными масштабными резисторами 7 и 8 и интегрирующим конденсатором 9,компарато 10,триггер 11, элемент И 12, генератор 13 импульсов стабильной частоты, цифровой индикаторный блок 14, второй ингегратар 15 с входным масштабным резистором 16, интегрирующим конденсатором 17 и ключом сброса 18, тактовый генератор 19, выход 2О интервала. Устройство работает следующим образом. В начальном состоянии выходные нагряжения интеграторов 6 и 15 равны ну лю/1 14НтТ (О) О/. Ключи 3, 4 и 5 разомкнуты и ключ 18 замкнут, выход триггера 11 имеет запретный уро вень О. В начале интервала интегрирования тактовый генератор 19 замыкае ключи 3 и 5 и размыкает ключ 18. Вхо ные нагфяжения делимого 17, (t ) и делителя UgCt) поданы на вхсиы 1 и 2 соответ ственно. Начинается интервал интегрирования Tj. В течение интервала Т. первым интегратором 6 интегрируют напряжение делимого и I {t) за время Т в соответствии с выражением: (i,(t)dt (, где Ц( t ) - ТОК заряда первого тегратора; -среднее значение то ка заряда первого интегратора; -входной масштабный резистор первого интегратора. Заряд первого интегратора в конце интервала интегрирования Tj Q V .7 UHT I - 1I В то же время Т, интегрируют напряжение делителя Ь ( t ) с помощью второго интегратора 15 в соответствии с выражением;R,6H,(i)dt-R, , где i(t), ток заряда второго интегратора;среднее значение тока заряда второго интегратора;входной масштабный резистор второго интегратора. В конце интервала интегрирования Т на выходе второго интегратора будет напряжениеиит и f) где C,-j - емкость интегрирующего конденсатора второго интегратора. За интервал Т на выходах интеграторов 6 и 15 будут напряжения инту (t) nl/HH jjCtJ. В момент t t, , т. е. в конце интегрирования, тактовый генератор 19 подает импульс сброса на вход индикатс ного блока 14, разомкнет ключи 3 и 5 и подает на вход триггера 11 сигнал цикла компенсации. На выходе триггера 11 появляется разрешающий уровень , который замыкает ключ 4 на втором входе первого интегратора 6. Импульсы 1/г ( i.) генератора 13 стабильной частоты через элемент И поступают в индикаторный блок 14. Компенсацию заряда первого интегратора 6 производят выходным напряжением1Г1,,5( t,) UMHT п второго интегратора конца интервала компенсации Т . Ток компенсации - Ц г Т Заряд компенсации q-r т J. в конце интервала компенсации выходное напряжение первого интегратора инт Т (t) О.Из равенства зарядовQ Q согласно выражениям (1) и (2) интервал компенсации

3tg-nt a . - .

К

L

иг R,

где K, Rg - коэффициент пропорциональности, и, - среднее значение ка

пряжения целимого; Vi среднее значение напряжения-целителя.

В конце интервала компенсации (при UuHirCtj) О) срабатьтает компаратор 10, который переводит триггер 11 в начальное состояние. На выходе триггера вырабатьюается сигнал логического нуля, который поступает на вход элемента И и закрьшает его. Сигнал с выхода триггера 11 поступает на вход ключа 4 и размыкает его, а также поступает на вход тактового генератора 19. Сигнал с выхода тактового генератора 19 замыкает ключ 18 и возвращает второй интегратор в начальное состояние.

В течение датервала компенсации измеряют время компенсации Т , заполняя его импульсами постоянной частоты I7f-(t ). Время компенсации TJ пропорциональное отношению напряжений , не зависит от длительности интервала интегрирования. Обеспечена возможность деления двух изменяющихся напряжений, усредняя их значения в течение, интервала интегрирования.

С целью получения аналогового выхода на выход интервала 20 включают усредняющее измерительное устройство,

Формула изобретения

Делительное устройство, содержащее первый ключ, первый вход которого является BxoaoNf делимого устройства, второй ключ, первый вход которого является входом делителя устройства, первый интегратор, первый вход которого подключен к выходу первого ключа, компаратор, один вход которого подключен к выходу интегратора, а другой вход - к шине нулевого потенциала, триггер, вход которого подключен к вькоау компаратора, элемент И, первый вхоа которого подключен к выходу триггера, генератор импульсов стандартной частоты, выход которого подключен ко второму входу элемента И, выход которого подключен ко входу цифрового инЩ1каторного блока генератор тактовых ИМПУЛЬСОВ, выходы которого подключены к управляющим входам всех ключей, элемента И и цифрового индикаторного блока, о т л и ч а ющ е е с я тем, что, с целью повышения точности деления, путем исключения зависимости В.ЫХОДНОГО сигнала от интервала 1штегрирования, оно содержит второй интегратор, в обратную связь которого включен ключ сброса, вход которого подключен к выходу третьего ключа, третий ключ, первый вход которого подключен к выходу второго интегратора, а выход ко второму входу первого интегратора.

Источники информации, пр1щятые во внимание при экспертизе

1.Прянишников В. А. Интегрирующие цифровые вольтметры постоянного тока, Л.: Энергия, 1976, с. 46-49.

2.Жук Л. А., Лучук А. М. , Скуридин В, П. Применение метода поочередного интегрирования сигналов цля построения множительно-целительных устройств комбин1фованного типа. Приборостроение, т. ХТ, № 9, 1968, с. 53-54, рис.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1979 |

|

SU805342A1 |

| Дифференцирующее устройство | 1979 |

|

SU817729A1 |

| Интегрирующий преобразователь напряжения в интервал времени | 1982 |

|

SU1046930A2 |

| Аналого-цифровой преобразователь | 1979 |

|

SU836794A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Способ измерения относительной разности амплитуд двух гармонических напряжений | 1988 |

|

SU1732287A1 |

| Интегрирующий аналого-цифровой преобразователь | 2023 |

|

RU2802872C1 |

| Преобразователь напряжения в интервал времени | 1985 |

|

SU1285599A1 |

| Устройство для диагностирования двигателя внутреннего сгорания | 1979 |

|

SU862025A1 |

Авторы

Даты

1980-07-23—Публикация

1978-06-26—Подача