(54) ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1978 |

|

SU750505A1 |

| Способ измерения относительной разности амплитуд двух гармонических напряжений | 1988 |

|

SU1732287A1 |

| ПЕРЕНОСНОЙ ЦИФРОВОЙ ИЗМЕРИТЕЛЬ БОЛЬШИХ ПОСТОЯННЫХ ТОКОВ | 1996 |

|

RU2131128C1 |

| Дифференцирующее устройство | 1979 |

|

SU817729A1 |

| Преобразователь напряжения в интервал времени | 1985 |

|

SU1285599A1 |

| Делительное устройство | 1980 |

|

SU875399A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| ЦИФРОВОЙ ПИРОМЕТР СПЕКТРАЛЬНОГО ОТНОШЕНИЯ | 1996 |

|

RU2108554C1 |

| Аналого-цифровой интегратор | 1979 |

|

SU842868A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПАРАМЕТРОВ ПОДКЛЮЧАЕМЫХ НА ПАРАЛЛЕЛЬНУЮ РАБОТУ ГЕНЕРАТОРОВ | 2014 |

|

RU2557672C1 |

t

Изобретение относится к аналогоцифровой вычислительной технике и технике ана.пого-цифрового преобразования.

Известно устройство для деления сигналов, содержащее два ключа, интегратор, триггер, генератор интервала времени, компаратор, элемент И, генератор импульсов стандартной частоты, цифровой индикаторный блок и генератор тактовых импульсов II .

Недостатком этого устройства является низкая точность деления. Зависимость выходного сигнала от длительности интервала интегрирования устраняется за счет введения генератора интервала времени, что вызывает дополнительные аппаратурные затрты.

Наиболее близким к предлагаемому по техническому реикжию является делительное устройство, соде{ж«йдое первый ключ, первый вход которого является входсял делимого устройства второй ключ, первый вход которого является входом делителя устройства, первый интегратор, первый вход которого покдлючен к выходу первого ключа, компаратор, один вход которого подключен к выходу интегратора, а другой вход - к шине нулевого потенциала, триггер, один вход которого подключен к выходу компаратора, элемент И, первый вход которого подключен к выходу триггера, генератор импульсов стандартной частоты, выход которого подключен ко второму входу элемента И, выход которого подключен

0 к первому входу цифрового индикаторного блока, второй интегратор, в цепь обратной связи которого вклочек к/аоч сброса, вход второго нитеграiTopa подключен к выходу второго клю5ча, третий ключ, выход которого подключен ко второму входу первого интегратора, генератор тактовых нмпульсов, выходы которого подключены к управляющим входам всех клйзчеК,

0 элемента И и цифрового индикаторного блока Гз. ,,

Недостатком данного устройства является то, что с помощью его возможно деление сигналов только опреде5ленной полярности, так как ток интегрирования и компенсации должны быть разного направления.

Цель изобретени; - расширение диапазона изменения входных сигналов

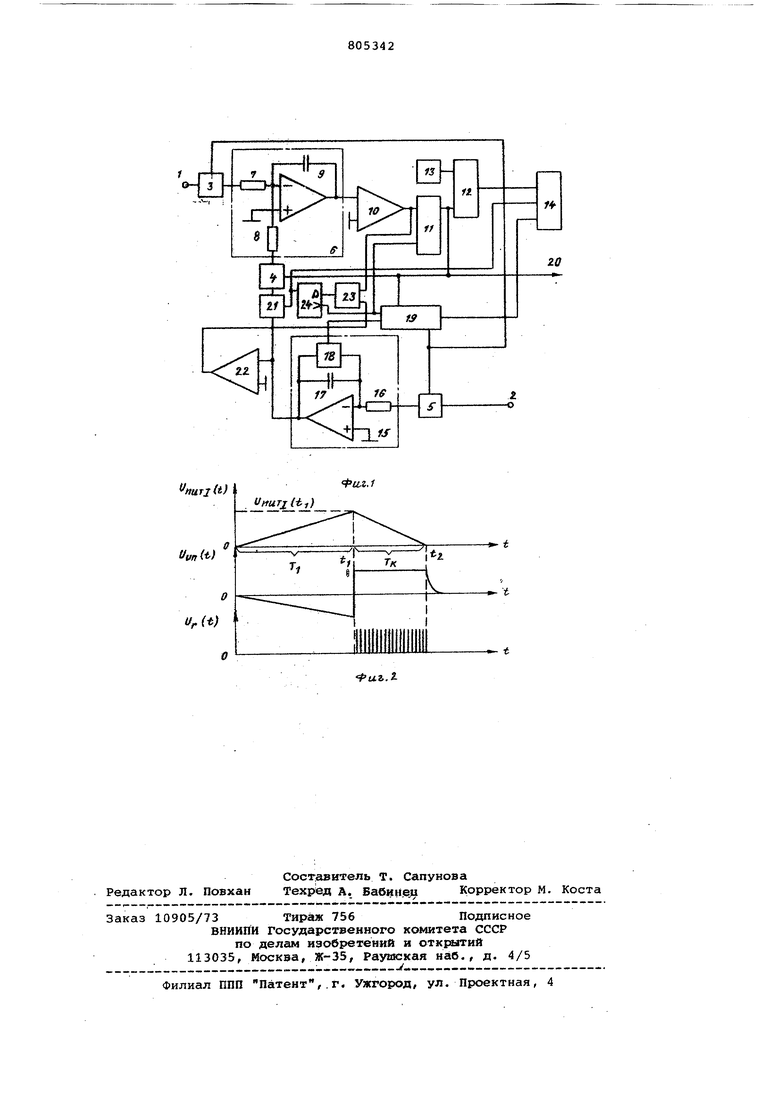

0 за счет выполнения операции деления независимо от полярности входных си налов. Цель достигается тем, что в извес ное устройство яополйнтельно В1ига чеда инвертор/ nepsi вход «соторого подключен к выкоду второго иатеграуора а выход - ко входу 7ретье1Ч} вторс компаратор, первьй ход «О5горого 1юдключен к вшсоду ин тегратора, второй - к вуяевого нотенпиала, де1Ш1фр1Ьтор, перв1яй н гто рой входам которого осщклвочеиы к выхо дам первого и второго компакторов соответственно, D-триггер, одни вход которого к выходу десшфрат1 а, другой о к выходу генератора тактовьас юяпульсов, а выход - ко вто рому вхоау цифрового индикаторного блока и ко второму входу инвертора. На фиг. 1 представлено делвтельж устройство, блок-схема; яа фиг.2 то же, диагра о«а работы. Устройство содержит вход аапряжеимя - делгалэго 1, вуод напряокения делителя 2, кхвочи 3, 4 и S, интвгра1чэр 6 с входными масжгтаваьаии р«Э1{Ьторами 7 и 8 и интегрирукш м коп ФемсАтором 9, первь комифатчзр 1в, т| ЕРгер 11, элемент И 12, rfeneратор 13 импульсов стандартной частоты, идафррвов индикаторшШ блок 14, второй кятегратор 15 с входишь маежтабшам резистором 16, интегрирую конденсатором 17 и ключом 18 сброса, генератор 19 тактовых имаульвов,вшссэд 20 интервала, инвертор 21, вторскв KOMiapaTop 22, дешифраtop 23, О-тригх р 24. Устройство paekjTaeT следующим образом. 8 печальном о&гу&яыян выходные на пряжение иигеграф| юв 6 и 15 равны нулю (е«ит1((в VtiKol -0). Ключи 3, 4 и 5 рвэо 1жнут&1, а 18 эамкяу7, выход грагг« 11 soieeT запретный уровень О В Ш1%а1Лв интервала ннтегф4сров«ния гевератс 19 тактовых зелвак&вт кяячи 3 и 5 и размыкает «jam 18. Вхрдиые напряжени делимого Uj,{t} и дагштвля U,2(t) подашь на входа 1 и 2 соответственно. Вачииаек-ся интервал интегрирования Т, . В течение инте| «яа t, первйм интегратором б интепяфуют напрасжеHvta делшюго 11 (t) ва время Т в соответствии с выражешкт:; ft7f I(t) J,,-, о R7 - входной масшта $ш|й реаяст н первого y.j ивтегрАторв; : - «ж заряда neiHloro интегратор ; 3 - среднее эяавенне токл aajpn t первог иятеграторА. Заряд первого интегратора независимо от поляриости напряжения делифе ля в конце интервала интегрирования равен VT . Т-«- О В го же время Т интегрируют напряжение Делителя с помощью второго интегратора 15 в соответствии с выражением t, R165i f,j(t)dt - RU-ajL- Т гдео R16 - входной масштабный резистор второго интегратора; - ток заряда второго интегратора; 3 - среднее значение тока заряда второго интегратора. В конце интервала интегрирования Т на выходе второго интегратора будет напряжение 3. где с I7 - емкость интегрирующего кон, денсатора второго интегратора. За интервал Т на выходах интеграторов 6 и 15 будут напряжения UMHT н U ц . в то же время на ыисодах компараторов 10 и 22 появляются потенциалы соответствующие полярностям выходных напряжений интеграторов 5 и 15. в зависимости от комбинаций Полярностей выходных напряжений интеграторов 6 и 15, т.е. соответствуюешх выходных потенциалов компараторов 10 и 22, на выходе деишфратора 23 появляется сигнал повторения или инверсии напряжения компенсации с срответствукщнм логический уровнем. КоэффнЕшент передачи инвертора 21 -1 соответствует иапряжениям делителя и делимого разной полярности и знаку минус частного. Коэффициент +i - напряжениям делителя и делимого одной поляриости к знаку птаос частного. В момент t-t-,, . в конце «втегрировання, генератор тактовых импульсов 19 подает импульс сброса на вход индикаторного блока 14, размыкает ключи 3 и 5 и подает на входы т|жггеров 11 и 24 сигнал иачги1а цикла компенсации. На выходе D-триггера 24 появляется урОве1«, соответствующий либо сигиалу повторения, либо сигналу инверсии инвертора 21. На выходе триггера 16 появляется разреиеавций уровень 1, кото1хлй замыкает кАоч 4 иа втором вхоДе первого интех ратора 6. Импульсы U (t) генератора стандартной частоты 13 через элемент И 12 поступают в нндикаторный блок 14. компенсация заряда первого интегратора 6 производят выходным напряжением Uvm {UMHT и I инверторповторителя 21 до конца интервала компенсации т..

Ток компенсации 3 .

м

R8 ardT-RB « где ft8 - входной масштабный резистор

первого интегратора. Заряд компенсации . v, «...1 --Ла.т. . 2)

С I / ftt

в конце интервала компенсации выходное напряжение первого интеГ1 ато{ а v.HTT(t,i) - 0.

Из равенства зарядов 9мнт к согласно выражениям (1) и (2) интвр вал компенсации

1Щ( R16 ря

sjh.

с17 TuiTRT

где и - среднее энАчеяие

напряжения делимого;

u - среднее знАчекие напряжения делителя,

К.|.с,7.

R8 коэффициент про порциойальйооти. в конце интервала компенсаиин (при UVIHTI срабатывает компаратор 10, KOtopuft переводит триггер 11 а начальное состояние Не выходе триггера 11 вырабатмвавтоя синал логического нуля, «отррьй поступает на эход элемента И 12 и зак(Ж1вает его. Сигнал с выхода триггера 11 поступает на вход кпючй 4 н pai3 edкает его, а также поступает, н вход генератора тактовых иипульеоВ| за квлкает ключ 18 и возвращает второй интегратор 15 в начальное состояние. Длительность интервала компенсации T измеряют, заполняя его иш1УЛ1 сШ4И постоянной частоты Of(t). Время компенсагши Тц, пропорционально отношению абсрльэтных значений ная| 1жеlUi

не зависят от ял«твяь

ний

ТСГВ

ности 1 нтервала интегрирования

Предлагаемое устройство обеспечивает деление двух изменя«:1ш хся дауполярных напряжений усреднеинем нх значения в течение интервала интегрирования и индикацию знака результата деления.

Формула изобретения

Делительное устройство, содержащее первый первь вкод которого является входом делимого уетройства, второй ключ, первый вход которого яаляфтея входом делителя устройства, первый интегратор, перв1яй вход которого подключен X выходу первого хгаоча, компаратор, один входкоторого подкл10чен к выходу интегратора, а ДРУГОЙ - к шине иулевого потенциала, триггер, вход которого подключен к выходу компаратора, Элемент И, перяый вход которого подключен к выходу триггера, генератор

o импулъоо стандартной частоты, вьосод которого подк,точвн ко второму входу элемента И, выход которого подключен к первому входу цифрового нндикаторного блока, второй интегратор, в

S цепь обратной связи которого включен ключ сброса, вход второго интеграто|ра подключен к выходу второго ключа, третий ключ, выход которого подключен ко второму входу первого интегратора,

0 генератор тактовых импульсов, которого геэдключены к управляющим входам всех ключей, элемента И и цифрового индикаторного блока, отличающееся тем, что, с целью расширения диапазона изменения входНШ{ .сигналов за счет выполнения операции деления независимо от поляр- ности входных сигналов,оно содержит инвертор, первый вход которого подк/шчен к выходу второго интегратора,

Q а выход - ко входу третьего ключа, второй компаратор, первый вход которого подключен к выходу второго интегратора, второй - к ишне нулевого потенциала, дешифратор, первый и вто5рой входы которого подключены к выходам первого и второго компараторовсоответственно, D-триггер, один вход KOTCfporo подключен к выходу дешифратора, другой -. к выходу генератора тактовых.импульсов, а выход подключен ко второму входу цифрового нндикаторного блока и ко второму входу, инвертора .

Источники информации, принятые во внимание при экспертизе

S

0 1968, т. Х1, 9, с.53-54, рис. 1.

ниг2М

UftUT2()

(imM

Ur(t)

Авторы

Даты

1981-02-15—Публикация

1979-03-11—Подача