рез четвертый элемент НЕ с вторым информационным входом второго мультиплексора, а второй информационный вход третьего мультиплексора подключен к выходу первого компаратора, выход первого триггера соединен с первым информационным входом

первого мультиплексора, второй информационный вход которого подключен к выходу второго триггера, выходы третьего и четвертого элементов И соединены соответственно с синхровходами второго и первого . триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1418768A1 |

| Цифровой измеритель девиациии сопротивления | 1973 |

|

SU477365A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1985 |

|

SU1304014A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1525915A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

гаВРИДНОЕ ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО, содержащее первый и второй интеграторы, выход каждого из которых подключен к первым входам соответственно первого и второго компараторов, выход первого компаратора соединен с входом данных первого триггера, переключатель, первый выход которого соединен с входом первого интегратора, и масштабный резистор, первый вывод которого является информационным входом устройства, отличающееся тем, что, с целью повышения точности интегрирования, в него введены генератор эталонных токов, счетчик, три мультиплексора, четыре элемента НЕ, второй триггер, четьфе элемента И, причем выходы первого и второго элементов И являются информационными вькодами устройства, вторые входы первого и второго компараторов соединены с шиной нулевого потенциала, второй вывод масштабирующего резистора подключен к информа1и онному входу переключателя, второй выход которого соединен с входом второго интегратора, знаковь1Й .вход генератора эталонных токов подключен к выходу первого мультиплексора, соединенного с управляющим входом второго мультиплексора, первым входом первого элемента И и через первый элемент НЕ с первым входом второго элемента И, вькод второго мультиплексора подключен к первому управляющему входу генератора эталонных токов и через второй элемент НЕ к (Л вторым входам первого и второго элементов И, третьи входы которых соединены с входом тактовых импульсов устройства, подключенным к входу счетчика, выход которого соединен с управляющим входом переключателя, вторым управляющим входом генератора эталонных токов, первым входом третьего элемента И и через третий элемент НЕ с первым входом четвертого элемента И и с управляющими входами первого и третьего мультиплексоров, вторые входы третьего и четвертого элементов И подклгоче. ны к входу тактовых импульсов устройства, первый и второй выходы генератора эталонных токов соединены с входами соответственно первого и второго интеграторов, выход второго компаратора подключен к входу данных второго триггера и первому информационному входу третьего муль|типлексора, выход которого соединен с первым информационным входом и че

Изобретение относится к гибридной вычислительной технике и может быть использовано в аналого-цифровых вычислительных системах и устройствах автоматики для длительного интегрирования аналогового сигнала.

Цель изобретения - повышение точности интегрирования.

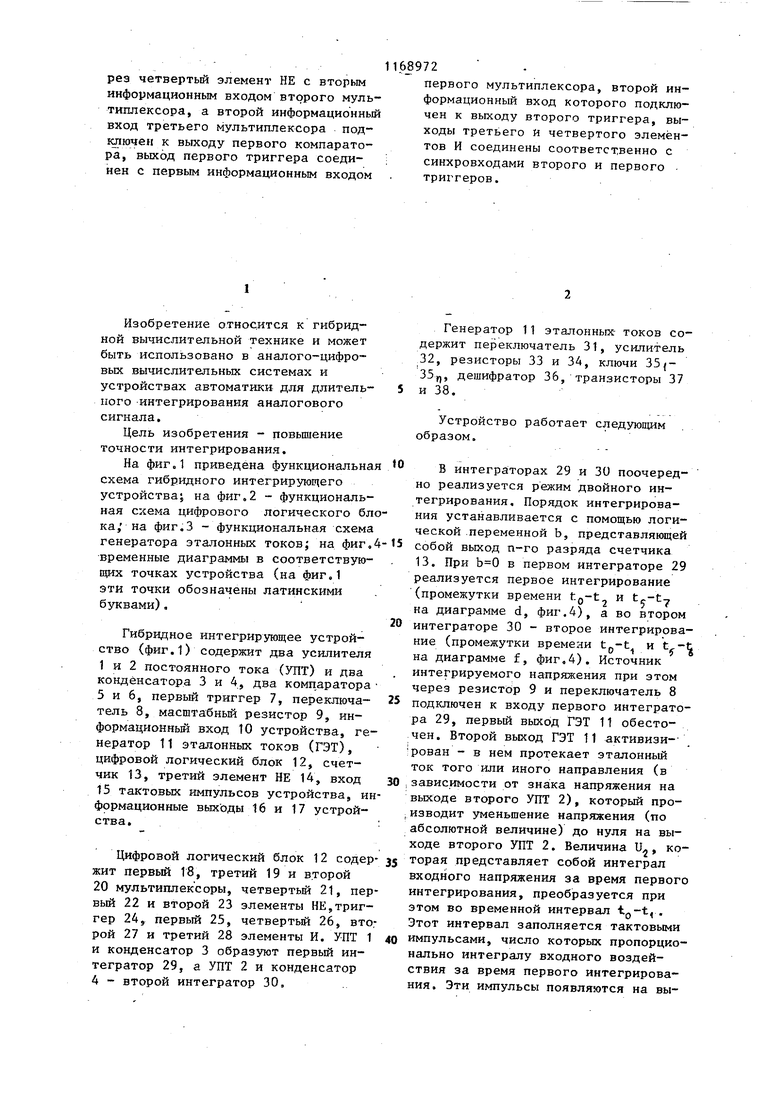

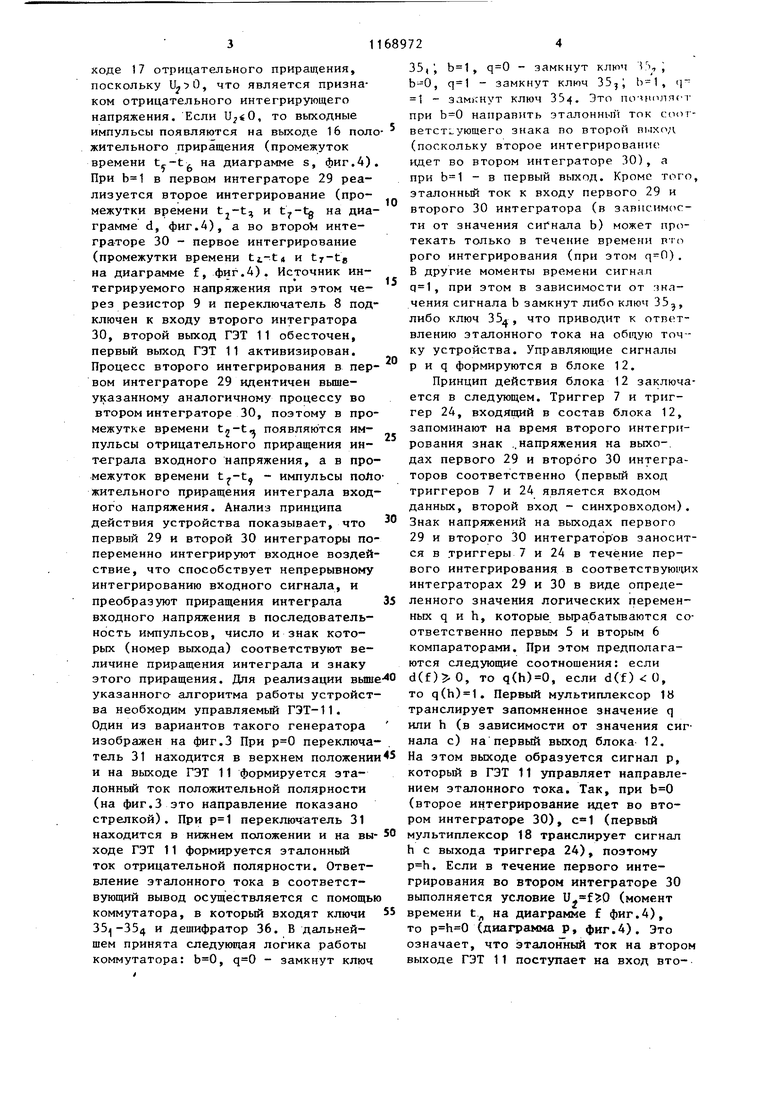

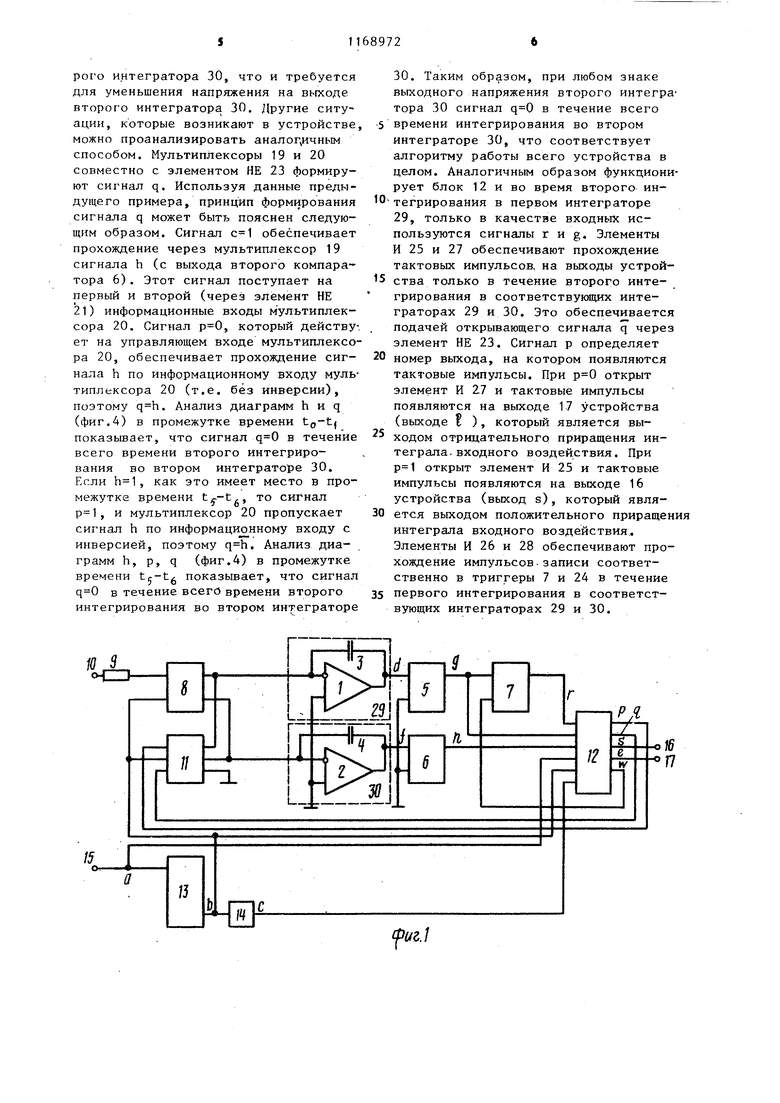

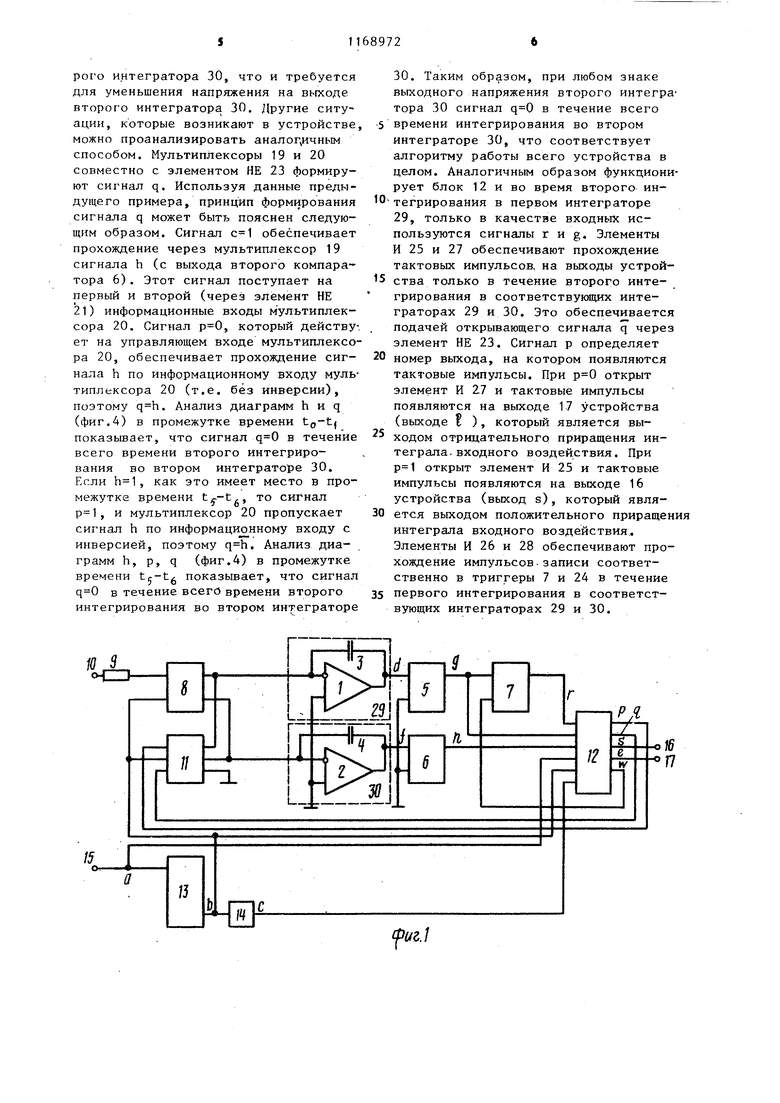

На фиг.1 приведена функциональная схема гибридного интегрирующего устройства на фиг.2 - функциональная схема цифрового логического блока; на фиг.З - функциональная схема генератора эталонных токов; на фиг,4временные диаграммы в соответствующих точках устройства (на фиг.1 эти точки обозначены латинскими буквами),

Гибридное интегрирующее устройство (фиг.1) содержит два усилителя

1 и 2 постоянного тока (ТОТ) и два конденсатора 3 и 4, два комцаратора 5 и 6, первый триггер 7, переключатель 8, масштабньй резистор 9, информационньй вход 10 устройства, генератор t1 эталонных токов (ГЭТ), цифровой логический блок 12, счетчик 13, третий элемент НЕ 14, вход 15 тактовых импульсов устройства, информационные выходы 16 и 17 устройства.

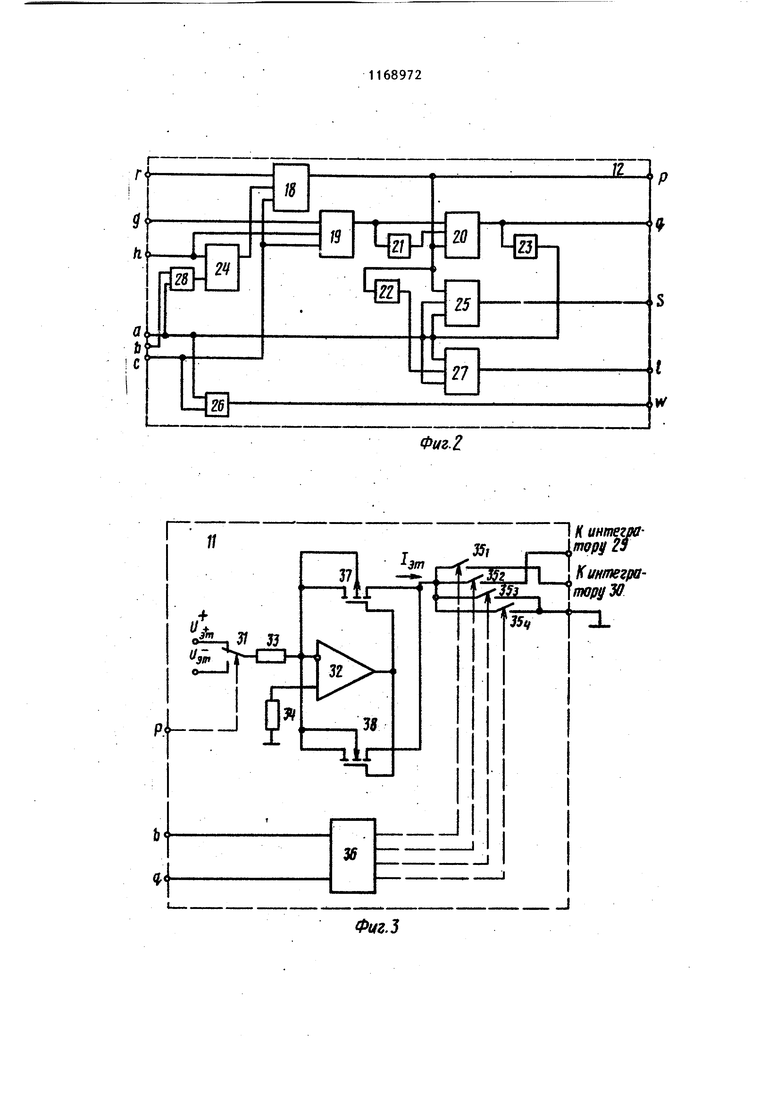

Цифровой логический блок 12 содержит первьй 18, третий 19 и второй 20 мультиплексоры, четвертьй 21, первый 22 и второй 23 элементы НЕ,триггер 24, первый 25, четвертьй 26, вто,рой 27 и третий 28 элементы И. УПТ 1 и конденсатор 3 образуют первый интегратор 29, а УПТ 2 и конденсатор 4 - второй интегратор 30.

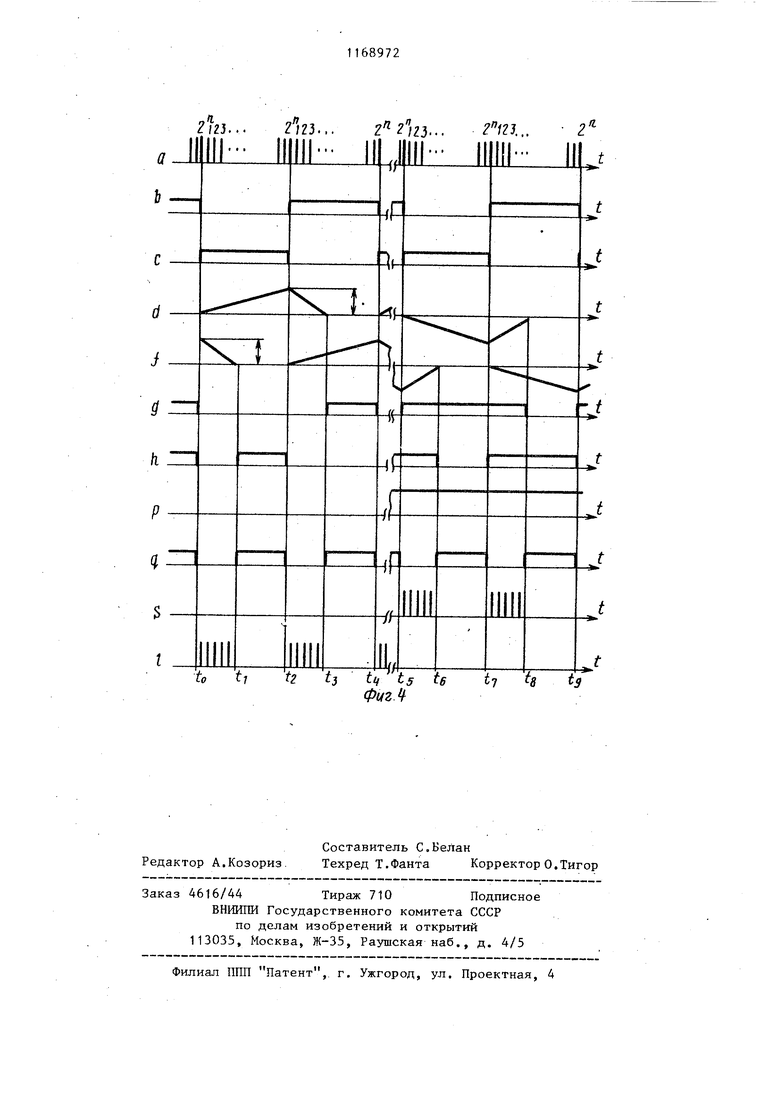

Генератор 11 эталонных- токов содержит переключатель 31, усилитель 32, резисторы 33 и 34, ключи 35{35, дешифратор 36, транзисторы 37 и 38.

Устройство работает следующим образом.

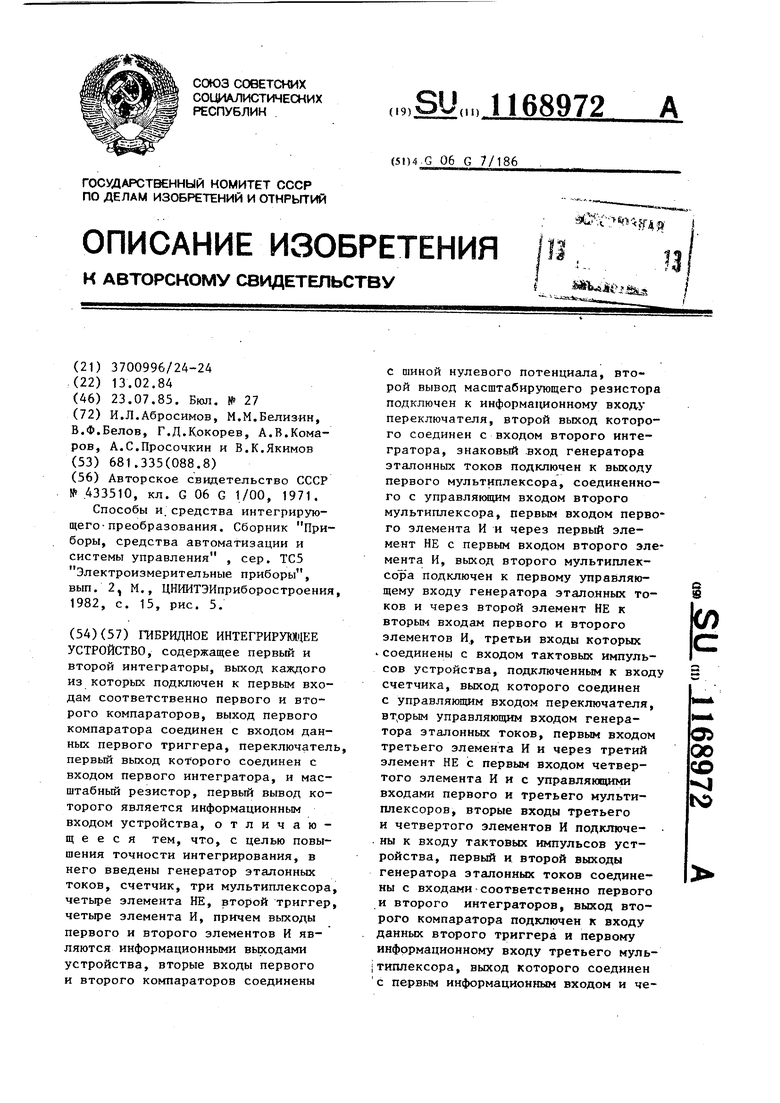

В интеграторах 29 и 30 поочередно реализуется режим двойного интегрирования. Порядок интегрирования устанавливается с помощью логической .переменной Ь, представляющей

собой выход п-го разряда счетчика 13. При в первом интеграторе 29 реализуется первое интегрирование (промежутки времени f-Q-t. и на диаграмме d, фиг.4), а во втором

интеграторе 30 - второе интегрирование (промежутки времени tp-t и t,-t на диаграмме f, фиг.4). Источник интегрируемого напряжения при этом через резистор 9 и переключатель 8

подключен к входу первого интегратора 29, первый выход ГЭТ 11 обесточен. Второй выход ГЭТ 11 активизи- рован - в нем протекает эталонный ток того или иного направления (в

30 , завис.имости от знака напряжения на выходе второго УПТ 2), который про;изводит уменьшение напряжения (по абсолютной величине) до нуля на выходе второго УПТ 2. Величина U, которая представляет собой интеграл входного напряжения за время первого интегрирования, преобразуется при этом во временной интервал tg-t,. Этот интервал заполняется тактовыми

40 импульсами, число которых пропорционально интегралу входного воздействия за время первого интегрирования. Эти импульсы появляются на выходе 17 отрицательного приращения, поскольку , что является признаком отрицательного интегрирующего напряжения. Если , то выходные импульсы появляются на выходе 16 пол жительного приращения (промежуток времени t,-t на диаграмме s, фиг.4) При в первом интеграторе 29 реализуется второе интегрирование (промежутки времени tj-t: и на диа грамме d, фиг.4), а во второй интеграторе 30 - первое интегрирование (промежутки времени ti-t4 и tf-tg на диаграмме f, фиг.Д). Источник интегрируемого напряжения при этом через резистор 9 и переключатель 8 под ключен к входу второго интегратора 30, второй выход ГЭТ 11 обесточен, первый выход ГЭТ 11 активизирован. Процесс второго интегрирования в пер вом интеграторе 29 идентичен вышеуказанному аналогичному процессу во втором интеграторе 30, поэтому в про межутке времени tj-t- появляются импульсы отрицательного приращения интеграла входного напряжения, а в про межуток времени , - импульсы пол жительного приращения интеграла вход ного напряжения. Анализ принципа действия устройства показывает, что первый 29 и второй 30 интеграторы по переменно интегрируют входное воздей ствие, что способствует непрерывному интегрированию входного сигнала, и преобразуют приращения интеграла входного напряжения в последовательность импульсов, число и знак которых (номер выхода) соответствуют величине приращения интеграла и знаку этого приращения. Дпя реализации выш указанного- алгоритма работы устройства необходим управляемый ГЭТ-11. Один из вариантов такого генератора изображен на фиг.З При переключатель 31 находится в верхнем положении и на выходе ГЭТ 11 формируется эталонный ток положительной полярности (на фиг.З это направление показано стрелкой). При переключатель 31 находится в нижнем положении и на выходе ГЭТ 11 формируется эталонный ток отрицательной полярности. Ответвление эталонного тока в соответствующий вывод осуществляется с помощью коммутатора, в который входят ключи 35 1-354 дешифратор 36. В дальнейщем принята следующая логика работы коммутатора: , - замкнут ключ 35, , , - замкнут ключ Г% , Ь-0, - замкнут ключ , 4 1 - замкнут ключ 354- Это почниляс i при направить эталонный ток соотвeтcтLyющeгo знака по второй пыход (поскольку второе интегрированиеидет во втором интеграторе 30), а при - в первый выход. Кроме того, эталонный ток к входу первого 29 и второго 30 интегратора (в зависимости от значения сигнала Ь) может протекать только в течение времени рого интегрирования (при этом ), В другие моменты времени сигнал , при этом в зависимости от значения сигнала b замкнут либо ключ 35, либо ключ 35, что приводит к ответвлению эталонного тока на общую точку устройства. Управляющие сигналы р и q формируются в блоке 12. Принцип действия блока 12 заключается в следующем. Триггер 7 и триггер 24, входящий в состав блока 12, запоминают на время второго интегрирования знак ..напряжения на выхо-. дах первого 29 и второго 30 интеграторов соответственно (первый вход триггеров 7 и 24 является входом данных, второй вход - синхровходом). Знак напряжений на выходах первого 29 и второго 30 интеграторов заносится в .триггеры 7 и 24 в течение первого интегрирования в соответствующих интеграторах 29 и 30 в виде определенного значения логических переменных q и h, которые вьграбатьгоаются соответственно первым 5 и вторым 6 компараторами. При этом предполагаются следующие соотношения: если d(f)5.0, то q(h)0, если d(f) : О, то q(h)1. Первый мультиплексор 18 транслирует запомненное значение q или h (в зависимости от значения сигнала с) на первый выход блока 12. На этом выходе образуется сигнал р, который в ГЭТ 11 управляет направлением эталонного тока. Так, при (второе интегрирование идет во втором интеграторе 30), (первый мультиплексор 18 транслирует сигнал h с выхода триггера 24), поэтому . Если в течение первого интегрирования во втором интеграторе 30 выполняется условие (момент времени t на диаграмме f фиг.4), то (диаграмма j, фиг.4). Это означает, что :эталонный ток на втором выходе ГЭТ 11 поступает на вход второго интегратора 30, что и требуется для уменьшения напряжения на выходе второго интегратора 30. Другие ситуации, которые возникают в устройстве можно проанализировать аналог,ичным способом. Мультиплексоры 19 и 20 совместно с элементом НЕ 23 формируют сигнал q. Используя данные предыдущего примера, принцип формирования сигнала q может быть пояснен следующим образом. Сигнал обеспечивает прохождение через мультиплексор 19 сигнала h (с выхода второго компара- тора 6). Этот сигнал поступает на первый и второй (через элемент НЕ 21) информационные входы мультиплексора 20. Сигнал , который действу ет на управляющем входе мультиплексора 20, обеспечивает прохождение сигнала h по информационному входу мультиплексора 20 (т.е. без инверсии), поэтому . Анализ диаграмм h и q (фиг.4) в промежутке времени показьшает, что сигнал в течение всего времени второго интегрирования во втором интеграторе 30. Если , как это имеет место в промежутке времени , то сигнал , и мультиплексор 20 пропускает сигнал h по информационному входу с инверсией, поэтому . Анализ диаграмм h, р, q (фиг.4) в промежутке времени показывает, что сигнал в течение всего времени второго интегрирования во втором интеграторе

первого интегрирования в соответствующих интеграторах 29 и 30.

f-

g

W

n{

2

ai ft с

- 25

I

w

Фиг.1

KuHmezjfa mffpy 29

X -

Фиг.З

...

z1z3...

а

п

to ti t2 t) ts te

... ,., г

л

л

tj 4 t

Фиг Л

| ГИБРВДЮЕ ШТЕГРИРУОДЕЕ УСТРОЙСТВО | 1971 |

|

SU433510A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способы и.средства интегрирующего- преобразования | |||

| Сборник Приборы, средства автоматизации и системы управления , сер | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-13—Подача