(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

| Запоминающее устройство | 1977 |

|

SU733020A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| Запоминающее устройство | 1976 |

|

SU932567A1 |

| Запоминающее устройство | 1971 |

|

SU479151A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU942140A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

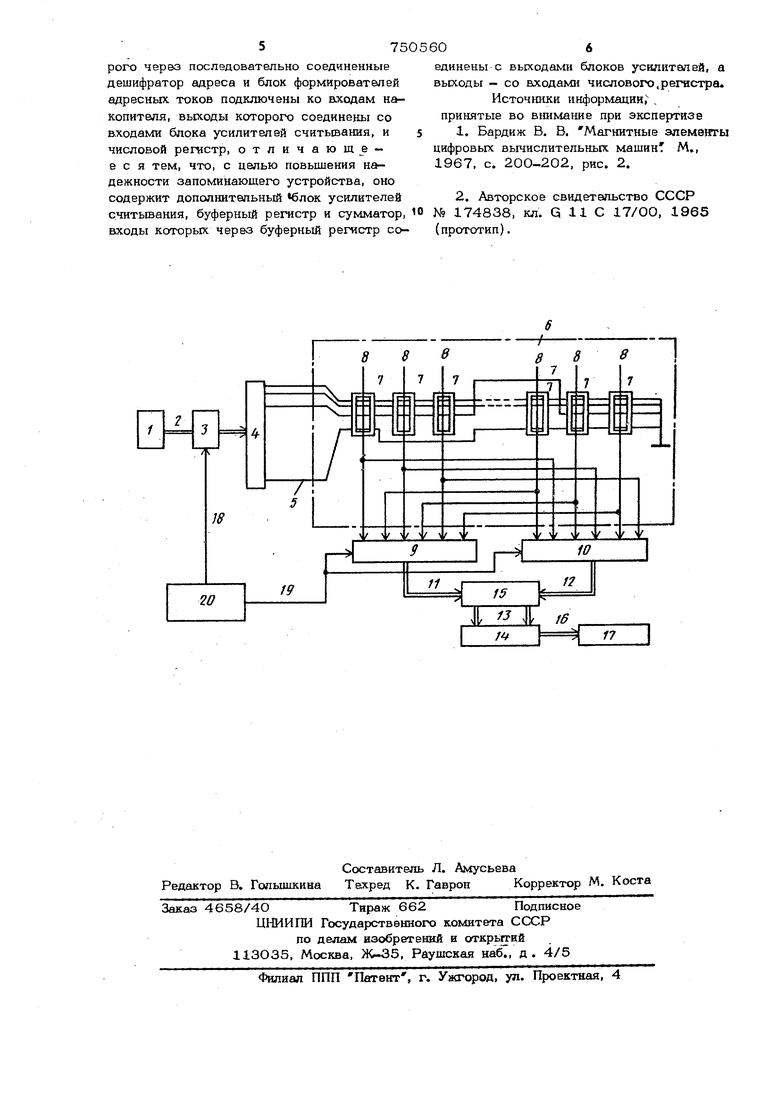

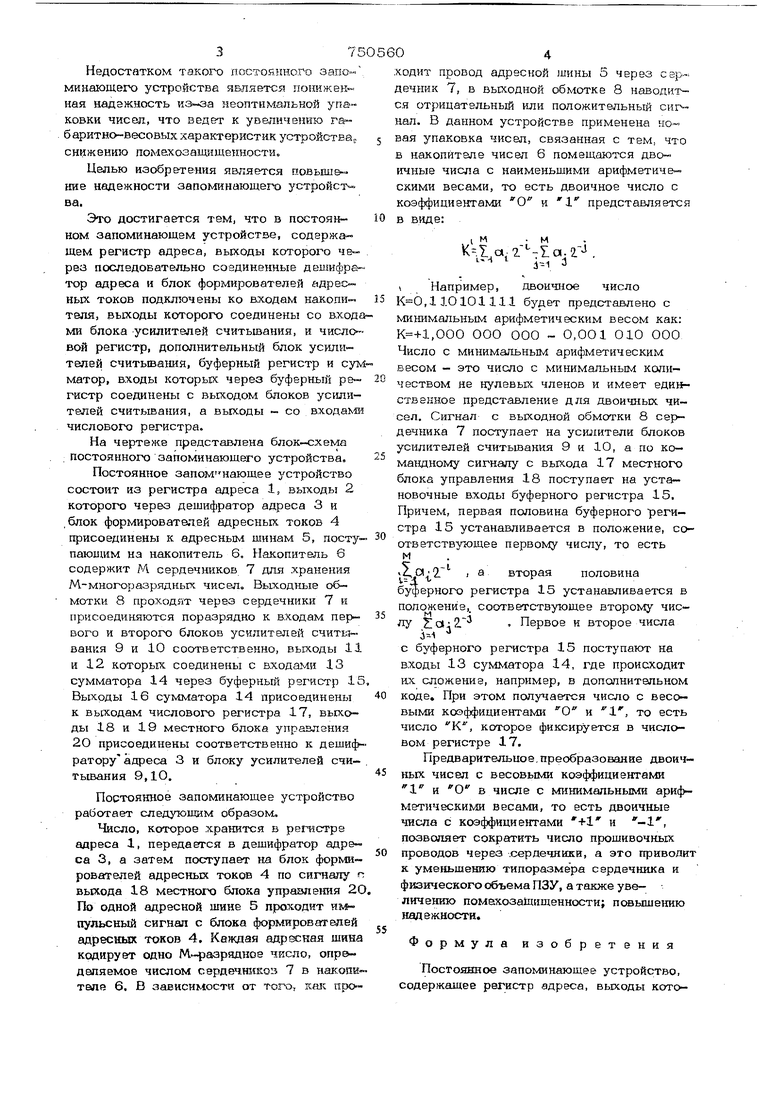

Изобретение относится к области вычислительной тахники и может использоваться в различных цифровьк вычислител ных системах. Известны постоянные запоминающие устройства, содержащие регистр адреса, дешифратор адреса, блок формирователей адресного тока, накопитель чисел, блок усилителей считьшания и регистр данных. Накопитель чисел состоит из М сердечников для хранения М-многоразряднык чисел. При прохождении тока по одной из адресных шин, наводятся сигналы в вьвходных шинах, проходящи;х через сердечники. Выходная шина служит для считьта ния кода единицы, если праходит через .сердечник, и - кода нуля О, если не проходит через него 1 . Недостатком такого постоянного запоминающего устройства (ПЗУ) является низкая помесхозалщщенность, вследствие трудностей, связанных с различием кул&вого и единичного уровней сигналов, и пониженная надежность из-за неоптимаяы НОЙ упаковки чисел, что приводит к увеличению габаритно-весовых .характеристик ПЗУ. Наиболее близким техническим решением к данному является постоянное запоминающее устройство, содержащее р&гистр адреса,выходы которого через последовательно соединенные дешифратор адреса и блок формирователей адресньсх токов подключены ко входам накопителя, выходы которого соединены со входами блока усилителей считывания, и числовой регистр 2 . Накопитель чисел состоит из М cej дачников для формирования М-разрядных чисел, но при этом адресные проводники проходят через все сердечиики, таким образом, что в выходных обмотках сердечников наводится отрицательный сигнал, что соответствует, например, считыванию кодовой единицы числа, или положительный сигнал, соответствующий нул&вой информации. Недостатком такого постоянного эапоминающего устройства являвтся пониженная надажность неоптимальной упаковки чисел, что ведет к увеличению га баритно-весовых характеристик устройотвас снижению помехозащищенности. Целью изобре гения является повышение надежности запоминающего устройства. Это достигается тем, что в постоянном запоминающем устройстве, содержащем регистр адреса, выходы которого че рез последовательно соединенные дешифратор адреса и блок формирователей адрес ных токов подключены ко входам накопителя, выходы которого соединены со вход ми блока усилителей считывания, и числовой регистр, дополнительный блок усилителей считьташя, буферный регистр и сум матор, входы которых через буферный регистр соединены с выходом блоков усилителей считывания, а выходы - со в. числового регистра. На чертеМСе представлена блок-схема постоянного запоминающего устройства, Постоянное запоминающее устройство состоит из регистра адреса 1, выходы 2 которого через дешифратор адреса 3 и ,блок формироватачей адресных токов 4 присоединены к адресным шинам 5, посту пающим на накопитель 6. Накопитель 6 содержит М сердечников 7 для хранения М-многоразрядных чисел. Выходные обмотки 8 проходят через сердечники 7 и присоединяются поразрядно к входам первого и второго блоков усилителей считывания 9 и 10 соответственно, выходы 11 и 12 которых соединены с входами 13 сумматора 14 через буферный регистр 15 Выходы 16 сумматора 14 присоединены к выходам числового регистра 17, выходы 18 и 19 местного блока управления 20 присоединены соответственно к дешиф ратору адреса 3 и блоку усилителей счигывания 9,10. Постоянное запоминающее устройство работает следующим образом, Число, которое .хранится в регистре адреса 1, передает-ся в дешифратор адре са 3, а затем поступает на блок формирователей адресных токов 4 по сигналу п вьрюда 18 местного блока управления 2 По одной адресной шине 5 проходит HiviH пульсный сигнал с блока формирователей адресных токов 4. Каждая адрэсная шина кодирует одно М -раарядное число, опр&депяемое числом сэрдечникоз 7 в накопИ талй 6, В зависимости от того, как одит провод адресной шины 5 через серечник 7, в выходной обмотке 8 наводитя отрицательный или положительный сигнал. В данном устройстве применена новая упаковка чисел, связанная с тем, что в накопителе чисел 6 помещаются дво ичные числа с наименьшими арифметическими весами, то есть двоичное число с О и представляется коэффициентами в виде: --la-rJ, л1.«. 3 V Например, двоичное число ,11О101111 будет представлено с минимальным арифметическим весом как: К-И,000 ООО 000 - 0,001 О10 ООО Число с минимальным арифметическим весом - это число с минимальным количеством не нулевьрс членов и имеет единственное представление для двоичных чисел. Сигнал с выходной обмотки 8 сердечника 7 поступает на усилители блоков усилителей считьюания 9 и 10, а по командному сигналу с выхода 17 местного блока управления 18 поступает на установочные входы буферного регистра 15. Причем, первая половина буферного регистра 15 устанавливается в положение, соответствующее первому числу, то есть «Z, , , а вторая половина буферного регистра 15 устанавливается в положение,, соответствующее второму числу 21 Первое и второе числа JM с буферного регистра 15 поступают на входы 13 сумматора 14, где происходит их сложение, например, в дополнительном коде. При этом получается число с весовыми коэффициентами О и i, то есть число К, которое фиксируется в числовом регистре 17. Предварительное,преобразование двоичных чисел с весовыми коэффициентами 1 и О в числе с минимальными арифметическими весами, то есть двоичные числа с коэффициентами и -1, позволяет сократить число прошивочных проводов через .сердечники, а это приводит к уменьшению типоразмера сердечника и физического объема ПЗУ, а также увеличешпо помехозаШищенности; повышению надежности. Формула изобре тения Постоянное запоминающее устройство, содержащее регистр адреса, выходы кото575рого через последовательно соединенные дешифратор адреса и блок формирователей адресных токов подключены ко аходам накопителя, вьгходы которого соединены со входами блока усилителей считывания, и числовой регистр, отличающееся тем, что, с целью повышения надежности запоминающего устройства, оно содержит дополнительный «блок усилителей считьюания, буферный регистр и сумматор, аходы которых через буферный регистр со8 в

8

8 8

I 06 единены с выходами блоков усилителей, а выходы - со входами числового,регистра. Источники информации,, принятые во внимание при экспертизе 1.Бардиж В. В. Магнитные элементы цифровых вьгаислительных машинТ М., 1967, с. 200-202, рис. 2. 2.Авторское свидетельство СССР № 174838, кл. G 11 С 17/00, 1965 (прототип).

Авторы

Даты

1980-07-23—Публикация

1977-11-03—Подача