Изобретение относится к вычислительной технике, а именно к двухмерным магнитным оперативным запоминающим устройствам. Известно двухмерное оперативное запоминающее устройство на ферритовых сердечниках, построенных по принципу совпадения токов, каждый сердечник магнитного накопителя прошит тремя проводами 1. Однако в данном устройстве невозможно обращение к следующей ячейке накопителя до окончания восстановления информации в предыдущей ячейке. Наиболее близким к изобретению по технической сущности является запоминающее устройство, содержащее основные регистры адреса и числа, одни из входов которых подключены к шине обращения, другие - соответственно к адресной и числовой шинам, выход основного регистра адреса соединен с одним из входов дешифратора адреса, выходы которого соединены с одними из входов блока формирователей адресного тока, другие входы которого подключены к одним из выходов блока управления, входы которого подключены к шинам считывания и обращения, выходы блока формирователей адресного тока соединены с одним из входов накопителя, другие входы которого подключены к выходам блока формирователей разрядного тока, а выходы - к входам блока усилителей считывания, выходы которых соединены с одними из входов регистра числа 2. Недостаток устройства заключается в том, что время обращения к нему в два раза больше времени выборки информации. Цель изобретения - повышение быстродействия запоминающего устройства. Поставленная цель достигается тем, что устройство содержит компаратор и дополнительные регистры числа и адреса, одни из входов которых соединены с другими выходами блока управления, другие входы дополнительных регистров числа и адреса соединены соответственно с выходами основных регистров числа и адреса, а выходы - соответственно с входами блока формирователей разрядного тока и соответствующими входами дешифратора адреса, соединенными с одними из входов компаратора, другие входы которого соединены с выходами основного регистра числа и адреса, а выход-

с соответствующим входом блока управлв ния.

Дешифратор адреса выполнен по схеме одновременной выборки двух адресных шин. Выходы основного регистра адреса связаны с информационными входами дополнительного регистра адреса и с одной группой вхс(дов схемы сравнения последовательных адресов. Другая группа входов схемы сравнения последовательных адресов связана с выходами дополнительного регистра адреса, а ее выход связан со входом блока управления. Выход блока управления связан с управляющими входами дополнительного регистра адреса и дополнительного регистра числа. Выходы дополнительного регистра адреса связаны с группой входов дешифратора адреса. Информационные входы дополнительного регистра числа связаны с выходами основного регистра числа. Выходы дополнительного регистра числа связаны с входами блока формирователей разрядного тока.

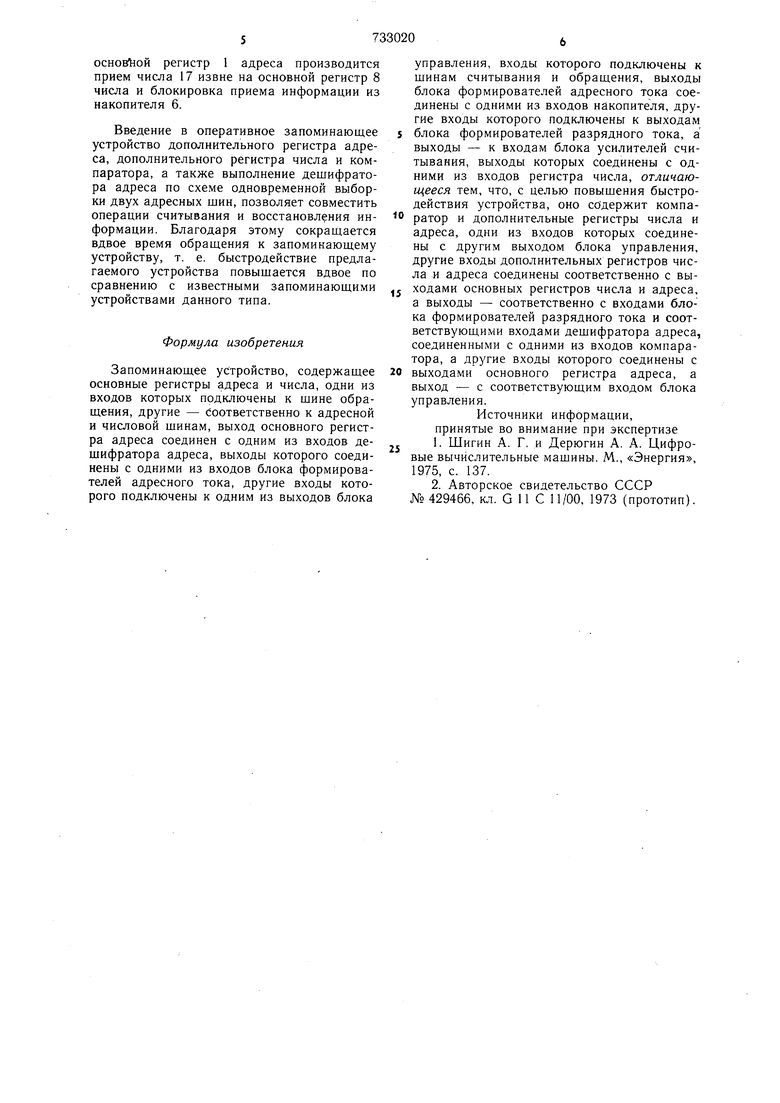

Блок-схема предлагаемого устройства представлена на чертеже.

Оперативное запоминающее устройство содержит основной регистр 1 адреса, дополнительный регистр 2 адреса, дешифратор 3 адреса, блок 4 формирователей адресного тока, блок 5 формирователей разрядного то,ка, накопитель 6, блок 7 усилителей считывания, основной регистр 8 числа, дополнительный регистр 9 числа, компаратор 10, блок 11 управления. Выходы основного регистра 1 адреса соединены с информационными входами дополнительного регистра 2 адреса, дешифратора 3 адреса и с одними из входов компаратора (схемы сравнения последовательных адресов) 10. Выходы дополнительного регистра 2 адреса связаны с другими входами дешифратора 3 адреса и с другими входами компаратора 10., Выходы дешифратора 3 адреса связаны с информационными входами блока 4 формирователей адресного тока. Управляющий вход блока 4 формирователей адресного тока соединен с выходом 15 блока 11 управления. Выход 14 блока 11 управления соединен с управляющими входами дополнительного регистра 2 адреса и дополнительного регистра 9 числа. Выходы блока 4 формирователей адресного тока связаны с адресными входами накопителя 6, разрядный входы которого соединены с выходами блока 5 формирователей разрядного тока. Выходы накопителя 6 соединены с входами блока 7 усилителей считывания, выходы которого соединены с входами основного регистра 8 числа. Выход основного регистра 8 числа соединен с информационными входами дополнительного регистра 9 числа, выходы которого соединены с входами блока 5 формирователей разрядного тока. Выход компаратора 10 соединен с входом блока 11 управления. Выход основного регистра S числа является

выходом оперативного запоминающего устройства.

Основной регистр 1 адреса предназначен для приема адреса в запоминающее устройство и управляет процессом считывания и стирания информации.

Дополнительный регистр 2 адреса предназначен для приема адреса из основного регистра 1 адреса и управляет процессом записи информации.

Дешифратор 3 адреса выполнен по схеме одновременной выборки двух адресных шин.

Основной регистр 8 числа предназначен для приема числа с выхода блока 7 усилителей считывания (при с итывании) и извне (при записи) и выдачи числа из запоминающего устройства.

Дополнительный регистр 9 числа предназначен для приема числа из основного регистра 8 числа и управления регенерацией числа в запоминающем устройстве.

Схема 10 сравнения последовательных адресов выявляет повторное обращение по одному и тому же адресу в запоминающее устройство и вырабатывает сигнал запрета

считывания.

Устройство работает следующим образом. При поступлении в запоминающее устройство сигнала «Обращение« 12 и кода 16 адреса происходит занесение адреса на осQ новной регистр 1 адреса. Адрес расшифровывается в дещифраторе 3 и через выбранную адресную шину при наличии в блоке 11 управления сигнала признака «Считывание 13 проходит импульс тока считывания, равный или более 1,5 IM(IM - ток полного

5 перемагничивания сердечника), который производит считывание информации из ки накопителя 6. Считанная информация, пройдя через блок 7 усилителей считывания, записывается на основной регистр 8 числа. После окончания импульса 12 происходит перепись импульсом 14 адреса из основного регистра 1 адреса в дополнительный регистр 2 адреса, считанной информации из основного регистра 8 числа в дополнительный регистр 9 числа и выдача

5 считанного числа из запоминающего устройства. По следующему сигналу 12 происходит занесение следующего адреса в основной регистр 1 адреса и также, как сказано выше, производится считывание информации из последующей ячейки накопителя 6 и запись ее

в основной регистр 8 числа, если компаратор 10 не выдает запрета на считывание следующего адреса. (Запрет на считывание выдается в случае последовательного обращения к одному и тому же адресу). Одновременно со считыванием информации из последующей ячейки производится восстановление информации в предыдущей ячейке. При поступлении сигнала признака «Запись 13 одновременно с приемом 16 адреса на

основной регистр 1 адреса производится прием числа 17 извне на основной регистр 8 числа и блокировка приема информации из накопителя 6.

Введение в оперативное запоминающее устройство дополнительного регистра адреса, дополнительного регистра числа и компаратора, а также выполнение дешифратора адреса по схеме одновременной выборки двух адресных шин, позволяет совместить операции считывания и восстановления информации. Благодаря этому сокращается вдвое время обращения к запоминающему устройству, т. е. быстродействие предлагаемого устройства повышается вдвое по сравнению с известными запоминающими устройствами данного типа.

Формула изобретения

Запоминающее устройство, содержащее основные регистры адреса и числа, одни из входов которых подключены к щине обращения, другие - соответственно к адресной и числовой шинам, выход основного регистра адреса соединен с одним из входов дешифратора адреса, выходы которого соединены с одними из входов блока формирователей адресного тока, другие входы которого подключены к одним из выходов блока

управления, входы которого подключены к шинам считывания и обращения, выходы блока формирователей адресного тока соединены с одними из входов накопителя, другие входы которого подключены к выходам блока формирователей разрядного тока, а выходы - к входам блока усилителей считывания, выходы которых соединены с одними из входов регистра числа, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит компаратор и дополнительные регистры числа и адреса, одни из входов которых соединены с другим выходом блока управления, другие входы дополнительных регистров числа и адреса соединены соответственно с выходами основных регистров числа и адреса, а выходы - соответственно с входами блока формирователей разрядного тока и соответствующими входами дешифратора адреса, соединенными с одними из входов компаратора, а другие входы которого соединены с

выходами основного регистра адреса, а выход - с соответствующим входом блока управления.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г. и Дерюгин А. А. Цифровые вычислительные машины. М., «Энергия, 1975, с. 137.

2. Авторское свидетельство СССР № 429466, к„1. G 11 С 11/00, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Запоминающее устройство | 1975 |

|

SU627539A1 |

| Запоминающее устройство | 1974 |

|

SU536524A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU942140A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Оперативное запоминающее устройство | 1975 |

|

SU653624A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| Оперативное запоминающее устройство | 1976 |

|

SU733019A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU495712A1 |

Авторы

Даты

1980-05-05—Публикация

1977-05-05—Подача