(5) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1986 |

|

SU1336102A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Оперативное запоминающее устройство с самоконтролем | 1974 |

|

SU562007A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

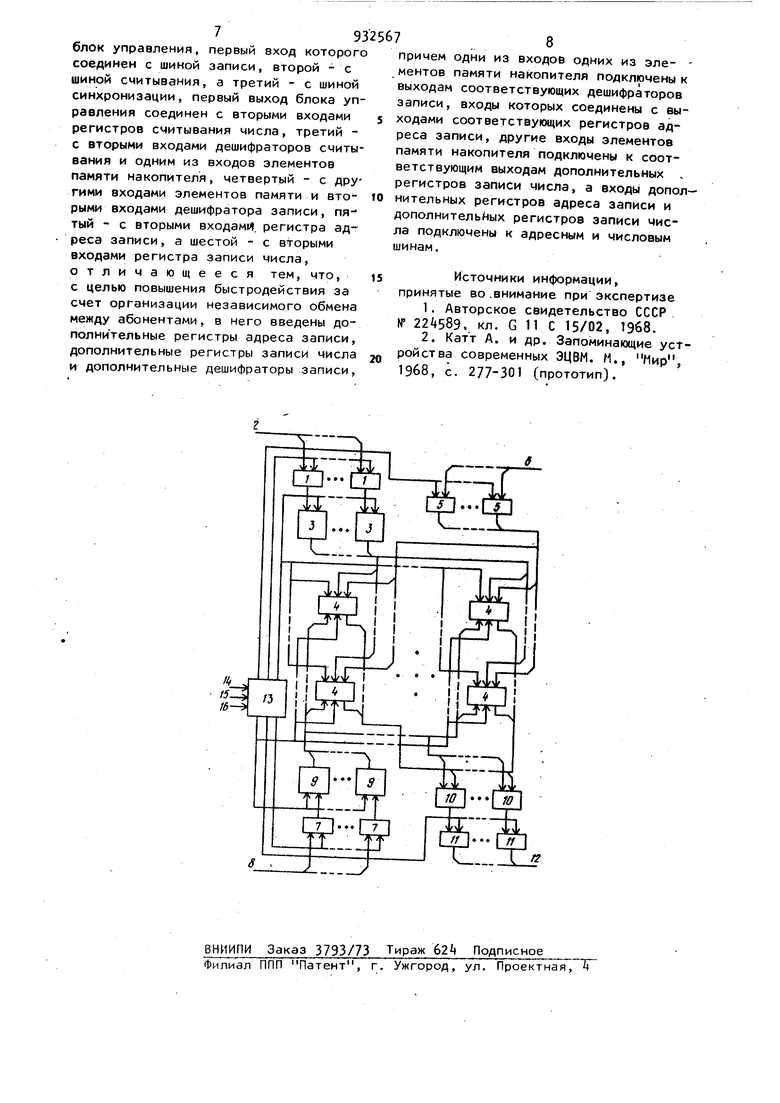

Изобретение относится к вычислительной технике и Может быть использовано при обмене информацией в многопроцессорных вычислительных системах. Известно многоканальное запоМинаЮ1Дее устройство, представляющее многофункциональное запоминающее уст ройство для многоканального пересчета единичных приращений с пространствен ным делением нескольких каналр записи, содержащее ячейки памяти с элементами памяти на ферритовых сердечниках, формирователи сигналов по адресным, разрядным и установочным шинам, усилители считывания, триггеры переноса., которые хранят перед записью поступившие по каналам записи сигналы, схемы управления суммированием во всех ячейках памяти fl. Недостатками этого устройства яв.ляется запоминание информации в виде единичных приращений, что находит сравнительно малое применение и невоз можность одновременного считывания информации из ячеек запоминающего ус тройства с различными адресами. Наиболее близким по технической сущности к предлагаемому является запоминающее устройство, содержащее регистр -адреса записи, первые входа которого соединены с адресной шиной, регистр записи числа, первые входы ко-торого соединеМ) с числовой шиной, регистры адреса считывания, первые входы которых соединены с адресными шинами, а выходы - с первыми входами дешифраторов считывания, выходы которых соединены с входами элементов памяти накопителя и первыми входами элементов И-ИЛИ, выходы которых соединены с первыми входами регистров считывания числа, выходы которых соединены с числовыми шинами, выходы эле-/, ментов памяти соединены с вторыми входами элементов И-ИЛИ, блок управ-: ления, первый вход которого соединен с шиной записи, второй - с шиной считывания, а третий - с шиной синхронизации, первый выход блока управ ления соединен с вторыми входами регистров адреса считывания, второй с вторыми входами регистров считывания числа, третий - с вторыми входами дешифраторов считывания и одними из входов элементов памяти накопителя, четвертый - с другими входами элементов памяти и вторыми входами дешифратора записи, пятый - с вторыми входами регистра адреса записи, а ; шестой - с вторыми входами регистра записи числа . Однако запоминающее устройство не обеспечивает эффективный обмен между несколькими абонентами из-за поочередной записи их информации через один вход, что ограничивает быстродействие запоминающего устройства пр обмене информацией между несколькими абонентами. Цель изобретения - повышение быстродействия запоминающего устройства за счет организации независимог обмена между абонентами. Поставленная цель достигается тем что в запоминающее устройство, содер жащее регистр адреса записи, первые входы которого соединены с адресной шиной, регистр записи числа, первые входы которого соединены с числовой шиной, регистры адреса считывания, первые входы которых соединены с адресными шинами, а вь1ходы - с первыми входами дешифраторов считывания, выходы которых соединены с входами эле ментов памяти накопителя и первыми входами элементов И-ИЛИ, выходы кото рых соединены с первыми входами регистров считывания числа, выходы рых соединены с числовыми шинами, выходы элементов памяти соединены с вторыми входами элементов И-ИЛИ, блок управления, первый которого соединен с шиной записи, второй С шиной считывания, а третий - с шиной синхронизации, первый выход блок управления соединен с вторыми входами регистров адреса считывания, второй - с вторыми входами регситров считывания числа, третий - с вторыми входами дешифраторов считывания и одним из входов элементов памяти нак пителя, четвертый - с другими входам элементов памяти и вторыми входами дешифратора записи, пятый - с вторым входами регистра адреса записи, а шестой - с вторыми входами регистра кот записи числа, введены дополнительные регистры адреса записи, дополнительные регистры записи числа и дополнительные дешифраторы записи, причем одни из входов одних из элементов памяти накопителя подключены к выходам соответствующих дешифраторов записи, входы которых соединены с выходами соответсвующих регистров адреса записи, другие входы элементов памяти накопителя подключены к соответствующим выходам дополнительных регистров записи числа, а входы дополнительных регистров адреса записи и дополнительных регистров записи числа подключены к адресным и числовым шинам. На чертеже представлена структурная схема запоминающего устройства. Запоминающее устройство содержит регистры 1 адреса записи, первые входы которых соединены с адресными шинами 2, а выходы - с первыми входами дешифраторов 3 записи.Выходы каждо-го дешифратора 3 записи соединены с соответствующими входами элементов памяти накопителя , регистры 5 записи числа, первые входы которых соединены с числовой шиной 6. Выходы нсаждого регистра 5 записи числа соединены с входами всех элементов памяти на-копителя .Регистры 7 адреса считывания, первые входы которых соединены с адресными шинами 8, а выходы - с первыми входами дешифраторов 9 считывания . Выходы каждого дешифратора 9 считывания соединены с одними из входов всех элементов памяти накопителя k, а также с первыми входами соответствующих элементов И-ИЛИ 10. Вторые входы каждого элемента И-ИЛИ 10 соединены с выходами каждого элемента памяти k. Выходы элементов И-ИЛИ 10 соединены с первыми входами регистров 11 считывания числа, выходы которых соединены с числовыми шинами 12. Блок 13 управления, первый вход которого соединен с шиной записи, второй - с шиной 15 считывания, а третий - с шиной 16 синхронизации. Первый выход блока 13 управления соединен с вторыми входами регистров 7 адреса считывания, второй - с вторы ми входами регистров 11 считывания числа, третий - с вторыми входами дешифраторов 9 считывания, и одним из входов элементов памяти накопителя k, четвертый - с другими входами элементов памяти накопителя 4 и вторыми вх дами дешифраторов 3 записи, пятый с вторыми входами регистров 1 адреса записи, а шестой - с вторыми входами регистров 5 записи числа. Так как за поминающее устройство имеет высокую конструктивную сложность, то изготовление таких устройств стало возмо ным только с развитием технологии больших интегральных схем. Запоминающее устройство работает в трех режимах: обмена, запоминания и смешанном. Наибольший эффект получается при работе в режиме обмена. Допустим нес колько абонентов одновременно хотят обменяться информацией. Адресные код по шине 2 поступают на входы регистров 1 адреса записи, а коды по шине 6 поступают на входы регистров записи числа. По сигналам по шинам 1 и 16 блок 13 управления вырабатывает управляющие сигналы, по которым работа происходит в следующей последовательности. Адресные коды заносятся в регистры 1 адреса записи, а коды чисел - в регистры 5 записи чис ла, с выхода которых коды чисел поступают на соответствующие входы элементов памяти накопителя i. С выхода каждого дешифратора 3 записивыбира атся по одному элементу памяти накоПиталя 4, т.е. выходы регистров 5 за писи числа подключаются к выходам эл ментов памяти накопителя k в нужном абонентам соответствии по управляюще му сигналу коды чисел переписываются в соответствующие элементы памяти накопителя Ц. В программах абонентов записано, с какими абонентами в данный момент обменивается каждый из них, т.е. в какие элементы памяти не обходимо обратиться, чтобы получить нужную информацию. С этой целью по адресным шинам 8 на входы регистров 7 адреса считывания поступают коды адресов. Затем по сигналам по шинам 15 и 16 блок 13 управления вырабатывает управляющие сигналы, по которым работа происходит в следующей последовательности. Адресные коды заносятся в регистры 7 адреса считывания после чего дешифрируются в дешифраторах 9 считывания. С выхода каждого дешифратора 9 считывания выбирается элемент памяти накопителя k, в котором находится обмениваемая информация нужная в данный момент обратившимся абонентам. Кроме того, эти же сигналы с выхода дешифраторов 9 считывания поступают только на те входы элементов И-ИЛИ 10, которые соответствуют выбранным элементам памяти накопителя и числовой шине 12 запросившего абонента. По сигналу из блока 13 управления коды чисел считываются из элементов памяти, проходят через соответствующие элементы И-ИЛИ 10, заносятся в регистры 11 считывания числа ивыдаются по числовым шинам 12 запросившим их абонентам. Таким образом, за один цикл записи-считывания происходит обмен информацией всех абонентов. Для обмена информацией в другом соответствии между абонентами необходимо поменять в программе соответствие адресов по записи и по считыванию. Необходимо подчеркнуть, что такая структура запоминающего устройства осуществляет не только попарный обмен абонентов, но и одного абонента с многими абонентами. Для этого к элементу памяти с обменной информацией могут обратиться по считыванию нескольких абонентов одновременно. При использовании известных запоминающих устройство для обмена информацией между несколькими абонентами возникают очереди на доступ к памяти - нерационально используется машинное время. Основным преимуществом предлагаемого устройства является возможность программно-управляемого обмена информацией между несколькими абонентами одновременно. Таким образом, экономическая эффективность состоит в экономии дорогостоящего машинного времени. формула изобретения Запоминающее устройство, содержащее регистр адреса Записи, первые входы которого соединены с адресной шиной, регистр записи числа, первые входы которого соединены с числовой шиной, регистры адреса считывания, первые входы которых соединены с . адресными шинами, а выходы - с первыми входами дешифраторов считывания, выходы которых соединены с входами элементов памяти накопителя и первыми входами элементов И-ИЛИ, выходы которых соединены с первыми входами регистров считывания числа, выходы которых соединены с числовыми шинами, выходы элементов памяти соединены с вто.ВЬ1Ми аходащ элементов И-ИЛИ,

Авторы

Даты

1982-05-30—Публикация

1976-10-18—Подача