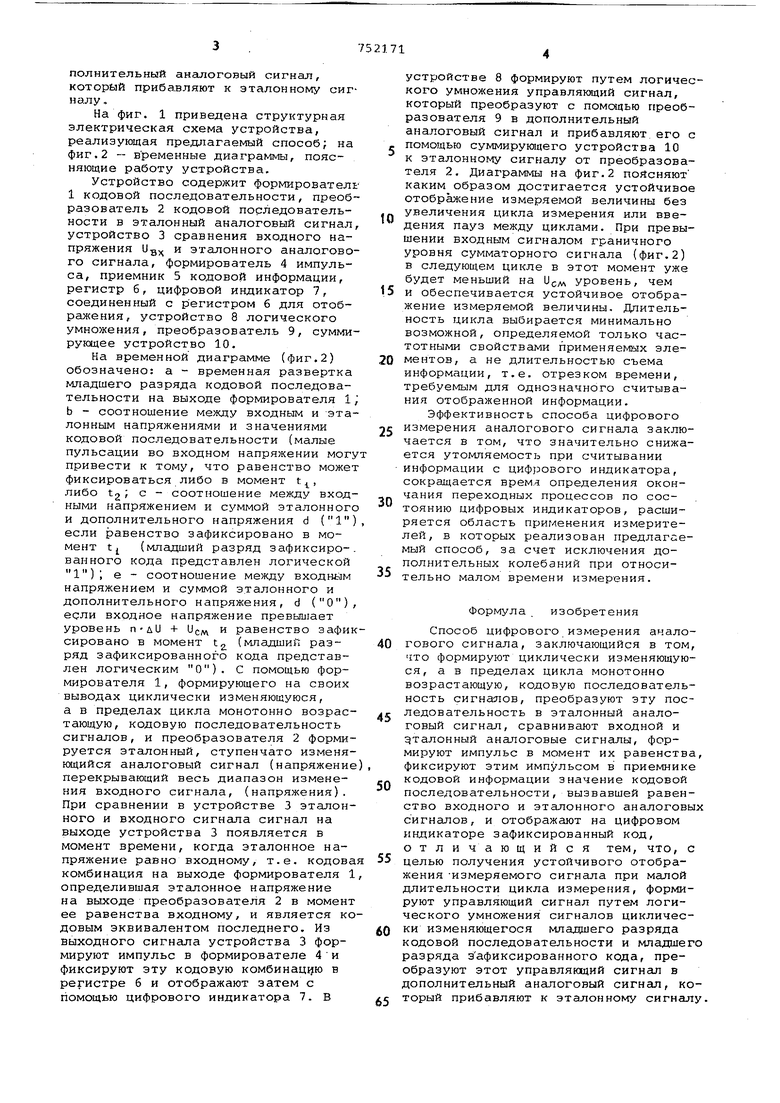

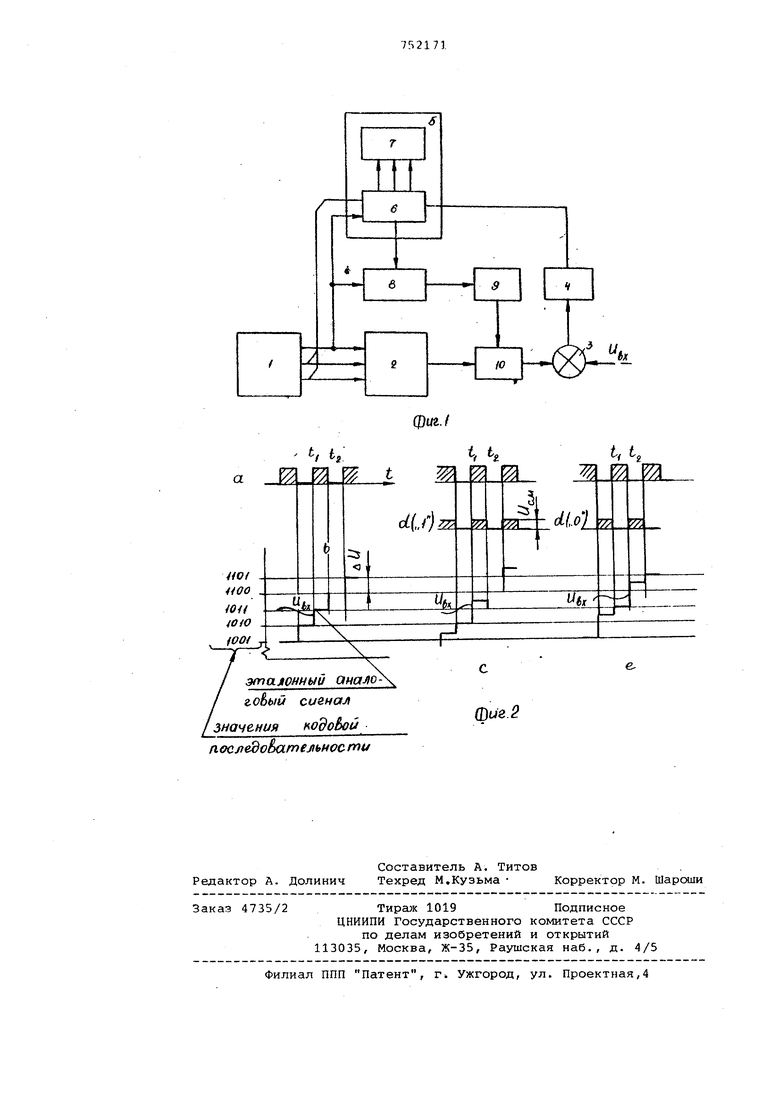

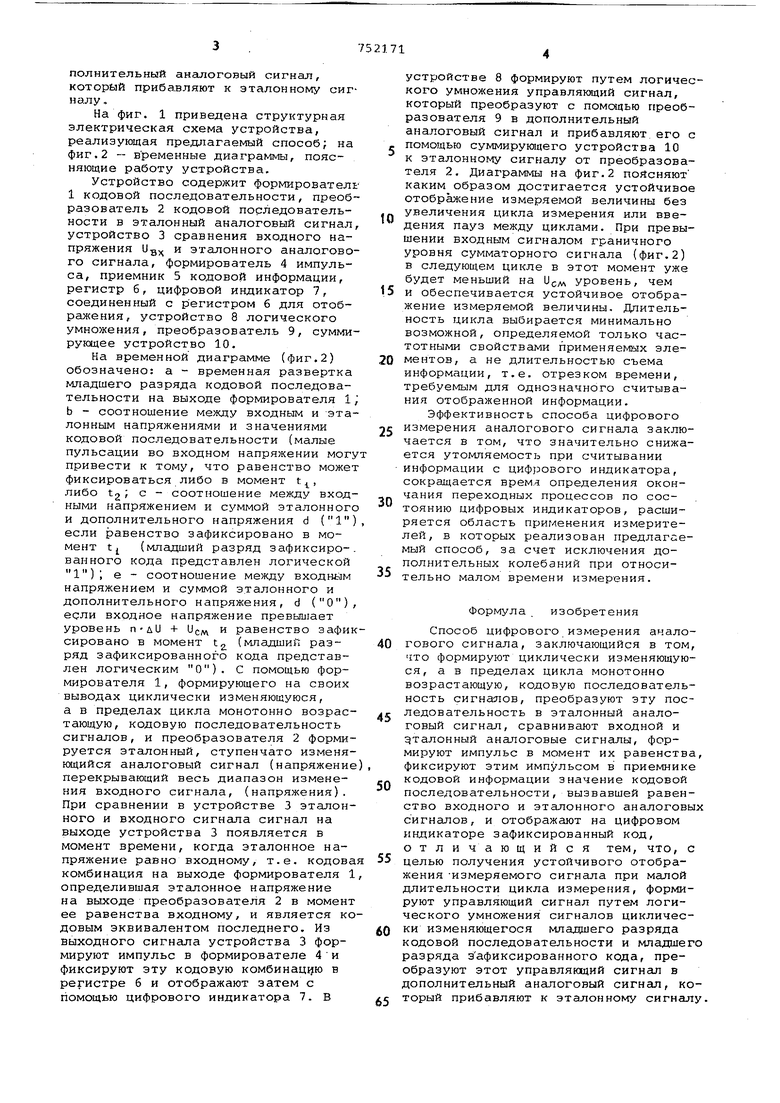

полнительный ангшоговый сигнал, который прибавляют к эталонному сиг налу , На фиг. 1 приведена структурная электрическая схема устройства, реализующая предлагаемый способ; на фиг, 2 -- временные диаграммы, поясняющие работу устройства. Устройство содержит формирователь 1 кодовой последовательности, преобразователь 2 кодовой последовательности в эталонный аналоговый сигнал устройство 3 сравнения входного напряжения и эталонного аналогово го сигнала, формирователь 4 импульса, приемник 5 кодовой информации, регистр 6, цифровой индикатор 7, соединенный с регистром б для отображения, устройство 8 логического умножения, преобразователь 9, сумми рующее устройство 10. На временной диаграмме (фиг.2) обозначено: а - временная развертка младшего разряда кодовой последовательности на выходе формирователя 1 b - соотношение между входным и эта лонным напряжениями и значениями кодовой последовательности (малые пульсации во входном напряжении могу привести к тому, что равенство може фиксироваться либо в момент t, либо tg; с - соотношение между вход ными напряжением и суммой эталонног и дополнительного напряжения d (1 если равенство зафиксировано в момент t (младший разряд зафиксированного кода представлен логической 1); е - соотношение между входнйм напряжением и суммой эталонного и дополнительного напряжения, d (О) если входное напряжение превышает уровень пли + УСДД и равенство зафи сировано в момент tg. (младший разряд зафиксированного кода представлен логическим О). С помощью формирователя 1, формирующего на своих выводах циклически изменяющуюся, а в пределах цикла монотонно возрас тающую, кодовую последовательность сигналов, и преобразователя 2 формируется эталонный, ступенчато изменя ющийся аналоговый сигнал (напряжени перекрывающий весь диапазон изменения входного сигнала, (напряжения). При сравнении в устройстве 3 эталон ного и входного сигнала сигнал на выходе устройства 3 появляется в момент времени, когда эталонное напряжение равно входному, т.е. кодова комбинация на выходе формирователя 1 определившая эталонное напряжение на выходе преобразователя 2 в момент ее равенства входному, и является ко довым эквивалентом последнего. Из выходного сигнала устройства 3 формируют импульс в формирователе 4и фиксируют эту кодовую комбинац1|ю в регистре б и отображают затем с помощью цифрового индикатора 7. В устройстве 8 формируют путем логического умножения управляющий сигнал, который преобразуют с помощью преобразователя 9 в дополнительный аналоговый сигнал и прибавляют его с помощью суммирующего устройства 10 к эталонному сигналу от преобразователя 2. Диаграммы на фиг.2 поясняют каким образом достигается устойчивое отображение измеряемой величины без увеличения цикла измерения или введения пауз между циклами. При превышении входным сигналом граничного уровня сумматорного сигнала (фиг.2) в следующем цикле в этот момент уже будет меньший на Ucл уровень, чем и обеспечивается устойчивое отображение измеряемой величины. Длительность цикла выбирается минимально возможной, определяемой только частотными свойствами применяеглах элементов, а не длительностью съема информации, т.е. отрезком времени, требуемым для однозначного считывания отображенной информации. Эффективность способа цифрового измерения аналогового сигнала заключается в том, что значительно снижается утомляемость при считывании информации с цифрового индикатора, сокращается времл определения окончания переходных процессов по состоянию цифровых индикаторов, расширяется область применения измерителей, в которых р)еализован предлагаемый способ, за счет исключения дополнительных колебаний при относительно малом времени измерения. Формула изобретения Способ цифрового измерения аналогового сигнала, заключающийся в том, что формируют циклически изменяющуюся, а в пределах цикла монотонно возрастающую, кодовую последовательность сигналов, преобразуют эту последовательность в эталонный аналоговый сигнал, сравнивают входной и :5талонный аналоговые сигналы, формируют импульс в момент их равенства, фиксируют этим импульсом в приемнике кодовой информации значение кодовой последовательности, вызвавшей равенство входного и эталонного аналоговых сигналов, и отображают на цифровом индикаторе зафиксированный код, отличающийся тем, что, с целью получения устойчивого отображения -измеряемого сигнала при малой длительности цикла измерения, формируют управляющий сигнал путем логического умножения сигналов циклически изменяющегося младшего разряда кодовой последовательности и младшего разряда зафиксированного кода, преобразуют этот управляЕоций сигнал в дополнительный аналоговый сигнал, который прибавляют к эталонному сигналу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1978 |

|

SU807371A1 |

| Цифровой измеритель напряжения | 1978 |

|

SU712766A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СОСТОЯНИЯ ОБОРУДОВАНИЯ НЕФТЯНЫХ СКВАЖИН | 2000 |

|

RU2184226C1 |

| Генератор напряжений | 1990 |

|

SU1728978A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Формирователь сигналов | 1988 |

|

SU1598198A2 |

| СИСТЕМА УЧЕТА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2003 |

|

RU2247994C1 |

i.

i, I,

t, t,

(Ьиг.2

Авторы

Даты

1980-07-30—Публикация

1978-07-31—Подача