1

с выходами первого и второго дифференцирующих элементов, а четвертый и пятый входы - соответственно с выходами старшего и предшествующего разрядов шифратора позиционного кода в двоичный.

2. Преобразователь по п. 1, отличающийся тем, что блок коррекции выполнен на.первом и втором триггерах, трех двухвходовых элементах И, трех четырехвходовых элементах И,трех элементах ИЛИ, дифференцирующем элементе, блоке инверторов и блоке элементов задержки входы которого являются четвертым и пятым входами блока коррекции, . первьй вход которого объединен с первыми входами первого и второго двухвходовых и всех четырехвходовых элементов И и входом дифференцирующего элемента, выход которого соединен с вторым входом второго двух- входового элемента И, выход которого подключен к первому входу третьего двухвходового элемента И, второй вход которого соединен с выходом первого элемента выход - с первыми входами второго и третьего элементов ИЛИ, вторые входы которых подключены соответственно к выходам первого двухвходового и третьего четырехвходового элементов И, а выходы - соответствэнно к первым входам первого и второго триггеров, вторые входы которых соответственно соединены с выходами первого и второго четьфехвходовых элементов И, а выходы подключены к соответствующим входам первого элемента ИЛИ и являются соответственно первым и вторым выходами блока коррекции, второй вход которого объединен с вторыми входами первого двухвходового элемента И и второго четырехИзобретение относитс.я к вычислительной и измерительной технике и может быть использовано для преобразования аналоговых сигналов в двоичный код.

Цель изобретения - повьш1ение точности за счет одновременного форми81

вхйдового элемента И, третий и четвертый входы которого объединены соответственно с вторым и третьим

входами третьего четырехвходового элемента И и подключены к соответствующим выходам блока инверторов, входы которого соответственно объединены с вторым и третьим входами первого четьфехвходового элемента И и подключены к соответствующим выходам блока элементов задержки, причем че- вертые входы первого и третьего четьфехвходовых элементов И объединены и являются третьим входом блока коррекции.

3. Преобразователь по п. 1, о т - личающийся тем, что каждый канал преобразования младших разрядов выполнен на. цифроаналоговом преобразователе, первом и втором ис- точниках эталонных напряжений, первом и втором аналоговых сумматорах, делителе напряжения, блоке компараторов и блоке элементов И-НЕ, выходы которого являются соответствующи- Mii выходами канала преобразования младших разрядов, а входы ссответст- .венно подключены к выходам блока компараторов, первые входы которого объединены и являются аналоговым входом канала преобразования младших разрядов, цифровые входы которого соединены с соответствукядими входами цифроаналогового преобразователя, выход которого соединен с первыми входами аналоговых сумматоров, вто-; рые входы которых подключены к выходам соответствующих источников эталонных напряжений, а выходы - к соответствующим входам делителя напряжения, выходы которого соединены с соответствующими вторыми входами блока компараторов.

рования кодов старших и младших разрядов.

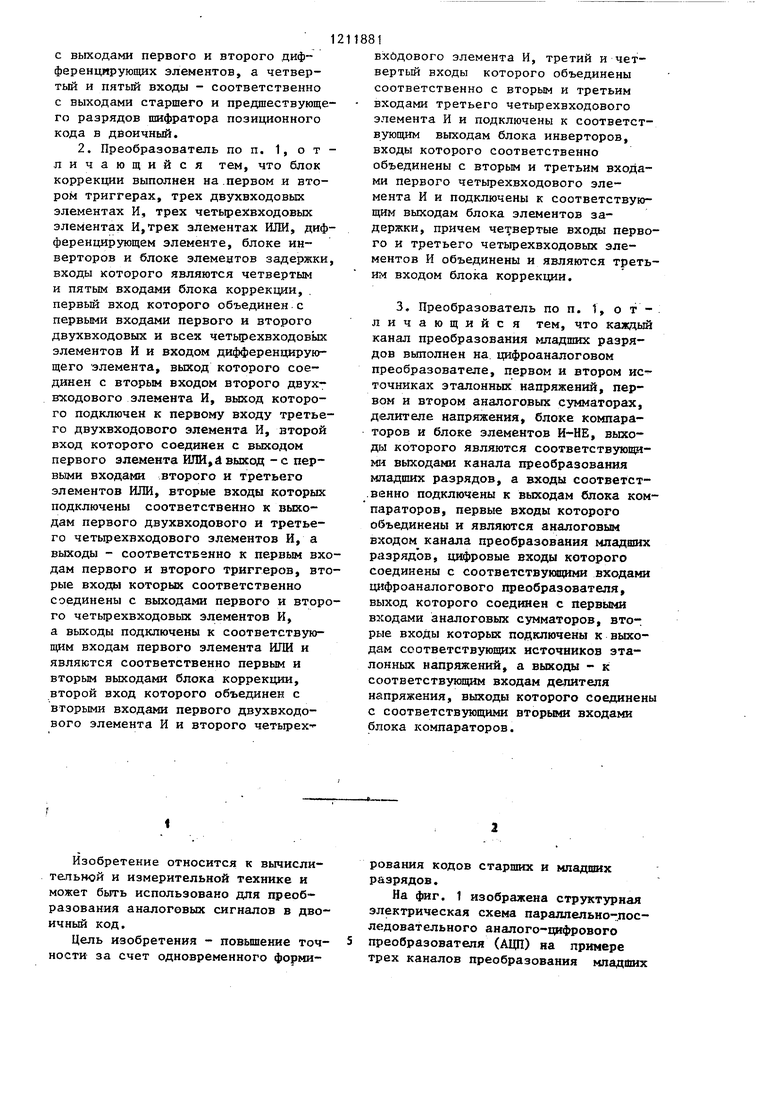

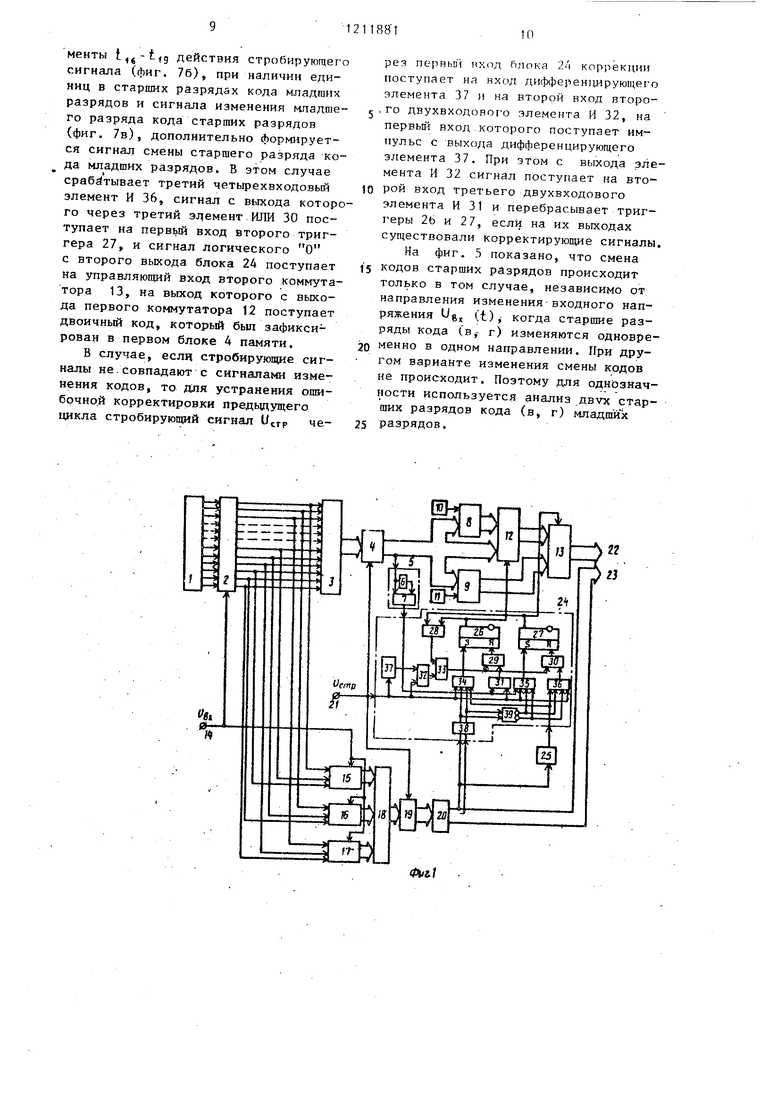

На фиг. 1 изображена структурная электрическая схема параллельно-,пос- ледовательного аналого-цифрового преобразователя (АЦП) на примере трех каналов преобразования младших

3

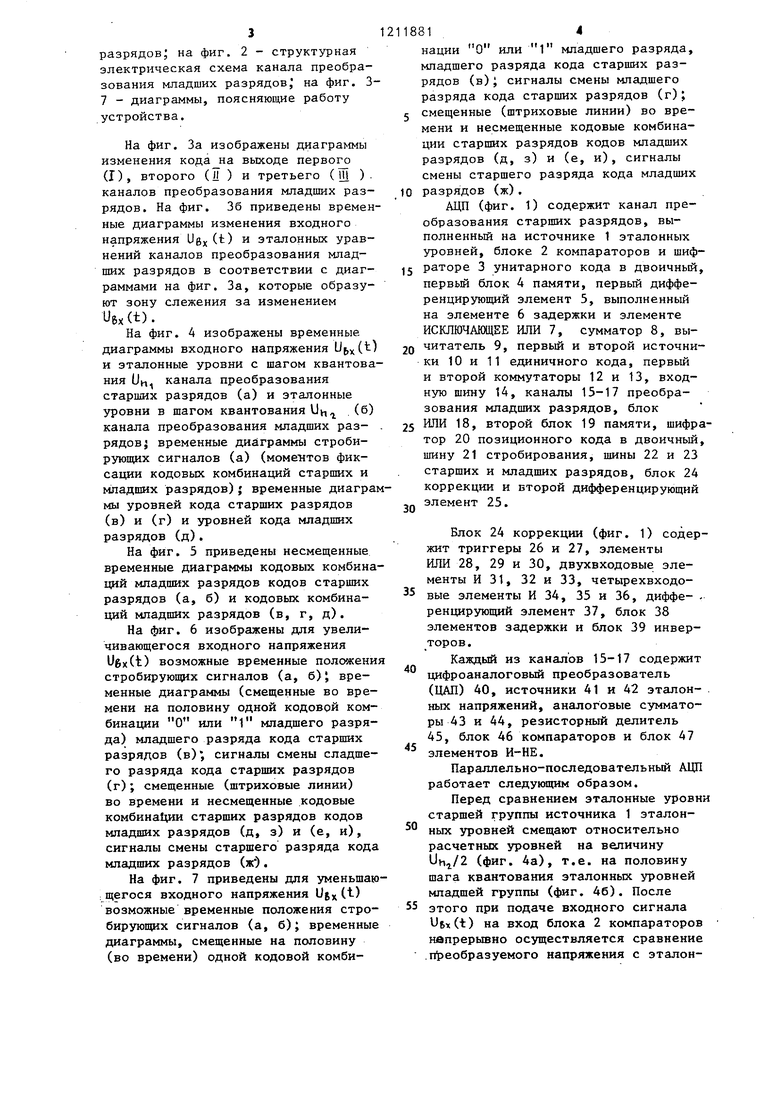

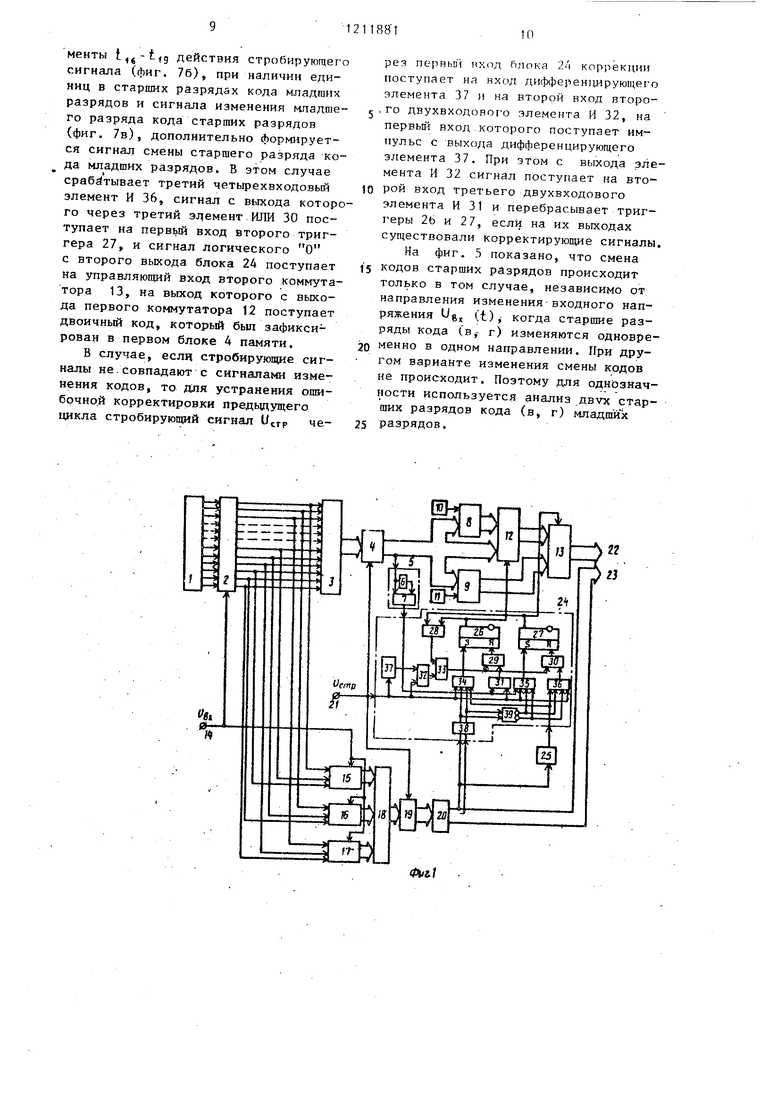

разрядов; на фиг. 2 - структурная электрическая схема канала преобразования младших разрядов, на фиг. 3- 7 - диаграммы, поясняющие работу устройства.

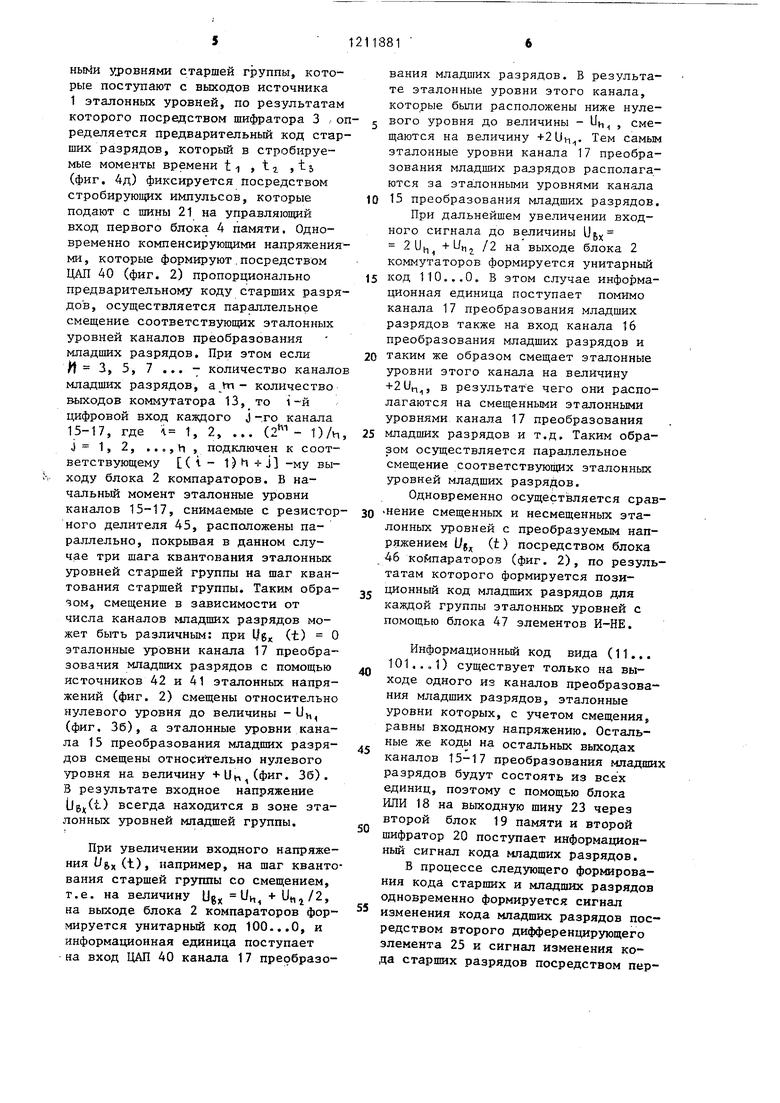

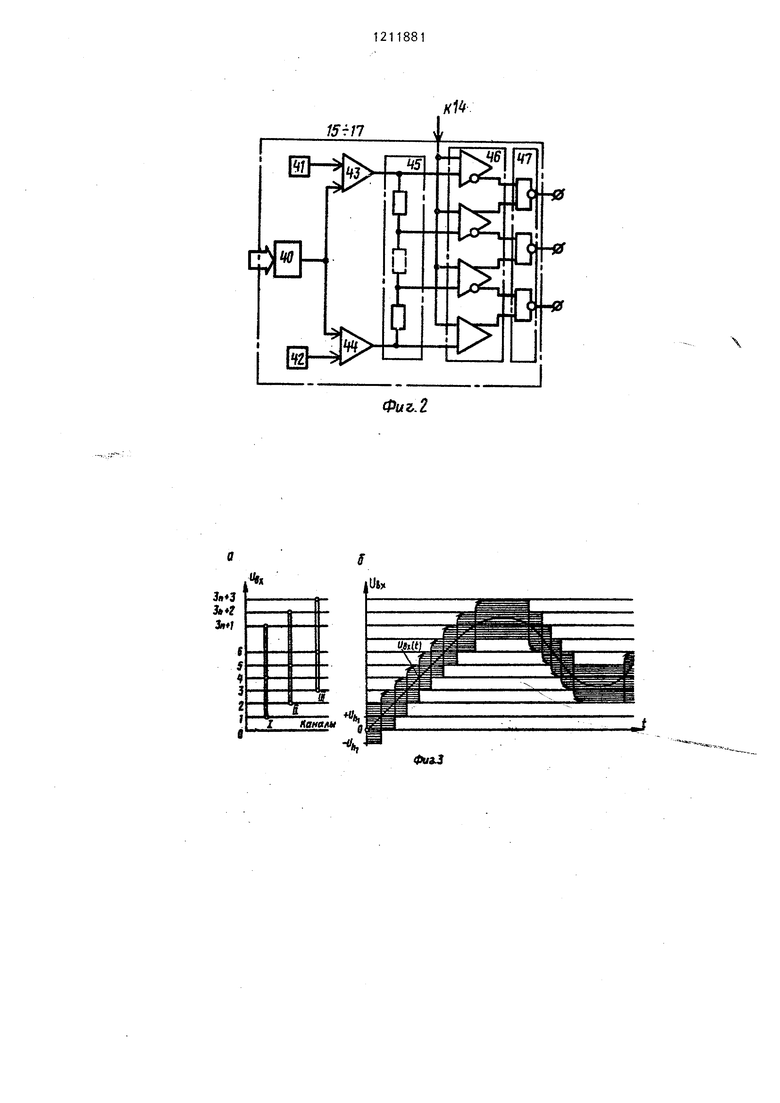

На фиг. За изображены диаграммы изменения выходе первого (Г), второго (Л ) и третьего (Ш ). каналов преобразования младших разрядов. На фиг. 36 приведены временные диаграммы изменения входного напряжения Ugj; (t) и эталонных уравнений каналов преобразования младших разрядов в соответствии с диаграммами на фиг. За, которые образуют зону слежения за изменением

U6x(t).

На фиг. 4 изображены временные диаграммы входного напряжения Uf,(t) и эталонные уровни с шагом квантования DH, канала преобразования старших разрядов (а) и эталонные уровни в шагом квантования U, (б) канала преобразования младших раз- рядов; временные диаграммы строби- рующих сигналов (а) (моментов фиксации кодовых комбинаций старших и младших разрядов); временные диаграмы уровней кода старших разрядов (Б) и (г) и уровней кода младпшх разрядов (д).

На фиг. 5 приведены несмещенные временные диаграммы кодовых комбинаций младших разрядов кодов старших разрядов (а, б) и кодовых комбинаций младших разрядов (в, г, д).

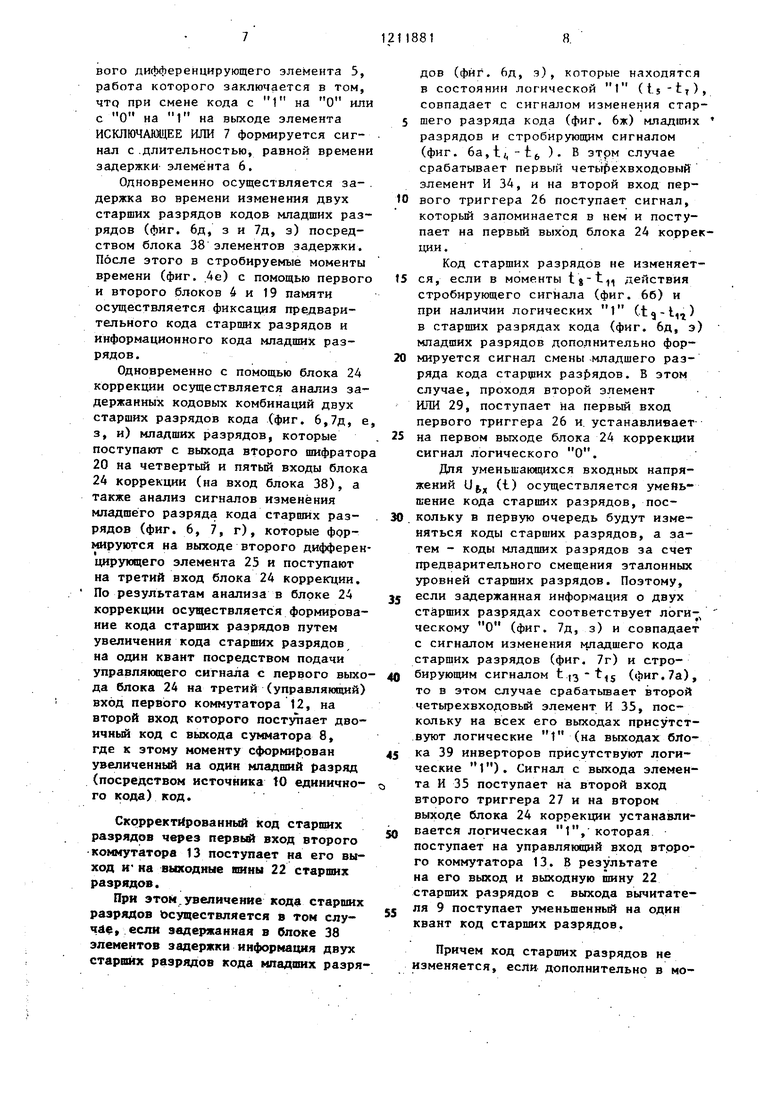

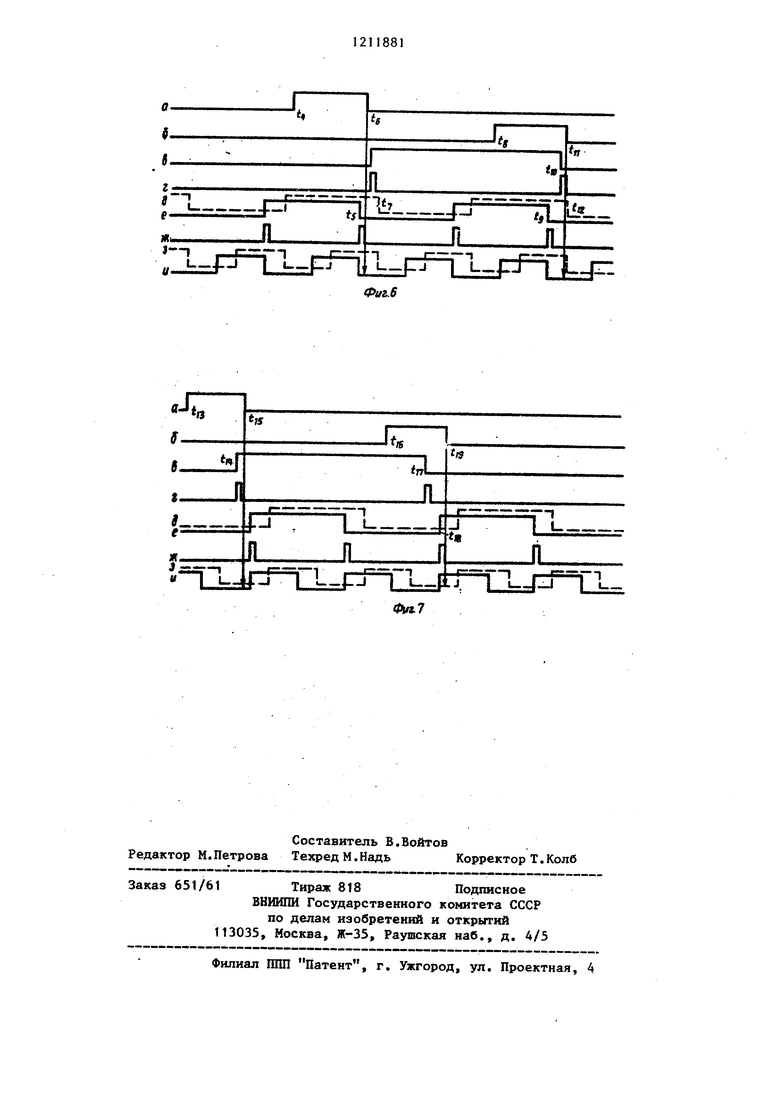

На фиг. 6 изображены для увеличивающегося входного напряжения UgxCt) возможные временные положени стробирующих сигналов (а, б); временные диаграммы (смещенные во времени на половину одной кодовой комбинации О или 1 младшего разряда) младшего разряда кода старших разрядов (в), сигналы смены сладше- го разряда кода старших разрядов (г); смещенные (штриховые линии) во времени и несмещенные кодовые комбинации старших разрядов кодов младших разрядов (д, з) и (е, и), сигналы смены старшего разряда кода младших разрядов (ж ).

На фиг. 7 приведены для уменьшаю ;щегося входного напряжения Uj t) возможные временные положения стробирующих сигналов (а, б); временные диаграммы, смещенные на половину (во времени) одной кодовой комби118814

нации О или 1 младшего разряда, младшего разряда кода старших разрядов (в); сигналы смены младшего разряда кода старших разрядов (г);

5 смещенные (штриховые линии) во времени и несмещенные кодовые комбинации старших разрядов кодов младших разрядов (д, з) и (е, и), сигналы смены старшего разряда кода младших

10 разрядов (ж).

АЦП (фиг. 1) содержит канал преобразования старших разрядов, выполненный на источнике 1 эталонных уровней, блоке 2 компараторов и шиф,5 раторе 3 унитарного кода в двоичный, первый блок 4 памяти, первый дифференцирующий элемент 5, выполненный на элементе 6 задержки и элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 7, сумматор 8, вы2Q читатель 9, первый и второй источники 10 и 11 единичного кода, первый и второй коммутаторы 12 и 13, входную шину 14, каналы 15-17 преобразования младших разрядов, блок

25 ИЛИ 18, второй блок 19 памяти, шифратор 20 позиционного кода в двоичный, шину 21 стробирования, шины 22 и 23 старших и младших разрядов, блок 24 коррекции и второй дифференцирующий

, элемент 25.

Блок 24 коррекции (фиг. 1) содержит триггеры 26 и 27, элементы ИЛИ 28, 29 и 30, двухвходовые элементы И 31, 32 и 33, четырехвходо- 35 вые элементы И 34, 35 и 36, диффе- - ренцирующий элемент 37, блок 38 элементов задержки и блок 39 инверторов.

Каждый из каналов 15-17 содержит цифроаналоговый преобразователь (ЦАП) 40, источники 41 и 42 эталонных напряжений, аналоговые сумматоры 43 и 44, резисторный делитель 45, блок 46 компараторов и блок 47 элементов И-НЕ.

Параллельно-последовательный АЦП работает следующим образом.

Перед сравнением эталонные уровни старшей группы источника 1 эталон- ных уровней смещают относительно расчетных уровней на величину (фиг. 4а), т.е. на половину шага квантования эталонных уровней младшей группы (фиг. 46). После 55 этого при подаче входного сигнала U6x(t) на вход блока 2 компараторов непрерывно осуществляется сравнение .преобразуемого напряжения с эталон40

ныйи уровнями старшей группы, которые постзгаают с выходов источника 1 эталонных уровней, по результатам которого посредством шифратора 3 . оределяется предварительный код старших разрядов, который в стробируе- мые моменты времени t ч , t ,1, (фиг, 4д) фиксируется посредством стробирующих импульсов, которые подают с шины 21 на управляющий вход первого блока 4 памяти. Одновременно компенсирующими напряжениями, которые формируют.посредством ЦАП 40 (фиг. 2) пропорционально предварительному коду старших разрядов, осуществляется параллельное смещение соответствующих этгшониых уровней каналов преобразования младших разрядов. При этом если 3, 5, 7 ... - количество канало младщих разрядов, ajm- количество выходов коммутатора 13, то i-и цифровой вход каждого J-го канала 15-17, где 1, 2, ... ( 1)/и j 1, 2, ..,,1 подключен к соответствующему (i- 1)H-i-J -му выходу блока 2 компараторов. В начальный момент эталонные уровни каналов 15-17, снимаемые с резистор ного делителя 45, расположены параллельно, покрьшая в данном случае три шага квантования эталонных уровней старшей группы на шаг квантования старшей группы. Таким обра- чом, смещение в зависимости от числа каналов младших разрядов может быть различным: при Ug (t) О эталонные уровни канала 17 преобразования младших разрядов с помощью источников 42 и 41 эталонных напряжений (фиг. 2) смещены относительно нулевого уровня до величины - U, (фиг. Зб), а эталонные уровни канала 15 преобразования младших разрядов смещены относительно нулевого уровня на величину + UK, (фиг. Зб). В результате входное напряжение ) всегда находится в зоне эталонных уровней младшей группы.

При увеличении входного напряжения Uftx(t), например, на шаг квантования старшей группы со смещением, т.е. на величину Ugx и /2, на выходе блока 2 компараторов формируется унитарный код 100...О, и информационная единица поступает на вход ЦАП 40 канала 17 преобразования младших разрядов. В результате эталонные уровни этого канала, которые бьши расположены ниже нулевого уровня до величины

- UH

смещаются на величину +2UH. Тем самым эталонные уровни канала 17 преобразования младших разрядов располагаются за эталонными уровнями канала

15 преобразования младших разрядов. При дальнейшем увеличении входного сигнала до величины 2Up, +UMJ /2 на выходе блока 2 коммутаторов формируется унитарный

код 110...0„ В этом случае информационная единица поступает помимо канала 17 преобразования младших разрядов также на вход канала 16 преобразования младших разрядов и

таким же образом смещает эталонные уровни этого канала на величину +2Ut, в результате чего они располагаются на смещенными эталонными уровнями канала 17 преобразования

младших разрядов и т.д. Таким образом осуществляется параллельное смещение соответствуюпщх эталонных уровней младших разрядов.

Одновременно осущест1вляется срав-нение смещенных и несмещенных эта- лонньпс уровней с преобразуемым напряжением и (t) посредством блока 46 койпараторов (фиг. 2), по результатам которого формируется пози1ДИОННЫЙ код младших разрядов для каждой группы эталонных уровней с помощью блока 47 элементов И-НЕ.

0

5

0

5

Информационный код вида (11... 101..„1) существует только на выходе одного из каналов преобразования младщих разрядов, эталонные уровни которых, с учетом смещения, равны входному напряжению. Остальные же коды на остальных выходах каналов 15-17 преобразования младших разрядов будут состоять из все х единиц, поэтому с помощью блока ИЛИ 18 на выходную шину 23 через второй блок 19 памяти и второй шифратор 20 поступает информационный сигнал кода младших разрядов.

В процессе следующего формирования кода старших и младших разрядов одновременно формируется сигнал изменения кода младших разрядов посредством второго дифференцирующего элемента 25 и сигнал изменения кода старших разрядов посредством первого дифференцирующего элемента 5, работа которого заключается в том, 4TQ при смене кода с 1 на О или с О на 1 на выходе элемента ИСКЛЮЧАНХЦЕЕ ИЛИ 7 формируется сиг- нал с .длительностью, равной времени задержки элемента 6.

Одновременно осуществляется за- держка во времени изменения двух старших разрядов кодов младших разрядов (фиг. 6д, 3 и 7д, з) посредством блока 38 элементов задержки. После этого в стробируемые моменты времени (фиг. 4е) с помощью первого и второго блоков 4 и 19 памяти осуществляется фиксация предварительного кода старших разрядов и информационного кода младших разрядов.

Одновременно с помощью блока 24 коррекции осуществляется анализ задержанных кодовых комбинаций двух старших разрядов кода (фиг. 6,7д, е 3, и) младших разрядов, которые поступают с выхода второго пшфратор 20 на четвертый и пятьй входы блока 24 коррекции (на вход блока 38), а также анализ сигналов изменения младшего разряда кода старших раз- рядов (фиг. 6, 7, г), которые Формируются на выходе второго дифференцирующего элемента 25 и поступают на третий вход блока 24 коррекции. По результатам анализа в блоке 24 коррекции осуществляется формирование кода старших разрядов путем увеличения кода старших разрядов на один квант посредством подачи управляющего сигнала с первого выхо да блока 24 на третий (управляю1ций) вход первого коммутатора 12, на второй вход которого поступает двоичный код с выхода сумматора 8, где к этому моменту сформи(рван увеличенный на один младший разряд (посредством источника 10 единично- го кода) код.

Скорректированный код старших разрядов через первый вход второго коммутатора 13 поступает на его выход и- на выходные шины 22 старших разрядов.

При этом.увеличение кода старших разрядов Ьсуществляется в том слу- 4de если задержанная в блоке 38 элементов задержки информация двух старших разрядов кода младших разря5

0 15 0

5 0 j 0 з

дов (фиг. 6д, э), которые находятся в состоянии логической 1 (ts t), совпадает с сигналом изменения старшего разряда кода (фиг. 6ж) млад1пих разрядов и стробирующим сигналом (фиг. 6a,tj, -tfe ). В зтрм случае срабатывает первый четы ехвходовый элемент И 34, и на второй вход первого триггера 26 поступает сигнал, который запоминается в нем и поступает на первый выход блока 24 коррекции.

Код старших разрядов не изменяется, если в моменты tg-t,,, действия стробирующего сигнала (фиг. 66) и при наличии логических 1 ) в старших разрядах кода (фиг. 6д, э) мпадших разрядов дополнительно фор- шруется сигнал смены-младшего разряда кода старщих разрядов. В этом случае, проходя второй элемент ШШ 29, поступает на первый вход первого триггера 26 и. устанавливает на первом выходе блока 24 коррекции сигнал логического О.

Для уменьшающихся входных напряжений (t) осуществляется умейь- шение кода старших разрядов, поскольку в первую очередь будут изменяться коды старших разрядов, а затем - коды младших разрядов за счет предварительного смещения эталонных уровней старших разрядов. Поэтому, если задержанная информация о двух старших разрядах соответствует логи-, ческому О (фиг. 7д, з) и совпадает с сигналом изменения младшего кода старших разрядов (фиг. 7г) и стробирующим сигналом t. (фиг.7а), то в этом случае срабатьшает второй четырехвходовый элемент И 35, поскольку на всех его выходах присутствуют логические 1 (на выходах блока 39 инверторов присутствуют логические 1). Сигнал с выхода элемента И 35 поступает на второй вход второго триггера 27 и на втором выходе блока 24 коррекции устанавливается логическая 1, которая поступает на управляющий вход второго коммутатора 13. В результате на его выход и выходную шину 22 старших разрядов с выхода вычитате- ля 9 поступает уменьшенньй на один квант код старших разрядов.

Причем код старших разрядов не изменяется, если дополнительно в моменты действия стробиругощего сигнала (фиг. 7б), при наличии единиц в старших разрядах кода младших разрядов и сигнала изменения ипадше- го разряда кода старших разрядов {фиг. 7в), дополнительно формируется сигнал смены старшего разряда кода младших разрядов. В этом случае срабатывает третий четырехвходовый элемент И 36, сигнал с выхода которого через третий элемент ИЛИ 30 поступает на первьй вход второго триггера 27, и сигнал логического О с второго выхода блока 24 поступает на управляющий вход второго коммутатора 13, на выход которого с вько- да первого коммутатора 12 поступает двоичный код, который был зафиксирован в первом блоке 4 памяти.

В случае, если стробирующие сиг- калы не.совпадают с сигналами изменения кодов, то для устранения ошибочной корректировки предьщущего цикла стробирующий сигнал чеез перньп пход блока 2ч коррекции оступает на вход дис}х|}ерен1Щрующего элемента 37 и на второй вход второ- го двухвходового элемента И 32, на первьш вход которого поступает импульс с выхода дифференцирующего элемента 37. При этом с выхода элемента И 32 сигнал поступает на второй вход третьего двухвходового

элемента И 31 и перебрасывает триггеры 26 и 27, если на их выходах существовали корректирующие сигналы. На фиг. 5 показано, что смена

кодов старших разрядов происходит только в том случае, независимо от направления изменения входного напряжения Ug (t), когда старшие разряды кода (в,- г) изменяются одновременно в одном направлении. При другом варианте изменения смены кодов не происходит. Поэтому для однозначности используется анализ ДВУХ старших разрядов кода (в, г) младших

разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ следящего аналого-цифрового преобразования и устройство для его осуществления | 1983 |

|

SU1229954A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1193809A1 |

| Устройство для преобразования интервалов времени в цифровой код | 1985 |

|

SU1411701A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

| Устройство для измерения концентрации пыли в воздухе | 1985 |

|

SU1257477A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1202055A1 |

Фиг. 2

J/i«3

If

f

f

ч

3

г

.1 Капам

ФилЗ

0.

.

JL

Составитель В.Войтов Редактор М.Петрова Техред М.Надь Корректор Т.Колб

651/61

Тираж 818 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

ff

f -K,

J- П

U.

| Патент США № 3710377, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Параллельно-последовательский пре-ОбРАзОВАТЕль НАпРяжЕНия B КОд | 1977 |

|

SU799131A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-15—Публикация

1983-12-27—Подача