I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и системах .автоматического управления для сравнения чисел с заданным допуском сравнения.

Известно устройство для сравнения чисел динамического типа, содержащее элементы И, ИЛИ, триггеры 1 .

Недостатками данного устройства являются низкое быстродействие, сравнение лишь модулей чисел и невозможность изменения допуска сравнения.

Наиболее близким к предлагаемому техническим решением является устройст- во для сравнения чисел, содержащее сумматоры, элементы И, ИЛИ, дешифратор 2 .

Недостатки этого устройства заключаются в невозможности изменения допуска сравнения, в необходимости предваритель-jg ного Преобразования одного из чисел в дополнительный код, что ведет к увеличению аппаратурных затрат, и в сравнении лишь модулей чисел без учета их знаков.

Цель изобретения - расширение функциональных возможностей путем обеспечения смены кодов допусков и сравнения чисел с учетом их знаков.

Поставленная цель достигается тем, что в устройство для сравнения чисел, содержащее два сумматора, где первая группа входов первого сумматора соединена с входными шинами первого числа, введены два узла согласования, преобразователь прямого кода в обратный, элемент равнозначности, два узла анализа, причем входные шины второго числа соединены со входами первого узла cariiaco ваная, выходы которого подключены ко второй группе входов первого сумматора, 1,2,...к-ый выходы которого соединены со входами второго узла согласования, выходы которого подключены к первой группе входов второго сумматора, вторая грутша входов которого соединена с выходами , преобразователя прямого кода в обратный, входы которого подключены к входным шинам кода допуска, вькод переноса второго сумматора соединен с управляющим входом первого узла анализа входные шины знаковых разрядов чисел подключены ко входам элемента равнозначности, выход которого соединен со знаковым входом первого сумматора и со входом управлени первого узла согласованая (к+1), (к+2)... П -ый выходы первого сумматора, где п число разрядов сравниваемых чисел, подключены к 1,2,...(п-к)-ому входам первого узла анализа соответственно,знаковый выход первого сумматора соединен со знаковым входом первого узла анализа и со входом управления второго узла сопилсования, выход переноса первсго сумматс а подключен к первому входу второго узла анализа и ко входу переносов второго сумматора, первый выход первого узла анализа соединен со вторым входом второго узла анализа, входная шина знакового раз ряда первого числа подключена к третьему входу второго узла анализа, и тем, что в устройстве первый узел анализа содержит элемент запрета, элемент ИЛИ-НЕ и элемент ИЛИ, причем 1,2,... (п-«:)-ый входы узла анализа соединены с 1,2,..,(п-к)ол информационными входами элемента запрета и с 1,2,... (п-к)-ым входами элемента ИЛИ-НЕ, знаковый вход узла анализа подключен к (и-к+1)-ому информационному входу элемента запрета и к (п-к+1)-ому входу элемента ИЛИ-НЕ, (П-к+2)-ой вход элемента ИЛИ-НЕ и управляющий вход элемента запрета соединены с управляющим входом узла анализа, вьгходы элемента ИЛИ-НЕ и элемента запрета подключены ко входам элемента ИЛИ, прямой выход которого соединен с первым выходом узла анализа, а инверсный - со вторым вь1ходом узла анализа, а также тем, что в нем второй узел анализа содержит элемент запрета, элементы ИЛИ-НЕ, ИЛИ , причем первый вход узла анализа соединен с первым информационным входом элемента запрета и с первым входом первого элемента ИЛИ-НЕ, выход которого подключен к первому входу элемента ИЛИ, втсфой вход узла анализа соединен со входами управления элемента запрета, со вторым входом первого элемента ИЛИ-НЕ и с первым входом второго элемента , второй вход которого подключен к выходу элемента ИЛИ,. третий вход узла анализа соединен со втсрым информационным входом элемента запрета в с третьим входом первого элемента ИЛИ-ИЕ.

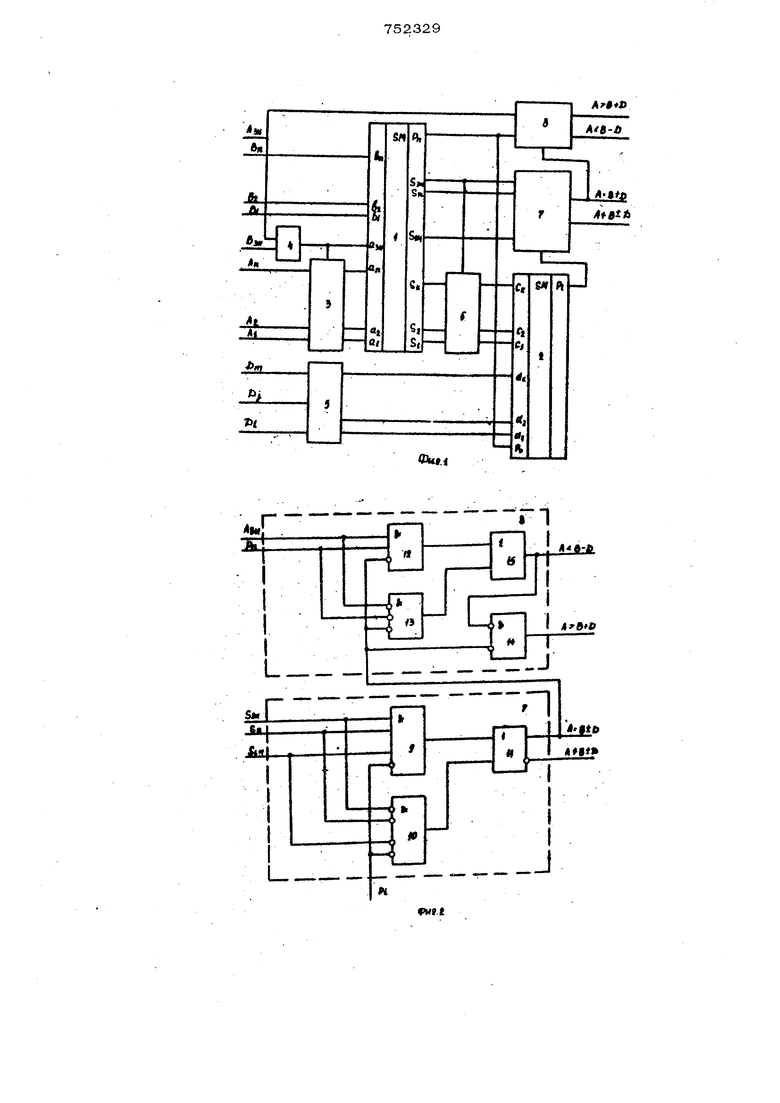

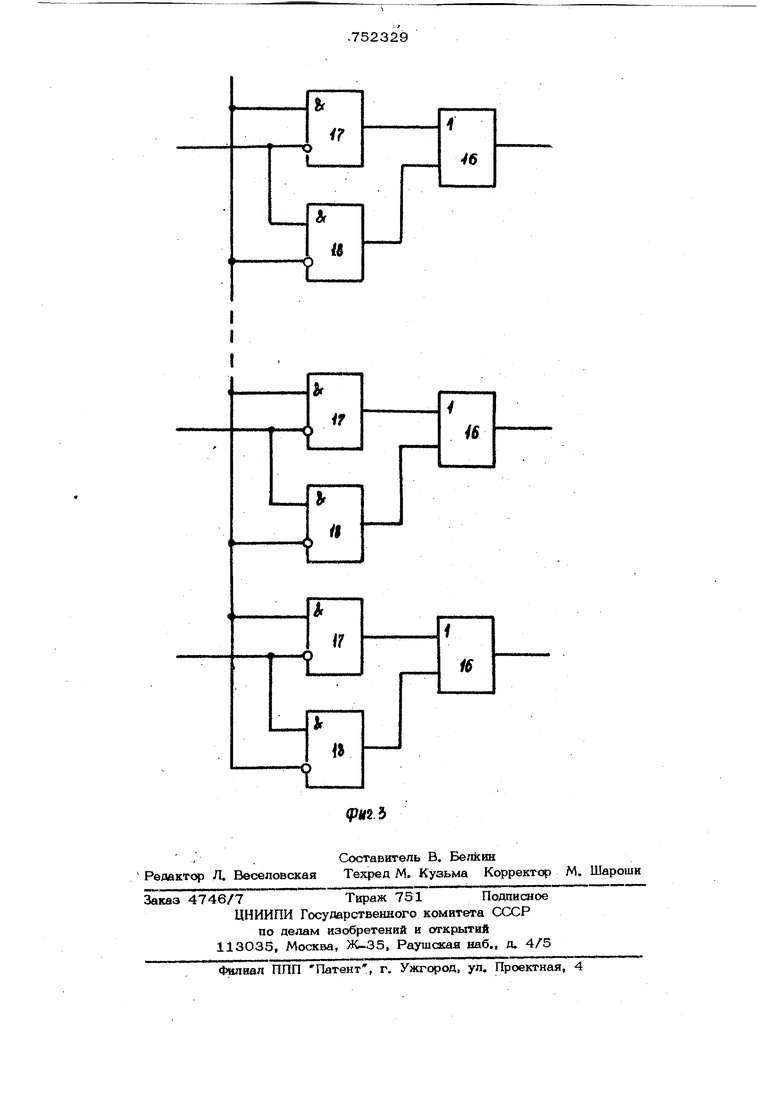

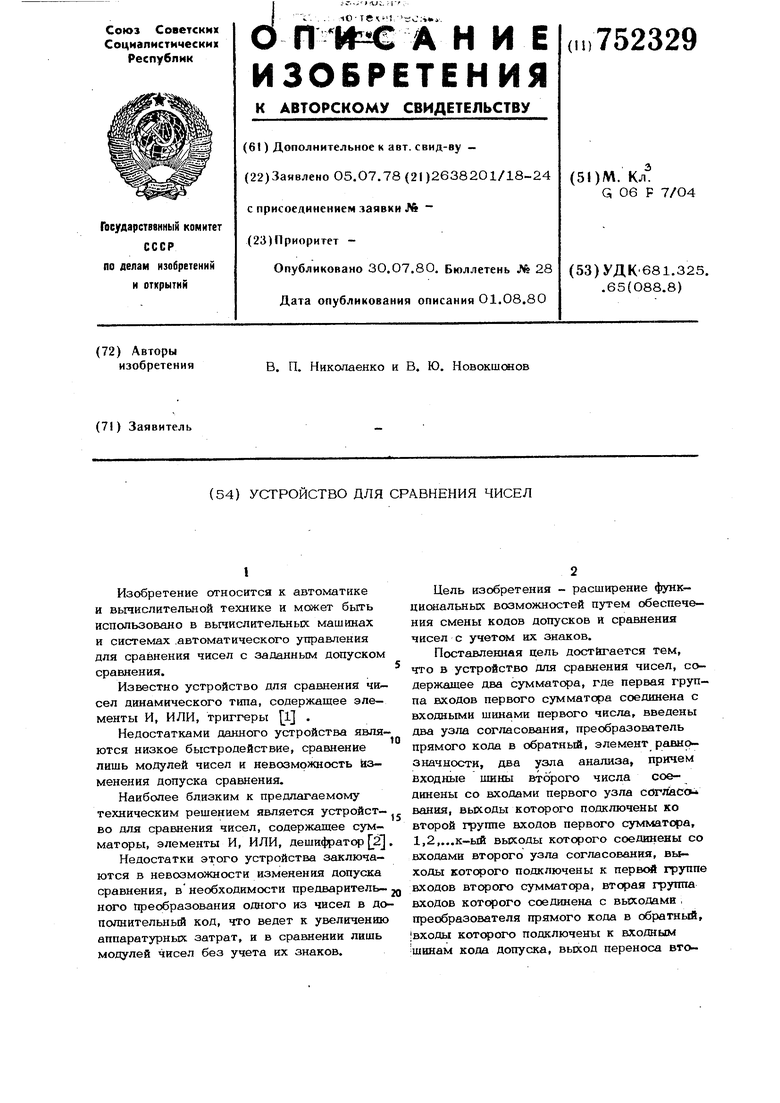

На фиг, 1 изображена блокгч:хема устройства для сравнения чисел; на фиг. 2 функциональная схема узла анализа;: на фиг. 3 - функциональная схема узла сог-, ласования.

Устройство содержит сумматоры 1 и 2, узел 3 согласования, элемент 4 равнозначности, преобразователь 5 прямого кода в обратный, узел 6 согласования, узлы 7,8 анализа.

Узел 7 анализа состоит из элемента

9запрета, элемента 10 ИЛИ-НЕ, элемента 11 ИЛИ.

Узел 8 анализа состоит из элемента 12 запрета, элементов 13, 14 ИЛИ-НЕ, элемента 15 ИЛИ.

Узлы 3,6 согласования содержат в каждом разряде элемент 16 ИЛИ, элементы 17,18 запрета.

Устройство работает следующим образом.

При поступлении чисел А и В с разными знаками элемент 4 равнозначности формирует сигнал, по которому на знако- вьй вход сумматора 1 через элемент 18 запрета и элемент 16 ИЛИ узла 3 согласования поступает прямой код числа А, причем на знаковый вход подается нулевой сигнал. Сумматор 1 на выходах формирует прямой двоичный код суммы (А)4-(В), равный в данном случае (А-В), а с выхода переноса снимается нулевой сигнал. Если -t- О , т.е. если (A-B)D, то на выходах сумматора 1 вырабатываются i нулевые сигналы, поступающие на элемент

10ИЛИ-НЕ узла 7 анализа. По сигналу на знаковом входе узла элементы 18 запрета и элементы 16 ИЛИ узла 6 согласования передают на входы сумматора

2 код, равный в данном случае прямому коду младших разрядов (А-В), т.е. С(А-В). Так как , то С , т.е С + ( -D )- 2t и сумматф 2 не формирует сигнал переноса. В этом случае элементы Ю ИЛИ-НЕ и 11 ИЛИ вырабатьшают сигнал А B+D, запрещая тем самым формирование узлом 8 анализа сигнала +V .

Если при сравнении чисел с разными знаками AfB , т.е. если(А-В)0 , то в зависимости от величины неравенства,

либо на выхо/цах 6 -i - S , 5зн сумматора 1 формируются неоднозначные сигналы, либо узел 6 согласования вырабатывает код С больше кода I . В noci лёднем .случае С D 1, т.е. С + ( 1 -О ) - 2, и сумматор 2 фс мирует сигнал переноса.

Таким образом, на элементы 9 запрета и элемент 10 ИЛИ-НЕ узла 7 ана- лиэа поступают неоднозначные сигналы и элемент 11 ИЛИ вьфабатьшает .сигнал А. В +D, разрешая формирование узлом 8 анализа сигналов +D и -D. Если положительным является число В, т элементы 13 ИЛИ-НЕ и 15 ИЛИ узла 8 анализа вырабатывают сигнал А-сВ -D , запрещая формирование сигнала +D. Если положительным является число А, то элемент 15 ИЛИ дает разрешение элементу 14 ИЛИ-НЕ на формирование сигнала А B + D. При сравнении однозначных чисел А и В по сигналу с элемента 4 равнозначности на входы сумматора 1 через элементы 17 запрета 16 ИЛИ узла 3 согласования кода поступает обратньй код числа А равньй (2 -1 - (А), причем на знаковы вход подается единичный сигнал. На выхо дах сумматора 1 формируется код суммы ( 1 - (А) + (В) + 2) ((А-В)+2)Если (А)5:(В), т.е. если ((А-В) + +2 ) 2 , то сумматор 1 не формирует сигнал переноса Р , со знакового выхода сумматора 1 снимается единишый сигнал, а на выходах 5 -5 вьфабатывается код (2 -1-(А-В), равньй обратному коду разности ). В случае равенства чисел А и В в пре делах допуска D на входы элемента 9 запрета узла 7 анализа с выходов 5ц, .- , S -2,, поступают единичны сигналы. С вьрсодов Q - Ъ сумматора 1 через элементы 17 И и 16 ИЛИ схемы 6 согласования кода поступает код С(А-В). Так как C-i О , то сумматор 2 не формирует сигнал переноса, и элементы 9 запрета и 11 ИЛИ узла 7 анализа вырабатьшают сигнал +D. В случае неравенства чисел А и В в пределах допуска на элементы 9 запрета и 1О ИЛИ-НЕ узла 7 анализа поступают неоднозначные сигналы и элемент 11 ИЛИ вырабатывает сигнал А В +D. Если числа А и В положительные, то элементы 14 ИЛИ-НЕ узла 8 анализа формирует сигнал +D. Если числа А и В отрицательные, то элементы 13 ИЛИ-НЕ и 15 ИЛИ узла 8 анализа вырабатывают сигнал -D. Если при сравнении однозначных чисел (А) (В), т.е. если ( - (А-В)+2) ТО сумматор 1 формирует сигнал переноса СО знакового выхода снимается нулевой сигнал, а на вьссодах 9j--5fi Ьырабатываетс код (). 7 296 При равенстве чисел А н В в пределах допуска на входы элемента 10 ИЛИ-, НЕ узла 7 анализа с выходов Kii- ан сумматора 1 поступают нулевые сигналы. С выходов S - SKсумматора 1 через элементы 18 запрета и 16 ИЛИ узла 6 согласования кода поступает код С, равный в данном случае (). Сумматор 2 производит сложение кода С, обратного кода D и единицы переноса () + +()+1 |A-B(f2-D-l и т.к. , то сумматор 2 сигнал переноса не формирует, а элементы 10 ИЛИ-НЕ и 11 ИЛИ узла 7 анализа вырабатывают сигнал +D. При неравенстве чисел А и В в преде- лах допуска в узел 7 анализа поступают неоднозначные сигналы и элемент 11 ИЛИ этого узла вьфабатьшает сигнал А 1 В +1) . Если при этом числа А и В положительные, то элементы 12 запрета и 15 ИЛИ формируют сигнал А В -D,a если отрицательные, то с выхода элемента 14 ИЛИ-НЕ узла 8 анализа снимается сигнал + D. Применение предлагаемого устройства позволяет сократить оборудование, а сравнение чисел с учетом их знаков приводит к расширению области применения устройства. Управление кодом допуска также приводит к расширеншо функциональньк возможностей устройства и позволяет использовать одно устройство вместо набора устройств для каждого допуска. Формула изобретения 1. Устройство для сравнения чисел, содержащее два сумматора, первая группа входов первсго сумматора соединена с входными шинами первого числа, о т л и - чающее ся тем, что, с целью расширения функциональных возможностей за счет обеспечения смены кодов допусков и сравнения чисел с учетом их знаков, в устройство введены два узла согласования, преобразователь прямого кода, в обратный элемент, равнозначности, два узла анализа, причем входные шины второго числа соедютены со входами первого узла сагласования, выходы которого подключены ко второй группе входов первого сумматора, 1,2,... к-ый выходы которого соединены со входами второго узла согласования, выходы которого подключены к первой группе входов второго сумматора.

вторая группа входов соедишена с BbtsoAaMH преобразователя прямого кода в обратный , входы которого подключены к ВХО1ЩЫМ шинам кода допуска, выход переноса второго сумматора соединен с управл5ающим входом первого узла анализа, входные шины знаковых разрядов чисел подключены ко входам элемента равнозначности, выход которого соединен со знаковым входом первого сумматора и со входом управления первого узла согласования, (к+1)} {к+2)... п -ый выходы первого сумматора, где П - число разрядов сравниваемьк чисел, подключены к 1,2,.,, ()-.му входам первого узла анализа соответственно, знаковый выход первого сумматора соединен со знаковым входом первого узла анализа и со входом утфавления второго узла согласования, выход переноса первого сумматора подключен к первому входу второго узла анализа и ко вх.оцу переносов второго сумматора, первый выход первого узла анализа соединен со вторым входом второго узла анализа, входная шина знакового разряда первого числа подключена к третьему входу вторагю узла анализа.

2. Устройство по п. 1, отличающее с я тем, что в нем первый узел анализа содержит элемент запрета, эле- мент ИЛИ-НЕ и элемент ИЛИ, причем 1,2,... (п -к)-ый входы узла анализа соединены с 1,2,... (п-) информационными входами элемента запрета и 1,2„..(п-к) входами элемента ИЛИ-НЕ, знаковый вход узла анализа подключен к (п-к+1)-ому информационному входу элемента запрета

и (п-к+1)-ому входу элемента ИЛИ-НЕ, (п-к+2)-ый вход элемента ИЛИ-НЕ и управляющий вход элемента защэета соединены с управляющим входом узла анализа, выходы элемента ИЛИ-НЕ и элемента запрета подключены ко входам элемента ИЛИ, прямой выход которого соединен с первым выходом узла анализа, а инверсный - со вторым вькодом узла анализа. 3. Устройство по п. 1, отличающееся тем, что в нем второй узел анализа содержит элемент запрета, элементы ИЛИ-НЕ, ИЛИ, причем первый вход узла анализа соединен с первым информационным входом элемента запрета и с первым входом первого элемента ИЛИ-НЕ, вькод которого подключен к первому входу элемента ИЛИ, второй вход узла анализа соединен со входами управления элеjMeHTa запрета, со вторым входом первого элемента ИЛИ-НЕ и с первым входом второго элемента ИЛИ-НЕ, второй вход которого подключен к выходу элемента ИЛИ, третий вход узла анализа соединен со вторым инфс мационным входом элемента запрета и с третьим входом первого элемента ИЛИ-НЕ.

Источники информации, принятью во внимание при экспертизе

1.Авторское свидетельство СССР № 543936, кл. G 06 F 7/04, 30.05.77.

2.Гаврилов Ю. В., Пучко А. И, Ари(} метическне устройства быстродействующих ЦВМ; М., Сов. радио, 197О, с. 253257 (прототип).

tt

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU877522A1 |

| Устройство для суммирования двоичных чисел | 1982 |

|

SU1022153A1 |

| Устройство для сравнительного анализа п чисел | 1978 |

|

SU736090A1 |

| Устройство для выравнивания порядков чисел | 1982 |

|

SU1030798A1 |

| Устройство для сравнения двоичных чисел | 1980 |

|

SU951294A1 |

| Устройство для сравнения двоичных чисел | 1980 |

|

SU943706A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-05—Подача