Изобретение относится к цифровой вычислительной технике и может применяться в составе арифметических устройств цифровых вычислительнь1х машин при вычислении элементарных функций. Известны устройства, реализующие операцию псевдоделения при вычисле. НИИ функции Z arctg (У/Х) и содержащие регистры, сумматоры и узел сдвига временем реализации операции псевдоделения пропорционально п t , где f - задержка на одноразрядном сумматоре ина элементе типа И-ИЛИ. Сложность реализации таких устройств пропорциональна п 1 и 2. Известные устройства обладают ограниченным быстродействием. Н-аиболее близким по технической сущности к предлагаемому изобретению является устройство, содержащее первый и второй регистры,- первый и второй сумматоры, первый узел сдвига причем выходы первого регистра подключены к входам узла сдвига, и к пе вым входам первого сумматора,выходы сумм которого подключены со сдвигом влево на один разряд к входам перво регистра,выходы второго регистра подключены к вторым входам первого сумматора и к первым входам второго сумматора, выходы сумм-которого под ключены к входам второго регистра, выходы узла сдвига подключены к вторым входам второго сумматора 2. Данное устройство выполняет операцию псевдоделения путем реализации рекуррентного соотношения. A-...2lArl ; i . где AO Y, 80 X, i 0, f, 2, .. /n-l J .1g,.e{.l,.l3, . Устройство работает циклически. Число исполняемых.итераций пропорционально п и на каждой итерации необходимо выполнить операцию сложения (вьзчитания) с распространением переносов на п разрядов для определения псевдочастотного , определякндего операцию сложения и вычитания, которую ; необходимо выполнить на следующей итерации. Время реализации операции псевдоделения устройства пропорционально п , что ограничивает его |.ббк: тррдейс ТВ ие.

Цельизобретения - увеличение быстродействия устройства псевдоделения.

Поставленная цель достиг.ается тем, .что в устройство псевдоделения, содержащее первый и второй регистры, первый и второй сумматоры, первый узел сдвига, причем выход первого регистра подключен к входу первого узла сдвига и к первому входу первого сумматора, выход суммы которого подключен к входу первого регистрд., выход второго регистра подключен ко второму входу первого сумматора и к первому входу второго сумматора, выход суммы которого подключен к входу второго регистра, выход первого узла сдвига подключен ко второму входу второго сумматора, введены третий и четвертый регистры, второй узел сдвига и третий сумматор,причем выход третьего регистра подключен к входу второго узла сдвига и к третьему входу первого сумматора, выход переносов которого подключен к входу третьего регистра, выход четвертого регистра подключен к четвертому входу первого сумматора и к третьему входу второго сумматора, выход переносов которого подключен к входу четЬертого регистра, выход второго узла сдвига подключен к четвертому входу BTOpo.ro сумматора, выход суммы старших разрядов первого сумматора подключен к первому входу третьего сумматора, а выход переносов старших разрядов первого сумматора - к второму входу третьего сумматора.

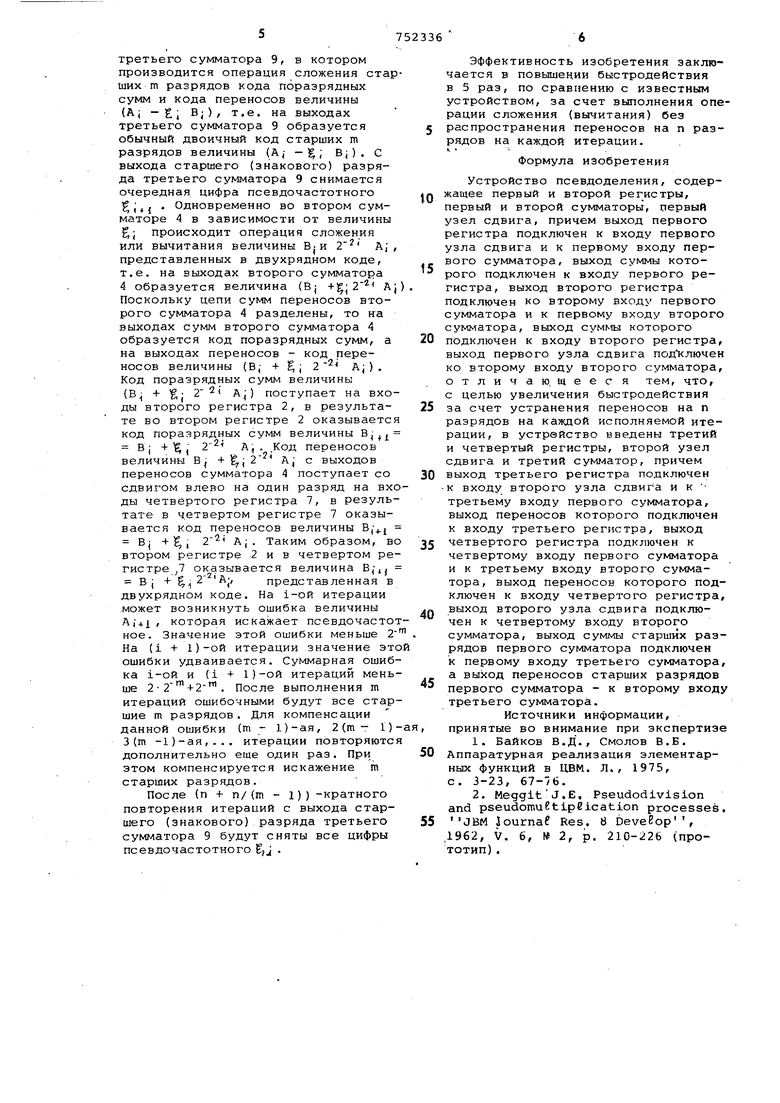

На чертеже показана структурная схема устройства псевдоделения.

Устройство псевдоделения содержит первый регистр 1, второй регистр 2, первый сумматор 3, второй ciMMaTop 4, первый узел 5 сдвига, третий регистр 6, четвертый регистр 7, второй узел 8 сдвига, третий сумматор 9 с параллельным переносом.

Устройство выполняет операцию псевдоделения путем реализации рекуррентного соотношения .

.БЛ

Bj4i

( signl|- signA, где 1 0,1,2,...г.

,.,,тг 4,т- 3, т- 2,т- 2 ,т-I ,га, ...,2т- 6, 2 т- 5, 2т- 4,2т- 4, 2 m - 3, 2т - 2, ..., ...,3т- 8,3т- 7, Зт-6, 3 m - б, 3 m - 5, 3 ш - 4 ... , п-3, п-2,п-1, п-1;

.. . f SP Х,;..+ 1}Д 4.1,

АО Y, m - количество разрядов третьего сумматора 9, меньшее разрядности устройства.

Устройство работает Циклически. Первый регистр 1 работает одновременно с третьим регистром б, второй регистр 2-е четвертым регистром 7, первый узел 5 сдвига со вторым узлом 8 сдвига. На i-ой итерации, код поразрядных сумм величины А с выходов первого регистра 1 поступает на входы первого узла 5 сдвига и на первые входы первого суматора 3, код переносов величины А.; с выходов третьего регистра 6 - на входы второго узла 8 сдвига и на третьи входы первого сумматора 3. Код поразрядных сумм величины В; с выходов второго регистра 2 поступает на вторые входы первого сумматора 3 и на первые входы второго .сумматора 4, код переносов величины -Bj с выходов четвертого регистра 7 на четвертые входы первого сумматора 3 и на третьи входы второго сумматора 4. В первом узле 5 сдвига происходит сдвиг кода поразрядных сумм величины AJ на 2j разрядов вправо, в результате на его выходах образуется код поразрядных сумм величины AJ , который поступает на вторые входы второго сумматора 4. Во втором узле 8 сдвига происходит сдвиг кода переносов величины AJ, поступившего на его входы, на 2 разрядов вправо, в результате на его выходах образуется код переносов величины AJ, который .поступает на четвертые входы второго сумматора 4. В первом сумматоре 3 в зависимости от значения величины j происходит операция сложения или вычитания величины А и величины В; , представленных в двухрядном коде, и на его выходах образуется величина (Aj Bj ) . Поскольку цепи сумм и переносов первого сумматора 3 разделены, то на выходах сумм;первого сумматора 3 образуется код поразрядных сумм величины (А; - , В,-) , а на выходах

переносов вели переносов - код чины (А j - , 4

В.).

Код поразрядных сумм величины (Aj - , В;) поступает со СДВИГОМ влево на один разряд на входы первого регистра 1, в результате в первом регистре 1 оказывается код поразрядных сумм величины , 2(А,- -, ). Код переносов величины (Ai -, В;) поступает со сдвигом влево на два разряда на входы третьего регистра 6, в результате в третьем регистре 6 оказывается код переносов величины А ,4 i 2 (А; - В). Старшие m разрядов кода поразрядных сумм величины (Aj В) с выходов сум старших m разрядов первого сумматора 3 поступают на первые входы третьего сумматора 9. Старшие m разрядов кода переносов величины (Aj - Bj) с выходов переносов старших m разрядов первого суммаiTOpa 3 поступают со, сдвигом, влево :на один разряд на вторые входы третьего сумматора 9, в котором производится операция сложения стар ших m разрядов кода поразрядных сумм и кода переносов величины (Aj В;), т.е. на выходах третьего сумматора 9 образуется обычный двоичный код старших m разрядов величины (А,- - ; В ) . С выхода старшего (знакового) разряда третьего сумматора 9 снимается очередная цифра псевдочастотного . Одновременно во втором сумматоре 4 в зависимости от величины g; происходит операция сложения или вычитания величины Bjи А; представленных в двухрядном коде, т.е. на выходах второго сумматора 4 образуется величина (Bj 2 A Поскольку цепи сумм переносов второго сумматора 4 разделены, то на выходах сумм второго сумматора 4 образуется код поразрядных сумм, а на выходах переносов - код переносов величины (В,- + j AJ ) . Код поразрядных сумм величины (Bj + - 2 Aj) поступает на вхо ды второго регистра 2, в результате во втором регистре 2 оказываетс код поразрядных сумм величины B,j, Bj +, А,. .Код переносов величины BJ + i 2 Aj с выходов переносов сумматора 4 поступает со сдвигом влево на один разряд на вх ды четвертого регистра 7, в резуль тате в четвертом регистре 7 оказывается код переносов величины . Bj +. 2j. Таким образом, в втором регистре 2 и в четвертом ре гистре 7 оказывается величина В,) В; + 2 Aj, представленная в двухрядном коде. На 1-ой итерации .может возникнуть ошибка величины А; + 1 , котс5рая искажает псевдочасто ное. Значение этой ошибки меньше 2 На (i + 1)-ой итерации значение эт ошибки удваивается. Суммарная ошиб ка i-ой и (1 + 1)-ой итераций мень ше . После выполнения m итераций ошибочными будут все стар шие m разрядов. Для компенсации данной ошибки (т - 1)-ая, 2(т - 1) 3(т -1)-ая,... итерации повторяютс дополнительно еще один раз. При этом компенсируется искажение m старших разрядов. После (п + n/(m - 1))-кратного повторения итераций с выхода старшего (знакового) разряда третьего сумматора 9 будут сняты все цифры псевдочастотного ,J . Эффективность изобретения заключается в повышении быстродействия в 5 раз, по сравнению с известным устройством, за счет выполнения операции сложения (вычитания) без распространения переносов на п разрядов на каждой итерации. к Формула изобретения Устройство псевдоделения, содержащее первый и второй регистры, первый и второй сумматоры, первый узел сдвига, причем выход первого регистра подключен к входу первого узла сдвига и к первому входу первого сумматора, выход суммы которого подключен к входу первого регистра, выход второго регистра подключен ко второму входу первого сумматора и к первому входу второго сумматора, выход суммы которого подключен к входу второго регистра, выход первого узла сдвига подключен ко второму входу второго сумматора, отличаю, щеес я тем, что, с целью увеличения быстродействия за счет устранения переносов на п разрядов на калщой исполняемой итерации, в устрейство введены третий и четвертый регистры, второй узел сдвига и третий сумматор, причем выход третьего регистра подключен к входу второго узла Сдвига и к третьему входу первого сумматора, выход переносов которого подключен к входу третьего регистра, выход четвертого регистра подключен к четвертому входу первого сумматора и к третьему входу второго сумматора, выход переносов которого подключен к входу четвертого регистра, выход второго узла сдвига подключен к четвертому входу второго сумматора, выход суммы старших разрядов первого сумматора подключен к первому входу третьего сумматора, а выход переносов старших разрядов первого сумматора - к второму входу третьего сумматора. Источники информации, принятые во внимание при экспертизе 1.Вайков В.Д., Смолов В.Б. Аппаратурная реализация элементарных функций в ЦВМ. Л., 1975, с. 3-23, 67-76. 2.MeggitJ.Ё, Pseudodivision and pseudomuEtipBication processes. JBM Journaf Res, 8 DeveEop, ,1962, V. 6, № 2, p. 210-226 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство псевдоделения | 1978 |

|

SU752337A1 |

| Устройство псевдоделения | 1978 |

|

SU742931A1 |

| Арифметическое устройство | 1978 |

|

SU763894A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Устройство для вычисления значения полинома -ой степени | 1978 |

|

SU744559A2 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Узловой процессор | 1986 |

|

SU1399763A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-31—Подача