I

Изобретение относится к цифровой Bbtчиспительной технике и может применяться в составе арифметических устройств цифровых вычислительных машин при вычислении элементарных (})ункций.

Известны устройства псевпоцепения, pe-iапизукщие операцию псевподеления при вычислении функций

y-Cogx, , v W CiJ.

Недостатком тшсих устройств является низкое быстроде аствие.

Наиболее бли.зким техническим решением к изобретению .является устройство, содержещее регистр, блок сдвига, блок ум-5 ноже НИИ, суммапгор и блок постоянной памяти, причем выходы регистра подключены ко входам блока сдвига, выходы которого подключены ко в.ходам блока умнож&ния, выходы старших разрядов регистра подключены ко входам блока постоянной памяти. Данное устройство псевдоделения выполняет преобразоваЕше

х.п(1.,г--)1 ,,

лутем реализации рекуррентного соотношения,

t.j .RLa- (2.)

с законом отбора

g.,если (3)

,

если ,

10

Где RJ, - частичный остаток операции псевдоделения на t-o{t итерации;

J. - значение левого сдвига на L-ой итерации.

Значение левого сдвига лежит менаду О и (), где величина tn- число старших разрядов регистра, к которым подключен блок постоянной памяти. После

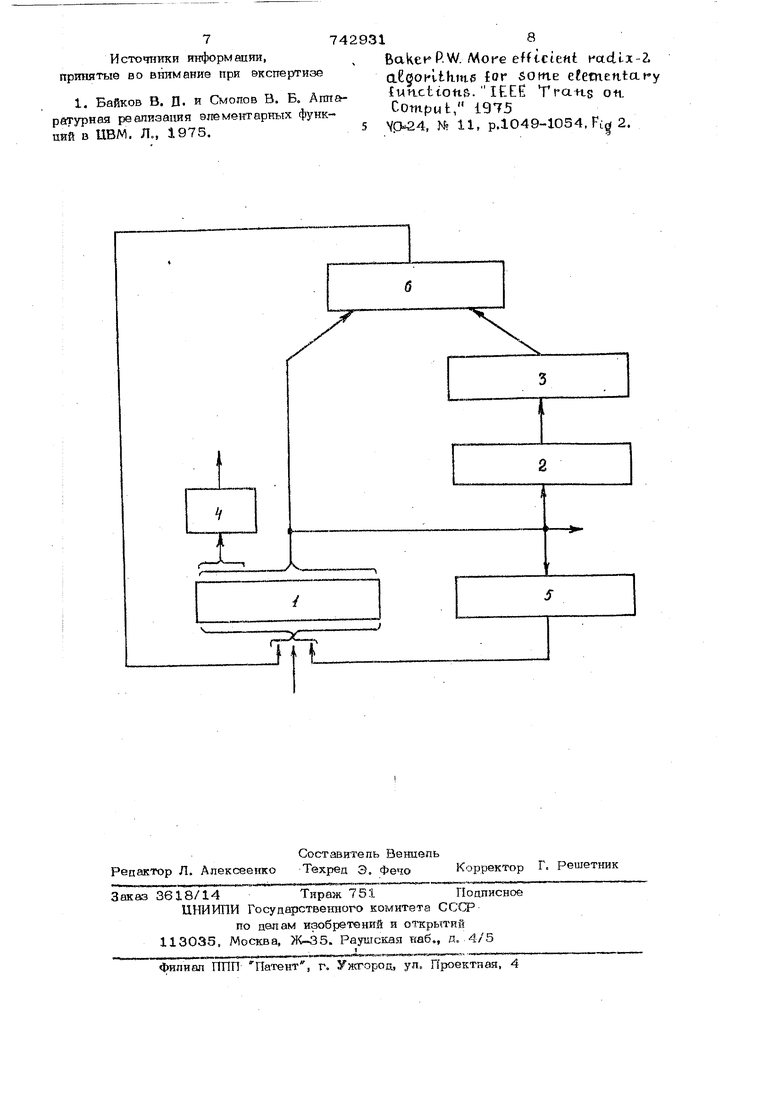

L -ой итерации в регистре находится частичный остаток R- . Блок постоянной памяти анализирует старшие Щ. разрядов Ut и определяет по хранящейся в век соответствующую величину левого Сдвига J о Таким образом, за оцщ итерацию происходит формирование частичного остатка операции псевподеления HI 4. , определение величины , а вешчггаы О где г U i, Ui-, U- 3,14-4, ,;,. ;} -1 т.е. итерации ((,+ 1)ая, (t-f2)-3, .,., {1™1)-я пропускаются. Be личина i i заЙис-нт от значения цифр т. старших раа Ьядов частичнотх) остатка R{. Число Е|ьтолняемых итераций пропорционально и на каждой итерац 1И выполняется операция сЬпожеютя с распространением переносов на TV. разрядов L2J , Однако известное устройство псевдоце™ Ленин обладает ограниченным быстродейст Цель изобретения - увеличение быстро действия устройства псевдоделения. Поставленная цель достигается тем, ч В устройство псевдоделения, содержащее регистр, блок Сдвига, блок умножения, су мшор, блок постоянной памяти, причем в ходы регисгра подключены ко входам бло ка Сдвига, вькоды которого подключены :ВХодам блока умножения, выходы старших разрядов регистра подключены ко входам блока постоянной памяти, дополнительно введен псевдосумматор, работающий в двухрядном коде, при этом выходы регис ра и блока умножения подключены ко вхо дам псевдосумматора, выходы которого Лодключены ко входам регистра, вьосоды которотю подключены ко входам суммато ра, выходы KOTopoi o подключены ко вхо дам регистра. И а черте нее показана структурная схема устройства псевдоделенияо Устройство содержит регистр 1, блок 2 сдвига 3 умножения, блок 4 постоянной памяти,.сумматор 5, псевдосумматор 6, работающий в двухрядном коде„ Пришлип действия предлагаемого устройства п(зевдоделения основан на исполь зовании того факта, что при выполнении операции псевдодвпения после выполнешм итераций в старших разрядах частично го остатка операции псевдоделения R t имеется не менее . единиц, Преплетаемов устройство псевдоделеяйя выполняет преобразование хп )- (4) утем реализации рекуррентного соотиЭ-1енияRui--- ;2-(. - L(5) де Rj частичный остаток операции севподеления на t итерации, Rrx,6ie(-i,o,-t-iV « ры псевдочастотного, i- -1,2,..„п- Преобразование ведется в несколько этапов. 1., Аргумент X подается в регистр 1, т.е, R «X. Блок 4 постоянной памяти, подкпюче1шый к, Ш, старшим разрядак регисгра 1. анализирует старшие-Нгразрядов j.j и выдает набор значений ,,0,i}, ,1,,, -п. для вьтолнения итераций первого этагца. Поскольку этот набор значений S{,, 1,2...гт1 определен до качана итерш-шонного-процеоса, то на каждой вьтолвяемой итерации первого этапа операцшо сложения (вычитания) выполняют в двухрядном коде, т.е. без распространения переносов на Vt. раэрядов, кото1эое выполняется лишь в конце этапа для преобразования частичного остатка R 1 . t двухрядного кода в обычный двоичнъгй код. Ускоренная реализация выражения (5) для L ,2,,..П1 происходит по следующей основной процедуре: 0)начало с-ой итерации; 1)если1 | р, то переход к п, 6, иначе переход к п. 2; 2)R,передается из регистра 1 в блок Сдвига 2, где происходит сдвиг на I разрядов вправо, на выходе, блока сдвига 2 получается результат 2 RL ; 3)2. R { с выходов блока сдвига 2 передается в блок 3 умножения на -1, -fl, где происходит умножение 2. R на-1, есгш -- 1 и на+1, если , т,е„ на выхода блока 3 умножения на -1, .-1 получается результат 4) ,2/- 1(1 перелается из блока 3 4-1 в псевдосумматор 6, (.ения на 1, R i. 1тередается .из регистра 1 в псевдосумматор 6; где происходит операция слонсения в двухрядном коде, т.е. без распространения переносов, на выходе псевдосумматора б образуется результат R -f -(- 2 : представленный в двухрядном коде 5) . R перепается из псевдосумматора 6 в регистр 1, т.е. в регистре 3. оказывается очередной частичный остаток ,, представленный в пвухряциом коде; 6) конец L-ой итерации, Поспе иг-кратного повторения основн процедуры частичный остаток операции псевдоделения R.,, полученны после т. -ой итерации в двухрядном ко на регистре 1, передштся из регистра в сумматор 5, где происходит распростр нение переносов на п. разрядов, т.е. на выходе сумматора 5 оказывается части ный остаток операции псевдоделения Р п авленный в обычном одн рядном двоичном коде передае ся из сумматора 5 в регистр 1. Частичный остаток R ш ± обозначенный / менее нединиц в стагрших содержит не разрядах. If. Наличие гпединиц в старших разря R позволяет до начала итерационного процесса определить J для I - irn igrrt, С выходов +1)-го, (mt-2}--ro,.J, 2тм.-го разрядов регистра 1 снимаются значения 61 с законом отбора Сг если г; - i - цифра разряда частичн го остатка В начале второго этапа выполняется Одна подготовительная итерация Яц R ц +- Z R по пп. 2 ; 6 00новной процедуры первого этапа. Здесь начальный частичный остаток оп рации псевдоделения на втором этапе, представленный в двухрядном коде в регистре 1. Затем выполняются итерации по осно ной процедуре первого этапа, по которой происходит ускоренная реализация выражения (5) для L m+±,ni+Z,.,,m- В результате в регистре 1 оказывается частичный остаток R , представленный в ZTH двухрядном коде. В конце второго этапа вьшолняется одна заключительная итерация RK - ° ™1 основной процеду)ры первого этапа. Здесь R - конечный частичный остаток операции псевдоделения на втором этапе, представленный в двухрядном коде в регистре 1. R1 передается из регистра 1 в суммеггор-5. В сумматоре 5 происходит распространение переносов на п. разрядов, т.е. на выходе сумматора 5 оказывается частичный остаток операции поевдоделения R представленный в обычном однорядном двоичном копе, R. ( 316 передается из сумматора 5 в -регистр .1. На этом второй этап .закончиваотся. В частичном остатке R | ик еется не менее 2т-i единиц в старших разрядах. Выполнение третьего этапа аналогично вьшолненшо второго этапа. Наличие тя единил в старших разрядах R позволяет до начала итерационного процесса определить fj для1--г.тп,2.т 1 .... 2(2пг-1), что дает в стерших р 1зрядах частичного остаткаН не менее 2()-l единиц. Выполнение остальных этапов ПНОЛОГЕГЧНО рассмотренным. Вычисления прекращаются, как только номер итерации L достигает величшгы tV2-fl. При этом в частичном остатке операции псевдоделения в регистре 1 в п/2 старших разрядах находятся единкшшы. Значения , для 1 7-1/г 1,п.....1г снимаются с выходов (n/2+l )-го, ( -го, ..., п. -го разрядов регистра 1 с коном отбора . f - /О, ее, -(- 1 L-l,ec i, где Г - цифра и-го разряда частичного остатка после прекращения: вычислений. Кроме того, П/2.Е +1. Эффективность изобретения заключается в увеличении быстродействия устройст ва за счет реализации операции слохлэния (вычитания) с распространением переносов на tl разрядов лишь на однрй-четырех итерациях и реализации операции сложения без распрострал:ения переносов на ТТраэрядов на всех остальных выполняемых Еггерациях. Формула изобретения Устройство псевдоделения, соцерх ашее регистр, блок сдвига, блок умнохения, сумматор, блок постоянной памяти, причем выходы регистра подключены ко входам блока сдвига, вькоды которого подключены ко входам бока умноядания, выходы старШ1ГХ разрядов регистра подключены ко входам блока постоянной памяти, о т л и ч вющее ся тем, что, с целью увеличения быстродействия, в него введен псевосумматор работающий в двухрядном кое при этом выходы регистра и блока уможения подключены ко входам псевдосуматора, выходы которого подключены ко ходам регистра, выходы которого подклюены ко входам сумматора, выходы котороо подключены ко входам регистра 74 Истотаики информации, пртютые во внимание при вкспертиае 1. Байков В. П. и Смолов В. Б. Аппаратурная реализация эпементарных функв ЦВМ. Л., 1975. а .W. More efficient adU-Z а6§окиКтб for SOME e ementaf-y ft4ncttotis. IEEE Traus on Comput, 1975 , N 11, p.l049-1054,F{g 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU763894A1 |

| Устройство псевдоделения | 1978 |

|

SU752337A1 |

| Устройство псевдоделения | 1978 |

|

SU752336A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

Авторы

Даты

1980-06-25—Публикация

1978-04-03—Подача