00

со со о оо

Изобретение относится к вычислительной технике и предназначено для решения сеточных уравнений, к которым приводятся уравнения с частными про- изводными второго порядка.

Цель изобретения - увеличение быстродействия .

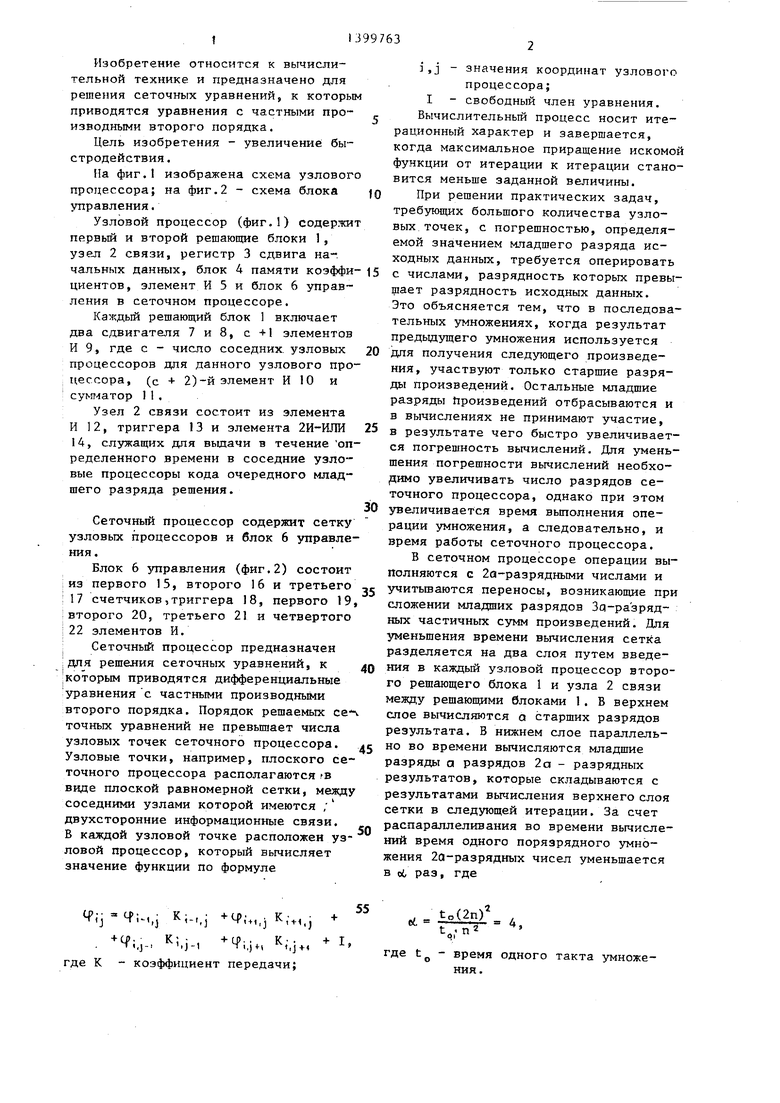

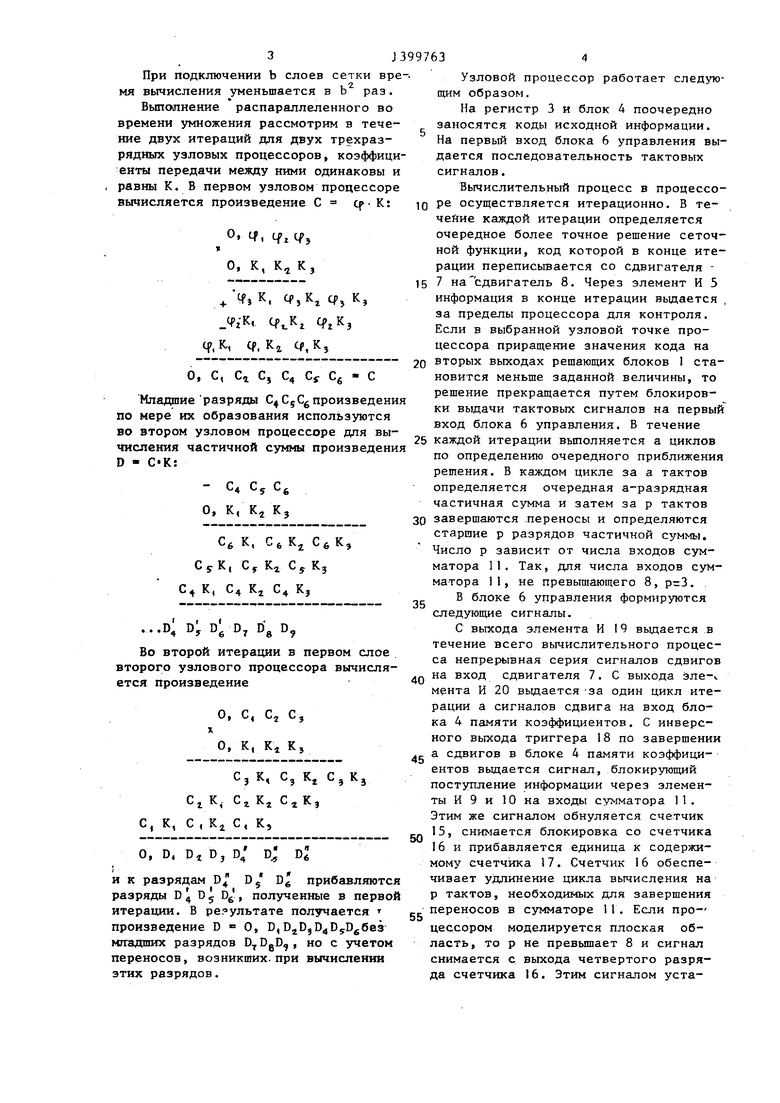

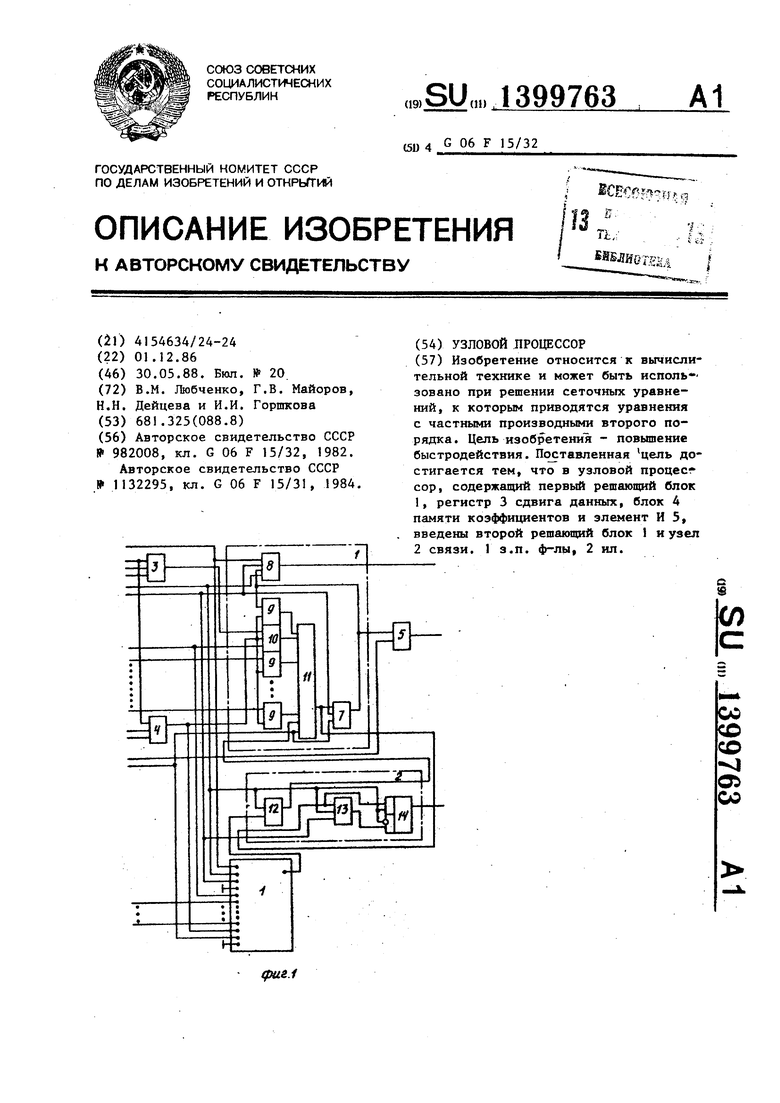

Па фиг.1 изображена схема узлового процессора; на фиг.2 - схема блока управления.

Узловой процессор (фиг.1) содержит первый и второй решающие блоки 1, узел 2 связи, регистр 3 сдвига начальных данных, блок 4 памяти коэффи- циентов, элемент И 5 и блок 6 управления в сеточном процессоре.

Каждый решающий блок 1 включает два сдвигателя 7 и 8, с +1 элементов И 9, где с - число соседних, узловых процессоров дпя данного узлового процессора, (с + 2)-и элемент И 10 и сумматор 11.

Узел 2 связи состоит из элемента И 12, триггера 13 и элемента 2И-ИЛИ 14, служащих для вьщачи в течение определенного времени в соседние узловые процессоры кода очередного младшего разряда решения.

Сеточный процессор содержит сетку узловых процессоров и блок 6 управления.

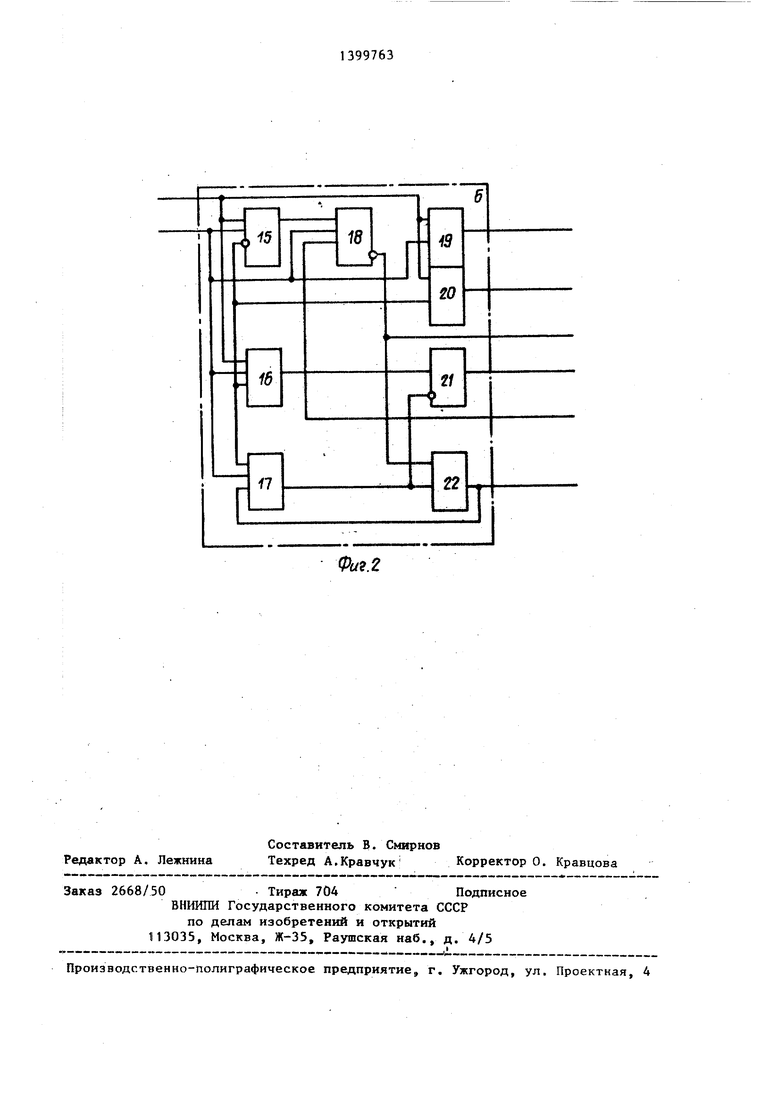

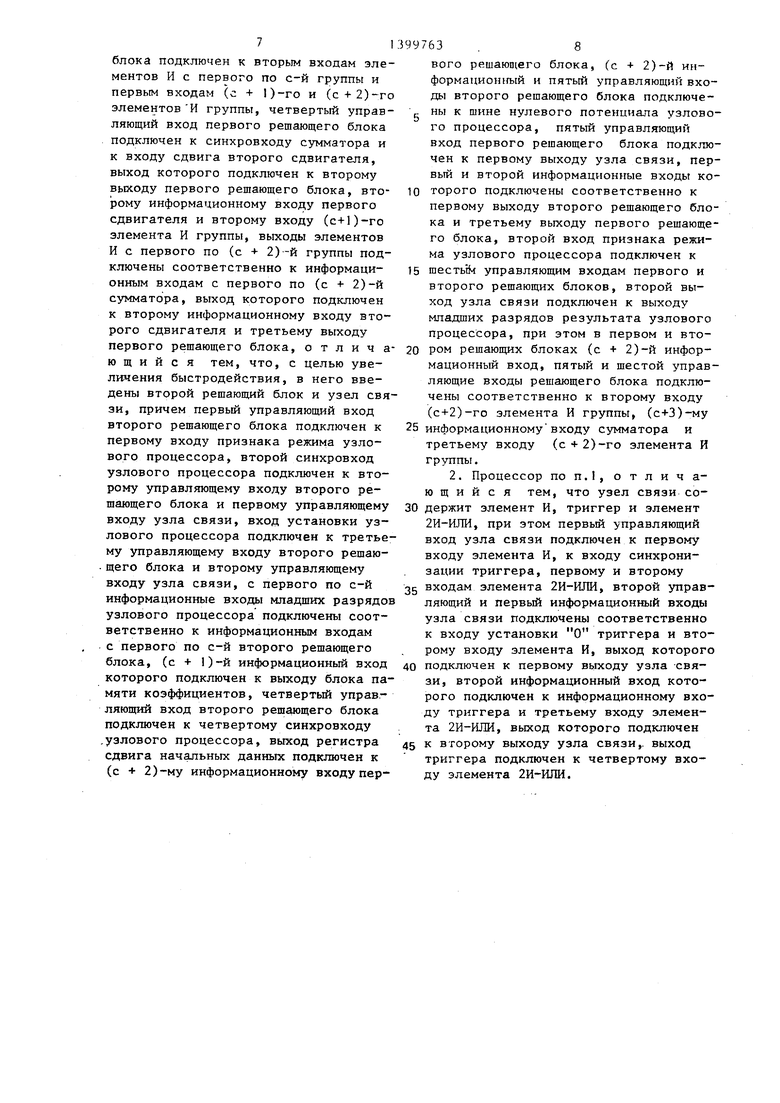

Блок 6 управления (фиг.2) состоит из первого 15, второго 16 и третьего :17 счетчиков,триггера 18, первого 19 ;второго 20, третьего 21 и четвертого I22 элементов И.

: Сеточный процессор предназначен I для решения сеточных уравнений, к Iкоторым приводятся дифференциальные уравнения с частными производными второго порядка. Порядок решаемых ce точных уравнений не превьшает числа узловых точек сеточного процессора. Узловые точки, например, плоского сеточного процессора располагаются fS виде плоской равномерной сетки, между соседними узлами которой имеются ; двухсторонние информационные связи. В каждой узловой точке расположен узловой процессор, который вычисляет значение функции по формуле

jg

5

0

5

0

0 с

0

,j - значения координат узлового

процессора; I - свободный член уравнения.

Вычислительный процесс носит итерационный характер и завершается, когда максимальное приращение искомой функции от итерации к итерации становится меньше заданной величины.

При решении практических задач, требующих большого количества узловых точек, с погрешностью, определяемой значением младшего разряда исходных данных, требуется оперировать с числами, разрядность которых превы- щает разрядность исходных данных. Это объясняется тем, что в последовательных умножениях, когда результат предьщущего умножения используется для получения следующего произведения, участвуют только старшие разряды произведений. Остальные младшие разряды произведений отбрасываются и в вычислениях не принимают участие, в результате чего быстро увеличивается погрешность вычислений. Для уменьшения погрешности вычислений необхо- Р(ИМО увеличивать число разрядов сеточного процессора, однако при этом увеличивается время выполнения операции умножения, а следовательно, и время работы сеточного процессора.

В сеточном процессоре операции выполняются с 2а-разрядными числами и учитъшаются переносы, возникающие при сложении младших разрядов За-разряд- ных частичных сумм произведений. Для уменьшения времени вычисления сетка разделяется на два слоя путем введения в каждый узловой процессор второго решающего блока 1 и узла 2 связи между решаюшдми блоками 1. В верхнем слое вычисляются а старших разрядов результата. В нижнем слое параллельно во времени вычисляются младшие разряды а разрядов 2а - разрядных результатов, которые складываются с результатами вычисления верхнего слоя сетки в следующей итерации. За счет распараллеливания во времени вычислений время одного порязрядного умножения 2а-разрядных чисел уменьшается в oi, раз, где

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Узловой элемент цифровой сетки для решения краевых задач теории поля | 1985 |

|

SU1283788A1 |

| Сеточный микропроцессор | 1978 |

|

SU763904A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

Изобретение относится к вычислительной технике и может быть исполь - зовано при решении сеточных уравнений, к которым приводятся уравнения с частными производными второго порядка. Цель изобретени я - повышение быстродействия. Поставленная цепь достигается тем, что в узловой процесг сор, содержащий первый решающий блок 1, регистр 3 сдвига данных, блок 4 памяти коэффициентов и элемент И 5, введены второй решающий блок 1 и узел 2 связи. 1 з.п. ф-лы 2 ил.

К.

4 ij , K;,j +q,4,,j -,ч,., + 0. К; - +

T .J- iJ-1

где К - коэффициент передачи;

Ч м., K,.j, 4-

d.

to(2n)

4,

где t - время одного такта умножения.

При подключении b слоев сетки мя вычисления уменьшается в b раз.

Выполнение распараллеленного во времени умножения рассмотрим в течение двух итераций для двух трехразрядных узловых процессоров, коэффициенты передачи между ними одинаковы и равны К. В первом узловом процессоре вычисляется произведение С Cf-K:

ifi

«

О, К, K,j к,

вре,К, q.,K д., К, (f,-K, q.K, Cf,K, (f,K, (f, KI g, K,

Oj C( Сц Cj C|| Cf Cg с

Младаие разряды C CjC произведения по мере их образования используются во втором узловом процессоре для вычисления частичной суммы произведения D « С К:

С К. I f 1 9 3 Ъ К 4 2 4 Э

D D.

...D, Dy Dg D, g ..,

Во второй итерации в первом слое второго узлового процессора вычисля- произведение

ется

О, С, С, С,

разряды D D 5 Dg , полученные в первой итерации. В реяультате получается произведение D О, младших разрядов ,, но с учетом переносов, возникших, при вычислении этих разрядов.

.

о ециире :

10

ния я ния

15

е я-

J3997634

ре Узловой процессор работает следующим образом.

На регистр 3 и блок 4 поочередно заносятся коды исходной информации. На первьй вход блока 6 управления выдается последовательность тактовых сигналов.

Вычислительный процесс в процессоре осуществляется итерационно. В те- чейие каждой итерации определяется очередное более точное решение сеточной функции, код которой в конце итерации переписьшается со сдвигателя - 7 на сдвигатель 8. Через элемент И 5 информация в конце итерации выдается , за пределы процессора для контроля. Если в выбранной узловой точке процессора приращение значения кода на

20 вторых выходах решающих блоков 1 становится меньше заданной величины, то решение прекращается путем блокировки выдачи тактовых сигналов на первый вход блока 6 управления. В течение

25 каждой итерации выполняется а циклов по определению очередного приближения решения. В каждом цикле за а тактов определяется очередная а-разрядная частичная сумма и затем за р тактов

30 завершаются .переносы и определяются старшие р разрядов частичной суммы. Число р зависит от числа входов сумматора 11. Так, для числа входов сумматора 11, не превышающего 8, .

В блоке 6 управления формируются следующие сигналы.

С выхода элемента И 19 выдается в течение всего вычислительного процесса непрерывная серия сигналов сдвигов

Q на вход сдвигателя 7. С выхода эле-ч

35

45

50

ой м

55

Мента И 20 выдается за один цикл итерации а сигналов сдвига на вход блока 4 П 1мяти коэффициентов. С инверсного выхода триггера 18 по завершении а сдвигов в блоке 4 памяти коэффициентов вьщается сигнал, блокирующий поступление информации через элементы И 9 и 10 на входы сумматора 11. Этим же сигналом обнуляется счетчик 15, снимается блокировка со счетчика 16 и прибавляется единица к содержимому счетчика 17. Счетчик 16 обеспечивает удлинение цикла вычисления на р тактов, необходимых для завершения переносов в сумматоре П. Если про- моделируется плоская об- р не превышает 8 и сигнал с выхода четвертого разряцессоромласть, то снимается

да счетчика 16. Этим сигналом устаНавливается в О триггер 18, производится сдвиг кода в регистре 3 сдвига начальных данных и через элемент И 21 сдвиг кодов в сдвигателях.8.

По завершении а циклов итерации сигнал с выхода счетчика 17 блокирует 1 аботу элемента И 21 и через элемент И 22 заносит код с выходов сдвигате- ля 7 на сдвигатель 8, а также сбрасывает в О счетчик 17. В элементах И 10 выполняется поразрядное зт ноже- Ние входной информации на соответствующие коэффициенты. В сумматоре 11

Производится сложение получаемых раз- |5 вход установки узлового процессора

произведения, В начале каждого Цикла с первого выхода второго реша- кйцего блока 1 через элемент И 12 уз- Л|а 2 связи на вход сумматора 11 пос- т|упает очередной разряд корректирую- ш|его кода. Кроме того, с выхода сдви- Г|ателя 7 через элемент И 9 на вход с|умматора И поступает поразрядно код Ч|астичной суммы искомого решения, по- Л|ученный за время предьщущих циклов итерации. В процессе вычислений в течение циклов в сдвигателе 7 образуются а младших разрядов искомой функции, а в течение а-го цикла по- тактно формируются старшие а разря- функции. В начале каждого из а-1 п|ервых циклов образующийся младший разряд искомой функции фиксируется на триггере 13 и вьщается через элемент 2И-ИЛИ 14 узла 2 связи на соот- В гтствующий вход второго решающего блока 1 соседних узловых процессоров, во вторьпс решающих блоках 1 вьшолня- ю гся операции с а младшими разрядами

2а .разрядных чисел. Результаты вычис- 40 узлового процессора, второй выход лений искомой функции, полученные на первого решающего блока подключен к

первого и второго ре1, в конце итерации пес;{1вигателях 7 шлющих блоков рфписьгеаются на сдвигатели 8 этих же решающих блоков 1. Код в сдвигателе 8 второго решающего блока 1 в следующий итерации будет использован как кйрректирующий код во время вычислений в первом решающем блоке 1.

второму входу элемента И, при этом первый решающий блок содержит первы и второй сдвигатели, сумматор и гру

45 пу из с + 2 элементов И, причем пер вый и второй управляющие входы перв го решающего блока подключены соответственно к входам записи и сдвига первого сдвигателя, выход которого

Формула из

об

;

р е т е н и я

памяти коэффициентов, вход начальной установки узлового процессора подключен к входам записи регистра сдвига начальных данных и блока памяти коэффициентов , первый синхровход узлового процессора подключен к входу сдвига регистра сдвига начальных данных,первый вход признака режима узлового процессора подключен к первому управляющему входу первого решающего блока, второй синхровход узлового процессора подключен к второму управляющему входу первого решающего блока,

подключен к третьему управляющему . входу первого решающего блока, вход признака выбора узлов узлового про- цессора подключен к первому входу

элемента И, выход которого подключен к выходу старших разрядов результата узлового процессора, с первого по с-й (где с - число соседних узловых процессоров для данного узлового процессора) информационные входы старших разрядов узлового процессора подклю- чены соответственно к информационным .входам с первого по с-й первого решающего блока, третий синхровход узлового процессора подключен к входу считьгоания блока памяти коэффициентов, выход которого подключен к (с + 1)-му информационному входу первого решающего блока, четвертый синхровход узлового процессора подключен к четвертому управляющему вхОду первого решающего блока, первый вьЬсод первого решающего блока подключен к выходу старших разрядов результата

второму входу элемента И, при этом первый решающий блок содержит первый и второй сдвигатели, сумматор и группу из с + 2 элементов И, причем первый и второй управляющие входы первого решающего блока подключены соответственно к входам записи и сдвига первого сдвигателя, выход которого

подключен к первому выходу первого решающего блока, третий управляющий вход первого решающего блока подключен к первым информационным входам первого и второго сдвигателей, с первого по с-й информационные входы первого решающего блока подключены соответственно к первым входам элементов И с первого по с-й группы, (с + 1)-й информационный вход первого решающего

71

блока подключен к вторым входам элементов И с первого по с-й группы и первым входам (с + 1)-го и (с +2)-го элементов И группы, четвертый управляющий вход первого решающего блока подключен к синхровходу сумматора и к входу сдвига второго сдвигателя, выход которого подключен к второму выходу первого решающего блока, вто- рому информационному входу первого сдвигателя и второму входу (с+1)-го элемента И группы, выходы элементов И с первого по (с + 2)-и группы подключены соответственно к информаци- онным входам с первого по (с + 2)-и сумматора, выход которого подключен к второму информационному входу второго сдвигателя и третьему выходу первого решающего блока, о т л и ч а ю щ и и с я тем, что, с целью увеличения быстродействия, в него введены второй решающий блок и узел связи, причем первый управляющий вход второго решающего блока подключен к первому входу признака режима узлового процессора, второй синхровход узлового процессора подключен к второму управляющему входу второго решающего блока и первому управляющему входу узла связи, вход установки узлового процессора подключен к третьему управляющему входу второго решающего блока и второму управляющему

входу узла связи, с первого по с-й

информационные входы младших разрядов узлового процессора подключены соответственно к информационным входам с первого по с-й второго решающего блока, (с + 1)-й информационный вход которого подключен к выходу блока памяти коэффициентов, четвертый управляющий вход второго решающего блока подключен к четвертому синхровходу .узлового процессора, выход регистра сдвига начальных данных подключен к (с + 2)-му информационному входу пер

s 0 5 о

5

0 5

вого решаюп1его блока, (с - 2)-и информационный и пятый управляющий входы второго решающего блока подключены к шине нулевого потенциала узлового процессора, пятый управляющий вход первого решающего блока подключен к первому выходу узла связи, первый и второй информационные входы которого подключены соответственно к первому выходу второго рещающего блока и третьему выходу первого решающего блока, второй вход признака режима узлового процессора подключен к шестьгй управляющим входам первого и второго решающих блоков, второй выход узла связи подключен к выходу младших разрядов результата узлового процессора, при этом в первом и втором решающих блоках (с + 2)-и информационный вход, пятый и щестой управляющие входы решающего блока подключены соответственно к второму входу (с+2)-го элемента И группы, (с+3)-му информационному входу сумматора и третьему входу (с + 2)-го элемента и группы.

Фи.2

| Вычислительный узел для однородной вычислительной системы | 1979 |

|

SU982008A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-01—Подача