Изобретение относится к цифровой вычислительной технике и может применяться ц составе арифметических устройств цифровых вычислительных машин при вычислении элементарных функций. Известны устройства, реализующие операцию псевдоделения при вычислении элементарных функций Y 1/Х, Y ,Вод X, Y лПГ и содержащие регистры, сумматоры и узлы сдвига 1 и 2. Известные устройства обладают ограниченным быстродействием с временем реализации операции псёвдоделения пропорциональным п , где t - задержка на одноразрядном сумм торе и на элементе типа И-ИЛИ. Наиболее близким по технической сущности к предлагаемому изобретению является устройство псевдоделения, содержащее первый и второй регистры, первый и второй сумматоры первый узел сдвига, причем выходы первого регистра подключены к первы входам первого сумматора, выходы сумм которого подключены к входам первого регистра, выходы второго ре гистра подключены к вторым первого сумматора, к входам первого узла сдвига и к первым входам второго сумматора, выходы сумм которого подключены к входам второго регистра, выходы первого узла сдвига подключены к вторым входам второго сумматора 2. Устройство псевдоделения выполняет операцию псевдоделения путем реализации рекуррентных соотношеНИИ irAi,i 2(A--,Bj, ,.€,,, its4gnS,; sign Ai, где , , 1 - X, HI X, 1 1,1, 2, 2,...,n-l, п-1;|.,нЗ P.l . Устройство работает циклически. Каждая итерация повтор;яется дважды, т.е. используются двойные шаги для сходимости вычислительного процесса.. Однако,известное устройство обладает ограниченным быстродействием, поскольку число исполняемых итераций пропорционально п и на каждой исполняемой итерации нео15ходимо выполнить операцию сложения (вычитания) с распространением переносов на п разрядов. Цель изобретения - увеличение быстродействия устройства псевдоделения за счет устранения переносов на п разрядов на каждой исполняемой итерации.

Поставленная цель достигается те что в устройство псевдоделения, содержащее первый и второй регистры, первый и второй сумматоры, первый узел сдвига, причем выход первого . регистра подключен к первому входу парного сумматора, выход сумм которого подключен к входу первого регистР9, выход второго регистра подклю ен к. второму входу первого сумматора, к входу первого узла сдвига и к первому входу второго сумматора, выход сумм которого подключен к входу второго регистра, выход первого узла сдвига подключен к второму входу второго сумматора, введены третий и четвертый регистры, второй узел сдвига и третий сумматор, приче выход третьего регистра подключен к третьему входу первого сумматора, выход переносов которого подключен к входу третьего регистра, выход четвертого регистра подключен к четвертому входу первого сумматора, к входу второго узла сдвига и к третье му входу второго сумматора, выход переносов которого подключен к входу четвертого регистра, выход второго узла сдвига подключен к четвертому входу второго сумматора, выход суммы старших разрядов первого сумматора, подключен к первому входу третьего сумматора, а выход переносов старших разрядов первого сумматора подключен ко второму входу третьего умматора.

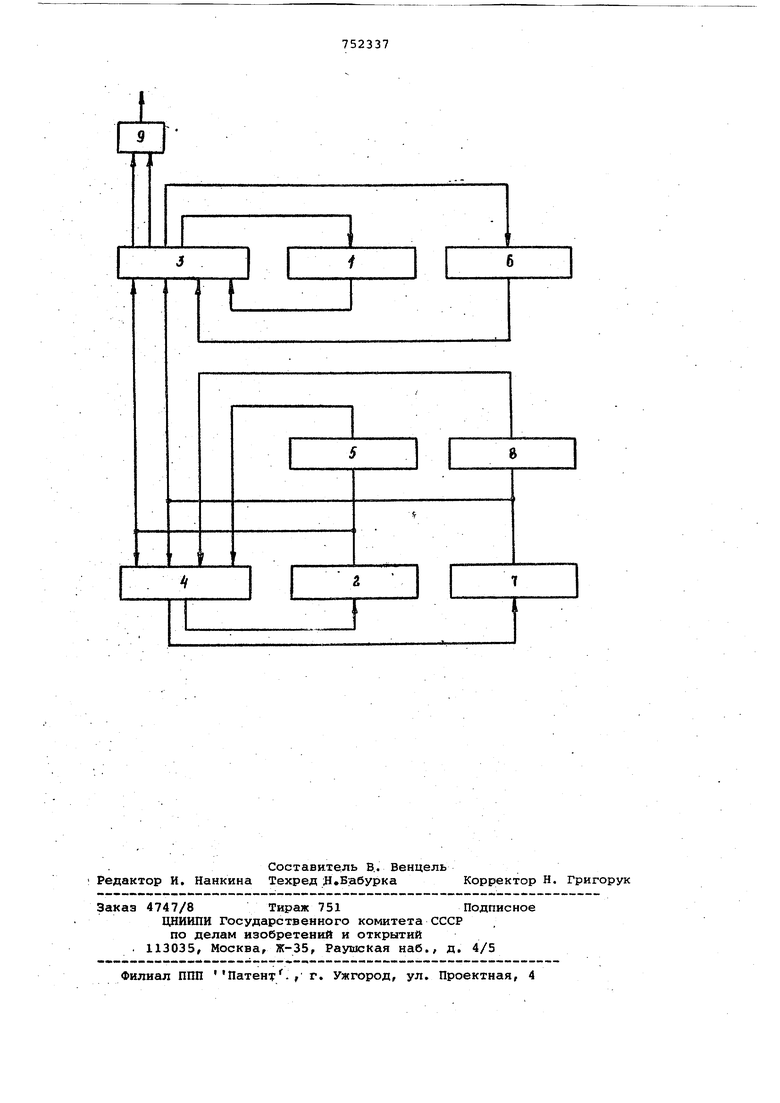

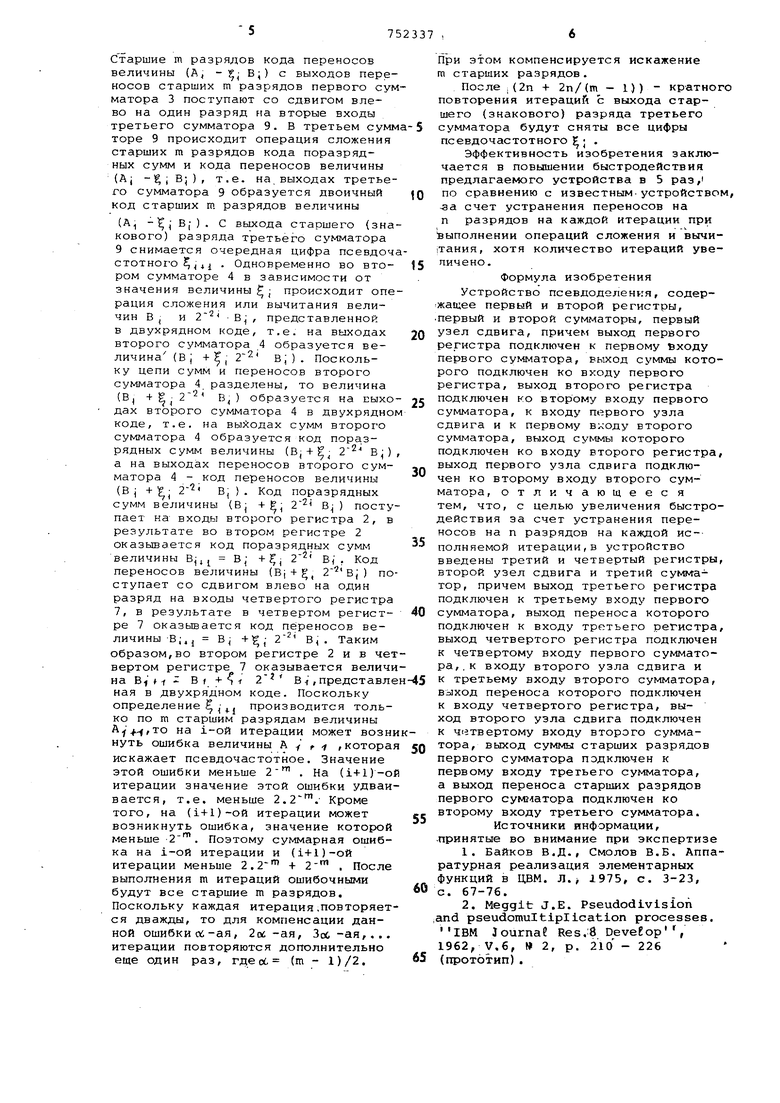

На чертеже показана структурная схема устройства псевдоделения.

Устройство содержит первый регист 1, второй регистр 2, первыйсумматор 3, второй сумматор 4, первый узел 5 сдвига, третий регистр 6, четвертый регистр 7, второй узел 8 сдвига/ третий сумматор 9 (с параллельным переносом).

( Устройство выполняет операцию псевдоделёния путем реализации рекуррентного соотношения

.i 2(A,.Bi),

(2)

B-iM B lg;2 B.

°1,

..,

где ,l, 2, 2, , . . ,о.-1 ,вс-1 ,оС ,оС,о6, d + l,oi+1, ...,2 d. -1,2с -1,2с6 ,2о6 2о6 , 2о(: + 1., 2ot + 1, . . . , Зоб - 1, Зоб- 1,3о., 3(Х, Зое, 3ot + 1, 3od+ l,...,n - 2, n - 2,n - 1, n-l,n-l, dL (m-i)/2,Ai 1-Х, BI X, - ef-1, t.lllc +1 m - количество разрядов третьего сумматора 9 меньше разрядности устройства п,.

Устройство работает циклически.

При этом первый регистр 1.работает одновременно с третьим регистром б, второй регистр 2-е четвертым

егистром 7, первый узел 5 сдвига о вторым узлом 8 сдвига.

На i-ой итерации код поразрядых сумм величин А, с выходов перого регистра 1 Поступает на первые ходы первого сумЫатора 3, код пееносов величины А| с выходов третьго регистра 6 - на третьи входы ервого сумматора 3. Код поразрядых сумм величины Bj с выходов вто рого регистра 2 поступает на вторые

входы первого сумматора 3, на входы первого узла 5 сдвига и на первые входы второго сумматора 4. Код переносов величины В, с выходов четвертого регистра 7 поступает на четвертые входы первого сумматора 3, на входы второго узла сдвига 8

и на третьи входы второго сумматора 4. В первом узле 5 сдвига происходит сдвиг кода поразрядных сумм величины Bj на 2j разрядов вправо, в результате на выходах первого узла 5 сдвига образуется код поразрядных сумм величины Bj, который поступает на вторые входы второго сумматора 4. Во втором узле 8 сдвига происходит сдвиг кода переносов величины в; на 2, . разрядов вправо. В результате на выходах второго узла 8 сдвига образуется код переносов величины 2 Bj, который поступает на четвертые входы второго сумматора 4. В первом сумматоре 3 в зависимости от значения величины j происходит операция сложения и вычитания величины АJ и В),представленных в двухрядном коде, и на выходах первого сумматора 3 образуется величина (А j -&; Bj), т.е. на выходах сумм первого сумматора 3 образуется код поразрядных сумм величины {А j Bj), а на выходах переносов первого сумматора 3 образуется код переносов величины (А - В) . Код поразрядных сумм величины (Aj - Bj) с выходов сумм первого сумматора 3 поступает со сдвигом влево на один разряд на входы первого регистра.1,в результате в первом регистре 1 оказывается код поразрядных сумм величины Aj,. 2 (А , В ) . Код переносов величины (А j - ; В,-) с аыходов переносов первого сумматора 3 поступает со сдвигом влево ila два разряда на

входы третьего регистра 6, в результате в третьем регистре б оказывается код переносов величины Ai. 2 (А ,- -)Bj). Таким образом,в первом регистре 1 и в третьем регистре 6 оказывается величина (Aj ), представленная в двухрядном коде. Старшие mразрядов кода поразрядных сумм величины ( ) с выходов сумм старших m разрядов первого сумматора 3 поступают на первые входы третьего сумматора 9.

Старшие m разрядов кода переносов величины (А - j В;) с выходов переносов старших m разрядов первого сумматора 3 поступают со сдвигом влево на один разряд на вторые входы третьего сумматора 9. В третьем сумм торе 9 происходит операция сложения старших m разрядов кода поразрядных сумм и кода переносов величины (А i - ; В; ) , т.е. на выходах третьего сумматора 9 образуется двоичный код старших m разрядов величины

СА В; ) . С выхода старшего (знакового) разряда третьего сумматора 9 снимается очередная цифра псевдочастотного , . Одновременно во втором сумматоре 4 в зависимости от значения величины происходит операция сложения или вычитания величин В, и , представленной в двухрядном коде, т.е. на вь1ходах второго сумматора 4 образуется величина (В j + , 22 в;). Поскольку цепи сумм и переносов второго сумматора 4 разделены, то величина (Bj В,) образуется на ЕЫХОдах второго сумматора 4 в двухрядном коде, т.е. на выводах сумм второго сумматора 4 образуется код поразрядных сумм величины (Bj + В ) а на выходах переносов второго сумматора 4 - код переносов величины (В; В, ). Код поразрядных сумм величины (Bj 2 В ) поступает на входы второго регистра 2, в результате во втором регистре 2 оказьшается код поразрядных сумм величины Bj, В, В( , Код переносов величины (В| + , 2Bj) поступает со сдвигом влево на один разряд на входы четвертого регистра 7, в результате в четвертом регистре 7 оказьшается код переносов ве-2, В, 2

личины -В

В,. Таким

1

образом,во втором регистре 2 и в четвертом регистре 7 оказывается величина BV м Bi ,представле мая в двухрядном коде. Поскольку определение производится только по m старшим разрядам величины АУ,ТО на i-ой итерации может вознинуть ошибка величины А V ,которая искажает псевдочастотное. Значение этой ошибки меньше 2 . На (И-1)-ой итерации значение этой ошибки удваивается, т.е. меньше 2..- Кроме того, на (1+1)-ой итерации может возникнуть ошибка, значение которой меньше 2. Поэтому суммарная ошибка на i-ой итерации и {1+1)-ой итерации меньше 2.2 + 2 , После выполнения m итераций ошибочными будут все старшие m разрядов. Поскольку каждая итерация.повторяется дважды, то для компенсации данной ошибки о;-ая, 2а; -ая, Зое -ая,... итерации повторяются дополнительно еще один раз, где об (т - 1)/2.

При этом компенсируется искажение m старших разрядов.

После i(2n + 2n/(m - 1)) - кратно повторения итераций с выхода старшего (знакового) разряда третьего сумматора будут сняты все цифры псевдочастотного ; .

Эффективность изобретения заключается в повышении быстродействия предлагаемого устройства в 5 раз/ по сравнению с известным-устройство -за счет устранения переносов на п разрядов на каждой итерации при выполнении операций сложения и вычи1тания, хотя количество итераций увепичено.

Формула изобретения

Устройство псевдоделенкя, содер-жащее первый и второй регистры, первый и второй сумматоры, первый узел сдвига, причем выход первого регистра подключен к первому йходу первого сумматора, выход суммы которого подключен ко входу первого регистра, выход второго регистра подключен ко второму входу первого сумматора, к входу первого узла сдвига и к первому входу второго сумматора, выход суммы которого подключен ко входу второго регистра выход первого узла сдвига подключен ко второму входу второго сумматора, отличающеес я тем, что, с целью увеличения быстродействия за счет устранения переносов на п разрядов на каждой ис-полняемой итерации,в устройство введены третий и четвертый регистры второй узел сдвига и третий сумм-атор, причем выход третьего регистра подключен к третьему первого сумматора, выход переноса которого подключен к входу третьего регистра выход четвертого регистра подключен к четвертому входу первого сумматора,, к входу второго узла сдвига и к третьему входу второго сумматора, выход переноса которого подключен к входу четвертого регистра, выход второго узла сдвига подключен к Ч1етвертому входу второго сумматора, выход суммы старших разрядов первого сумматора пэдклю чен к первому входу третьего сумматора, а выход переноса старших разрядов первого сумг атора подключен ко второму входу третьего сумматора.

Источники информации, .принятые во внимание при экспертизе

1.Байков В.Д., Смолов В.Б. Аппаратурная реализация элементарных функций в ЦВМ. Л. 1975, с. 3-23,

с. 67-76.

2.Meggit J.E. Pseudodivision ,and pseudomultiplication processes.

IBM lournae Res.:8 DeveEop, 1962, y.6, 2, p. 210- 226 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство псевдоделения | 1978 |

|

SU752336A1 |

| Устройство псевдоделения | 1978 |

|

SU742931A1 |

| Арифметическое устройство | 1978 |

|

SU763894A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Узловой процессор | 1986 |

|

SU1399763A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-31—Подача