. . 1

Изобретение относится к вычислительной технике, может быть использовано при построении устройств для решения задач математической физики, описываемых дифференциальными уравнениями в частных производных.

Известен вычислительный узел ци4ровой сетки, содержащий многовходовой сумматср, регистр сдвига, элемент И и группу элементов И 1.ю

Недостаток рассматриваемого узла низкая скорость решения задач.

Наиболее близким к предлагаемому по технической сущности является вычис- .|5 лительный узел цифровой сетки, соц&р- жащий запоминающее устройство, коммутатор, сумматор, регистр сдвига, регистр коэффициента, элемент И, группу элемейтов И 2..О

Недостатком известного устройства является большое время решения задач.

Цель изобретения - повышение быстродействия устройства.

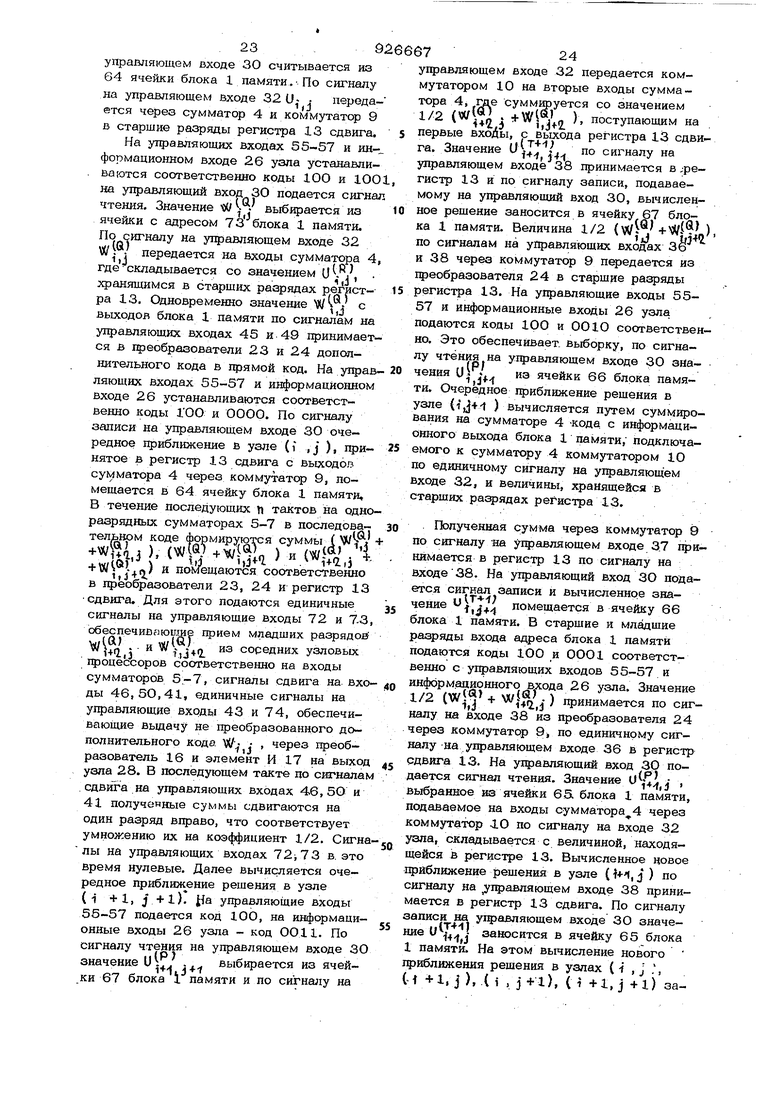

Поставленная цель достигается тем, что в вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных, ёод жащий первый блок памяти, выход котсрого соединен с входом первого сумматора, выход которого подключен к первому входу первого коммутатора, второй коммутатор, выход которого соединен с первым входом регистра сдвига, первый выход которого подключен к первому входу первого блока памяти, второй вход которого соединен с выходом третьего коммутатсра, первая группа элементов И, первый элемент И, дополнительно введеш 1 второй блок памяти, группа элементов НЕ, вторая группа элементов И, второй, третий и четвертый элементы И, втсрой, третий, чет вертый и пятый сумматсры, элемент ИЛИ первый, второй и третий преобразователи дополнительного кода в хдэямой код, четвертый коммутатор, выход которого соединен с первым входом первого пре- образователя дополнительного кода в прямой код, первый выход которого соединен с первым Входом второго коммутатора, Второй Вход которого подключен к первому выхрду второго преобразователя дополнительного кода в прямой крд вторые входы первого и второго преобразователей дополнительного кода в пря мой код подключены к первой группе входов третьего коммутатора и к первы входам второго и третьего сумматоров, вторые входы которых соединены с выходами первого и второго элементов И, выхЬды которых подключены к входам .четвертого сумматора, выход которого соединен с вторым входом регистра сдвига, второй выход которого подключен к первому входу третьего преобразо вателя дополнительного кода в прямой код, выход которого подключен к первому входу третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подклю чен к выходу четвертого элемента И,. первый вход которого соединен с вторым входом третьего преобразователя дополнительного кода в прямой код и подключен к третьему, выходу регистра сдвига, выход второго сумматора соединен с вторым входом первого преобразователя дополнительного кода в прямой код, выход третьего сумматора соединен с первым входом второго преобразователя дополнительного кода в прямой код, второй вход которого соединен с первым входом четвертого коммутатора, с входом первой группы элементов И, с вторым Входом первого коммутатора- и подключен к выходу первого блока памяти, выход третьего коммутатора соединен с входами регистра, с первыми входами второй группы элементов И и подключен к второму входу первого блока памяти, выход регистра соединен с втсрыми входами второй группы элементов И, выходы которых подключены к первому входу второго блока памяти, второй вход которого соединен с выходом регистра сдвига, выход второго блока памяти через группу элементов НЕ додключен к второму входу первого сумматора, выход первого коммутатора подключен к первому входу пятого сумматора, второй вход которого соединен с выходом регистра сдвига, выход пятого сумматора подключен к третьему входу второго коммутатора, вторая группа входов треть его коммутатора соединена с первыми входами первого и второго элементов И. На чертеже приведено предлагаемое устройство. Устройство содержит блоки 1 и 2 . памяти, сумматоры 3-7, коммутаторы 8-11, регистр 12 знаков соседних неизвестных, регистр 13 сдвига, группы элементов И 14 и 15, преобразователь 16 дополнительного кода в прямой код, элементы И 17-2О, элемент ИЛИ 21, группа элементов НЕ 22, преобразователи 23 и 24 дополнительного кода в прямой код, информационные входы 25-27, последовательный выход 28 узла, параллельные информационные выходы 29 узла, управляющие входы 30-74 узла. Предлагаемый вычислительный узел цифровой сетки позволяет вычислить., приближения к решению в четырех соседних узлах сеточной области по алгоритму ....ul.... -ifj 1.J -.J 1|3 li . ,. .ы,..с..иР + Hi 1.J li il rJ i«,j-l ,,j l :|-4i lH: - ij MH-4i ; 4iO4.v r;-4i « -j iiii«4 i,,iv«iM,j«i ,,, u Vv€-. «tr-M «,.,r%««V . :. «« f;.(,i)- (,,.«t«y;(9, ,.( де S номер итераций; Т - номер цика вычисления очередного Приближения; - искомое решение задачи в узлах етки; i, j - шздексы строки к столбца сеточной области; Р - количество ите раций расчета U на одном цикле вычисления очередного приближения решения; Q - количество итераций расчета на одном цикле вычисления очередного приближения решения; - 30{, j ,j .diij-di.-.dj; j - di-,j, приведенные каэфт приведенные коэффициенты разностной краевой задачи соответственно для узлов (i ,j ), (i +1,J ), ( Ь j+l), (HI, j+1). FI.J . f f,j .f,-H,.j i,j+i it-JJH приведенные правые части разностных уравнений; W - поправка к решению U , вычисляемая в. узлах сетки, для которых индексы i и j нечетны, R - вспомогательная переменная. Предлагаемое устройство работает следующим образом. Вычисление искомого решения в узла сеточной области в общей случае осуществляется в два раза. На первом этапе в блок 1 памяти заносятся сочетания сумм коэффициентов по 0,1,2,3,4 членов для узлов ( j , J ) ( 1 -fl, j ), (l ,j-t-l), (i H;j+l) соответственно В ячейки O-15, 16-3i, 32-47, 48-63. В блок 2 памяти заносятся удвоенные значения соответствующих сочетаний сумм коэффициентов по О, 1, 2,3,4 членов для узлов { 1 , j), ( f + 1, j ), ( f , j -И), ( i 1, j +1). При этом соответствие между адресами ячеек блока 1 памяти и его содержимым устанавливается зависимостью: ,c,0........). () ) flio (То 304,,,), где fo (1- оС 5) (1- cL 4), 0 (1- d 5) oL4, 0 dL5, (1- oL4 f cL 5 , X - содержимое ячейки запоминающего устройства с двоичным адресом 04.5,014 I cjtjjtot.j, oi, d о j. В ячейки блока 2 памяти, определяемые aapecaMK dL d dij. заносится величина 2Х. При занесении в блоки 1 и 2 памяти используются информационные входы 26 узла для задания адресов соответствующих ячеек и входы 27 задания коэффициентов узла. Предварительно все разряды регистра знаков соседних неизвестных устанавливаются в единичное состояние подачей н управляющий вход 53 узла единичного сигнала. В старшие разряды входов адре са блоков 1 и 2 памяти задается код ООП путем подачи нулевых у1фавляющих сигналов на управляющие входы 55-6О узла. Подачей единичного сигнала на управляющий вход 4О узла регистр 13 сдвига устанавливается р нулевое состояние. На входы 26 узла подается код ОООО, который коммутатором 8 подключается к младщим разрядам входа адреса блока 1 памяти по единичному сигналу на управляющем входе 68. Этот же код через элементы И, группы элементов И 14, открытые едишпнымн сигналами, снимаемыми с выходов регистра 12 знаков соседних неизвестных, подается на младшие разряды входа адреса блока 2 памяти. На утфавляющие входы 30 и 31 узла подаются сигналы записи в блоки 1 и 2 памяти и код нуля, находящийся в регистре 13 сдвига, записывается в нулевые ячейки блоков 1 и 2 памяти. Далее коэффициент , поступающий на информационные входы узла 27, по единичному сюналу на угфавляющем входе 45 узла, заносится в щюобразователь 23 в 1дзямой код через коммутатор 11, один разряд котсрого аналогичен разряду коммутатс а 1О, по единичному сигналу на управляющем входе 7О узла. С выхода преобразователя 23 в прямой код коэффициент dOj : через коммут.этор 9, по единичному сигналу на yпpaвJ яющeм входе 35, щ инямается в регистр 13 параллельным кодом, по единичному сигналу на управляющем входе 38 узла. На входы 26 узла подается код ООО1, который аналогично коду ОООО подключается к младщим разрядам входов адреса блоков и 2 памяти. На управляющий вход ЗО подается сигнал записи в блок 1 памяти и коэффициент 30 ; , снимаемый с выходов регистра 13 сдвига, помещается в первую ячейку блока 1 памяти. На управляющий вход 39 узла подается сигнал сдвига, по которому содержимоерегистра 13 сдвига сдвигается на один разряд влево, что соответствует умножению коэффициента на два. На управляющий вход 31 подается сигнал записи в блок 2 памяти и величина 2dO .- с выходов регистра 13 сдвига записывается в ячейку с адресом 1. Далее выполняются два цикла форМ1фования содержимого второй и третьей ячеек блоков 1 и 2 памяти. К оэффициен СО j аналогично коэффициенту do i,; с информационных входов 27 узла через коммутатор 11 принимается в преобразователь 23 в прямой код и через коммутатор 9 передается в регистр 13 сдвига. На вход 26 узла пода ется код ОООО, которьЕй коммутатором 8 подключается к младшим разрядам входа адреса блока 1 памяти. На управляющий вход ЗО узла подается сигнал чтения блока 1 памяти. Информационный выход блока 1 памяти коммутатором 10 подключается к второй группе входов су матора 4, первая группа входов которого соединена с выходами регистра 13 сдвига. Коэффициент COv . суммируется на сумматоре 4 с содержимым нулевой ячейки блока 1°памяти. Результат cyMi мирования по управляющему сигналу на управляющем входе 37 узла через коммутатор 9 принимается в регистр 13 сдвига по единичному сигналу на управл ющем входе 38 узла. После этого на входы 26 узла подается код ОО10, который коммутатором 8 и группой элементов И 14 подключается к младщим разрядам входов адреса блоков 1 и 2 памяти. На управляющий вход 30 узла подается сигнал записи в блок 1 памяти и коэффиаиеиг , помещается во вторую ячейку блока. 1 памяти. По сигналу сдвига на управляющем входе 39 содержимое регистра 13 сдвигается на один разряд влево. На управляющий вход 31 подается сигнал записи в запоминающее устройство 2 и во вторую ячейку его помещается величина 2 -СО результате второго цикла вновь происхо дит занесение коэффициента в регистр 13 сдвига через коммутатор 9 по единичному сигналу на управляющем вхо 35 из преобразователя 23, чтение из первой ячейки блока 1 памяти коэффициента do J , суммирование на сумматоре 4 содержимого регистра 13 с вых . дом данных запоминающего, устройства 1 подключенного к сумматсфу коммутаторо 1О, запоминание результата суммирован в регистре 13 и запись по адресу 00ООН суммы - +clO,j в блок 1памяти, а в блок 2 памяти по тому жб адресу кода величины 2 (СО j ). Далее в преобразователь 23 заносится код коэффициента bOj ив течение последующих четырех циклов: за несение коэффициента в регистр 13 чтение из блока 1 памяти - сумм1фоеание на сумматоре 4 - прием в регистр 13 - запись в блок 1 памяти содержимого регистра 13 - запись в блок 2 памяти, сдвинутого на один разряд влево содержимого регистра 13, фс змиру ется содержимое ячеек 4-7 блока 1 памяти, т.е. суммы toO,,;+ 0,.j + ,, ъо + со , +СО.,.,. + + 30 i и содержимое ячеек 4-7 блока 2 памяти представляющее собой величины 2 (to,. 1 + О), 2 ( +dOij ), 2 (-bOu ). 2 (bO,j + CO,..,- + + dlO{ il. При этом на входы 26 устройства должна подаваться следующая последовательность кодов: 0000, 0100, ООО1,0101, ОО10, ОНО, ООН, 0111. На управляющие входы 55-57 и 58-60 узла в это время подается код ООО. После этого в гфеобразователь заносится коэффициент 61 ,j и в течение последующих 8 циклов формируется содержимое ячеек 8-15 блоков. и 2 памяти. На вход 26 узла подается такая посредоватедьность кодов ОООО, 100О, ООО1, 1001,..., ОНО, 1НО, 0111, 1111. На этом формиррвание сочетаний сумм коэффшшентов для узла ( i , j ) заканчивается. Далее аналогичным образом осуществляется формирование содержимого ячеек 16-31 блоков 1 и 2 памяти, в которые заносятся сочетания сумм коэфф1рше.атов по О, 1, 2, 3, 4 членов для узла ( +l,j ). При этом на управляющих входах 55-57 и 58-6О узла устанавливается код 001. Процесс формирования сочетаний сумм коэффициентов повторяется как для узла (i , j ), только с информационных входов узла 27 в нужные моменты снимаются в щэеобрааователь 23 коэффициенты для узла (i 1, j ),.j.0,.,.j ,Ы,.,5 ,dV,j. После Этого на управляющих входах 5557, 58-6О устанавливается код О1О и аналогичным образом формируются сочетания сумм коэффициентов , , , dlj ; ДЛЯ узла ( 1 , j +1). При фсфмироваши сочетаний сумм коэффициент тов aJ|,j ,cb4,j , ъ s,j, da ,.,j для узла (i Itj i на узфавляющих входах 55-57 и 58-6О устанавливается код ОН. После окончания формщювания сочетаний сумм коэффициентов для чё гырех узлов в ячейки блока 1 памяти с адресами 68-72 заносятся правые части разностных уравнений f { ; ) соответственно. Iljfi i+ii +i i Для этого на управляющие входы 57-58 уада подается код 100. Значение пршшмается с информационного входа 27, подключаемого коммутатором Н, по сигналу на управляющем входе 7О, к входу преобразователя 23, по сигналу на управляющем входе 45, параллельным кодом в регистр г зеобрааователя 23. С выхода преобразователя 23 значение через коммутатсф 9 по сигналу на управляюще входе 35 принимается в регистр 13 сдв га, по сигналу на входе 38. На информационные входы 26 узла подается код 01ОО, который подключается комму татором 8 по сигналу на управляющем входе 68, к младшим разрядам входа адреса блока 1 памяти. На управляющий :заход ЗО узла подается сигнал записи в |блок 1 памяти и значение .- помещае ся в ячейку с адресом 68, Аналогичным образом значения ,3 ,j+- f V - .- , помещаются в ячейки с адресами 69-72, для чего на информациойные входы 26 узла подаются код 0101, ОНО, 0111, 100О. Далее в ячейки бдока 1 памяти с адреса 1И 6468 заносятся нулевые начальные приближеййя искомого ращения в узлах (i , i ), ( i -И, /), ( f . j +1), { i +1,. j -M) и поправки W - : соответственно. Для этого на управляющий Вход 40 узла подается сигнал сброса и регистр 13 сдвига устанавливается в :нойь. На йходах 55-57 устанавливается |Код 1ОО. На входах 26 узла последовательно устанавливаются коды ОООО, ООО1,ОО10, ООН, 010О, которые коммутатором 8 по-сигналу на управляю щем входе 68 подаются в младщие раз ряды йщзеса блока 1 памяти. После устаноьк:ц .очередного кода на входах ащ)ога на управляющий вход ЗО подает6я снгкйл- записи и код нуля, снимаемы с выходов регистра сдвига, помещается всоответствующую ячейку блока 1 пам TJBU На &ТОМ первый этап работы устрой ства заканчивается. На втором этапе осуществляется вычисление нового я эиближения рещения по рас етным формулам. Реализация каждой из формул включает подготовительные операции, необходимые для занесения ;3начений соответствующих переменньк, участвующих в вычислении, в младшие раарады регистра 13 сдвига и в iqjeобразователи 23, 24, непосредственно вычисление и занесение вычисленного значения соагвётствующей переменной в блок памяти. Подготовительные операции для реализации первой формулы состоят в следующем. На управляющих входах 55-57 узла устанавливается код ЮО, а на шффмационном входе 26 код ООО1. Это обеспечивает подачу на входы адре са блока 1 памяти адреса 65. По сигналу чтение на управляющем входе 30 узла считывается значение U , . на предьщущей итерации хранящееся в ячейке 65 блока 1 памяти, и через коммутатор 10, сумматор 4 н коммутатор 9, по единичным сигналам на управляющих входах 32 и 37 перед ается в регистр 13 сдвига. Значение U . . щэинимается также в преобразовате пь 23 дополнительного кода в прямой код по единичному сигналу на управляющем входе 45. В течение последующих ( П +2) тактов (и - разрядность неизвестных и коэффициентов), содержимое старщих разрядов регистра 13 сдвигается вгфаво, в младшие разрядь по сигналу сдвига на управляющем входе 41 узла. При этом элементы К 17 и 18 закрыты. Одноврек енно со сдвигом содержимого регистра 13 на информационном входе узла устанавливается код ОО1О, который коммутатором 8 по единичному сигналу на управляющем входе 68 подается в младщие разряды входа адреса блоков памяти 1 и 2. На управляющий вход ЗО подается сигнал чтения блока 1 памяти. Значение iij+-i предьщущей итерации, фанящееся в 66 ячейке блока 1 памяти, по единичному сигналу на управляющем входе 49 принимается в преобразователь 24. Таким образом, в результате подготовительных операций в блоки 23 и 24 помещаются значения .- и соответственно, в младщие разряды регистра 13 знанение и j . На управляющих входах 55-57 устанавливается код ООО. По единичному сигналу на управляющем входе 4О разряды регистра 13 устанавливаются в ноль. В течение последующих п циклов осуществляется вычисление нового приближения в, узле ( -1 , j ), для чего реализуется формула (1). В первом цикле ра-. устройства на этом этапе подаются единичные сигналы на управляющие входы 42, 47, 51, 54, 61, 64, 65, 69. Это обеспечивает прием в регистр соседних неизвестных 12 знаковых разрядов и f i и . из соседних узловых процессоров по входам 25 и . , преобразователей 23 и24 дополнительного кода в прямой код, вьщачу в соседние узловые щ)оцессоры знака U , , находящегося в знаковом разрядемладшей части регистра 13 сдвига. Далее в течение п -1 циклов подаются единичные управляющие сигналь на входы 43, 48, 52, 61, 64, 65, 69, 34, 33,37. Этим обеспечивается при начшгая с младших раэрадов iqjHMoro кода и - .- и Uv из соседних узловых процессоров и i преобразователей 23, 24 Каждый п -и разряд этих чисел через коммутатор 8 подается в младшие разряды входа адреса блока 1 памяти, а роразрядная конъюнкция кода с выхода коммутат ра 8 и кода, гранящегося в регистре 1 подается в младшие разряды блока 2 па мяти. Из ячейки брока 1 памяти, адрес которой определяется кодом ,,..,mu.,c- Выбирается ранее подготовленное частич ное произведение . iH/t 3 °i, cOjjU M do.jU$,tf ПО сигналу Чтения блока 1 памяти на управляющем входе ЗО.. Одновременно на управляющий вход 31 подаётся сигнал чтения из блока 2 памяти. Из ячейки блока 2 памяти, раз ряды адреса которой определяются из выражений . ,j) (ulf4)S,jH ..)Ч иннь--, (и(.()д.п.к., ..к.,...,и.,.к.-, -И разрад 1ФЯМОГО кода искомого решения на предыдущей итерации в уалах (i -и ), а -n,j). (1, j -fl) соответственно. Si ,j ...I ( j -H) - значение знаковых разрядов искомого решения на предьщущей итерации в соответствующих узлах сеточной области, выбирается величина коррекции кода частичного произ дения, равная 2 {aOi,jCt.-,,+ ,jCl4 + dO,.,do). Истинное частичное произведение фор мируется путем вычитания из величины, снимаемой с инфсрмаиионных выходов блока I памяти коррект1фующего кода, снимаемого с выходов блока 2 памяти. Вычитание осуществляется путем сложения на .сумматоре 3 кода, снимаемого с выходов блока 1 памяти с дополнительным кодом корректирующего кода, формируемого путем инвертирования кода с выхода блока 2 памяти на элементах И 17 группы 22 и добавления единицы (Подаваемой на управляющий вход узла 34. Выход сумматора 3 подключается коммутатором 1О к входам сумматора 4. Сумма с выходов сумматора 4 принимается в старшие разряды регистра 13 сдвига по управляющему сигналу на входе 38. По сигналу сдвига, поступающему на управляющий вход 41 устройства, осуществляется сдвиг содержимого регистра 13 на один разряд вправо. Код значения искомой функции в узле ( 1 , j ), хранящейся в младших разрядах регистра 13 через преобразователь 16. кодов, элемент И 17 и элемент ИЛИ 21, вьщается в соседние узловые процессоры. Преобразователь 16 дополнительного кода в прямой код и преобразователи 23 и 24 предназначеньз для получения прямого кода от величины, ;фанящейся в регистрах сдвига и поступающей на его вход. Если знак величины, поступающей на вход преобразователя, отрицателен, то от нее берется дополрительный код,. в случае положительного знака код, поступающий на вход преобразол. ателя, передается на его выход без изменения. После прохождения п -циклов на управляющих входах S5-5.7 устанавливается код 100. На информационный вход 26 подается код 01О1, который коммутатором 8 по единичному сигналу на управляющем входе 68 подается в младшие разряды адреса запоминающего устройства. По сигналу чтение запоминаюшегх устройства на управляющем входе Зи узла из ячейки с адресом 68 выбирается значение jF , которое коммутатором 10 по сигналу на управляющем входе 32 подается на входы сумматора 4 и суммируется с произведеннемсЮч, IU +, ,.,,,. о,и1 йЧУо о,,. накопленным в предьщущие циклы работы устройства в регистре 13. На этом реализация первой формулы заканчивается. Регистр 12 устанавливается в единичное состояние по сигналу на управляющем входе 53. На у1равляющие входы 26 узла подается код ОООО и вычислительное значение , находящееся в старших разрядах регистра 13 сдвига, по сигналу записи на управляющих входах ЗО и 31 узла заносится в ячейку блоков 1,и 2 памяти с адресом 64. По сигналу на управляющем входе 4О старшие разряды регистра 13 устанавливаются в ноль. Далее выполняются, подготовительные операции для реализации четвертой формуль.. Из блока i памяти по сигналу на управляющем Входе ЗО читается значение 1 j-f-t ранящееся в ячейке с адресом 66 и передается в регистр 13 через коммутатор Ю, сумматор 4 и коммутатор 9. На входы адреса, при этом должен подаваться код 10О с управляющих входов 55-57 узла и ОО10 с информационного входа 26. Значение и.,. с вы--,llJ ходов блока 1 принимается также в щ)еобразователе 2.4 по сигналу на управляющем входе 49. На входах 55-57 к 26 устанавливаются коды 1ОО и ООО1 По сигналу чтения из ячейки 65 блока 1 памяти считывается значение U f и по сигналу на входе 45 г ринимается в преобразователь 23. Одновременно значение и . по сигналу на входе 41 сдвигается в младщйе разряды регистра 13. В резуль,тате этих операций значение U j, помещаемся в преобразователь 24 в прямой код и младшие разряды регистра 13 . - в блок 23. Старщие разряды регистра 13 по сигналу на управляющем входе 40 устанавливаются в ноль. На управляющих входах 55-57 устанавливается код ОН и в течение последующих П Ш1КЛОВ работы устройства вычисляется новое приближение в узле ( i -ь 1, j-H), путем реализации формулы (4). В .первом цикле единичные сигналы лодаются на управляющие входы 42,47,51, 54,62,63,66,67. Это обеспечивает прирегистр знаков соседних неизвестны ем в 12 знаков ( . ии ,( из соседних узловых процессоров по входам 25 и и , из преобразовате лей 23 и 24, вьщачу в соседние узловые лфоцессоры знака из-знакового разряда младщей части регистра 13 В последующие п -1 цикл подаются единичные управляющие сигналы на входы .43,48,52,62,63,66,67. Этим обеспечивается прием последовательно, начиная с младщих разрядов, прямых кодов U::4.9 .-. из соседних узловых точек , по вхоЬам 25 . из преобразователей 23 и 24, подача каждого 9 6714 -го разряда через коммутатор 8 в младшие разряды входа адреса блока 1 памяти и поразрядной коньюнкцйи кодов с выхода регистра 12 и коммутатора 8 в младщйе разряды входа адреса блока 2 памяти, выдача в соседние узловые процессоры младщего прямого кода; У {,41 В старщие разряды входов адреса блоков 1 и 2 памяти постоянно подается код ОО.1 с управляющих входов 55-57. По сигналу чтения блоков 1 и 2 памяти, подаваемому на управляющие входы 30 и 31, происходит чтение из соответствующих ячеек кода, ранее подготовленного частичного произведения .f «M4if /iHjW .. коррекции этого частичного произведения в соответствии со знаками, хранящимися в регистре 12. Скоррект ованное на сумматоре 3 частичное произведение через KOMMyiaTop 10 подается .на входы сумматора 4, где суммируется с суммой частичных произведений для предыдущих разрядов, :фанящейся в регистре 13. Сумма с выходов сумматора 4 через коммутатор 9 принимается в регистр 13 по сигналу на управляющем входе 38 узла. По сигналу сдвига на управляющем входе 41 содержимое регистра 13 сдвигается на 1 вправо. В следующем цикле снова подавэтся сигналы чтения на управляющие входы ЗО, 31 из соответствующих ячеек бйоков 1 и 2 памяти, выбирается код частичного тфоизведения и соответствующий еМу корректирующий код, формируется частичное пронзведение и добавляется к ранее накопленной сумме частичных произведений для предьщущих разрядов. После прохождения п циклов на управляющих входах 55-57 устанавливается код 10О. На информационный вход 26 подается код 0111, который коммутатором 8 подключается к младщим разрядам входа адре- , са блока 1 памяти. Из ячейки с двоичным адресом 1ОО0111 выбирается значение f. ,J4-i и через коммутатсф 1О, по сигпалу на входе 32, подается на входы сумматора 14. Значение U, с вьиюдов сумматфа 4 через коммутатср 9 принимается в старщие разряды регистра 1.3 по. сигналу на управляющем входе 38. На этом реализация четвертой формулы заканчивается. Далее организуется запись вычисленного решения в точке (i +1, j-H) в ячейку блока памяти с адресом 67. Для этого на информашюшгые входы 2.6 узла подается код QO11, который коммутатором 8 подключается к младшим разрядам входа адреса блока 1 памяти. На входах 55-57 при этом должен быть код 1ОО. По сигналу записи на управляющем входе 30 информация с выходов старших ра рядов регистра 13 сдвига помещается в указанную ячейку, Далее вьшолняются подготовительные операции для реализации третьей формулы. Старшие разряды регистра 13 уста.навливаются в ноль по сигналу на yiipaB ляющем входе 4О. На входы адреса блока 1 памяти подается код 10О с управляющих входов 55-57 и ООНс ин({юрмационных входов 26 через коммутатор 8. Значение U f с входов блока 1 памяти принимается в регистр 13 через коммутатор 1О, сумматор 4 и ком мутатор 9 по сигналам на управляющих входах 32,37,38 и в преобразователь 23 по сигналу на управляющем входе 45 На управляющих входах 55-57 к информ ционном входе 26 устанавливаются соответственно коды 1ОО И OOOQ. По сиг налу чтения на управляющем входе 30 из ячейки с адресом 64 читается значение выходов блока 1 памяти принимается в преобразователь 24 в прямой код по сигналу на управляющем входе 49. Одновременно значение по сигналам сдвига на входе 41 сдвигается в мпадщие разряды регистра 13. Старшие ра;зряды регистра 13 по сигнал на управляющем входе 40 устанавливаются в ноль. На этом подготовительные операции для вычисления U t заканчиваются. J На управляющих входах 55-57 устанавливается код 010 и в течение последующих п циклов работы устройства вычисляется новое приближение решения в узле ( 1, j +l) путем реализации треть ей формулы. В первом цикле на управляющие входы 42,47,51,54,62,63,65, 69 подаются единичные управляющие сигналы. Это обеспечивает прием в регистр 12 знаков соседних неизвестных знаковых разрядов U Л j соседних узловых процессоров по входам 25 , ,, из преобразователей 23,24 в прямой код соответствен но, выдачу в соседние узловые процессоры знака .. из знакового разряда младшей части регистра 13, В последующие (п -l) цикл подаются единичные управляющие сигналы на входы 43,48,52,62,63,65,59. Этим обеспечивается прием последовательно, на.чиная с младших разрядов прямых содов л А ИЗ соседних узловых BxoAi1 25 и U(f;i, из блоков 2.3 к 24, подача каждого п-го разряда через коммутатор 8 в младшие разряды входа адреса блока 1 памяти и пораарадной коньюнкции кодов с выхода, регистра 12 и коммутатора 8 в младшие разряды входа адреса блока 2 памяти, вьщача б соседние узловые процессоры младшего разряда прямого кода , J4-i из соседней узловой точки по выходу 28, По сигналу чтения блоков 1 и 2 памяти, подаваемому на управляющие входы 30, 31, происходит чтение из соответствующих ячеек кода, ранее подготовленного частичного произведения ,,-jV,.iM ,,aM и кода коррекции частичного произведения в соответствии со знаками, хранящимися в регистре 12. Скорректированное на сумматоре 3 частичное произведение через коммутатор 10 подается на входы сумматора 4, где сумм1фуется с суммой частичных произведений для предыдущих разрядов, хранящийся в регистре 13. С выходов сумматора 4 сумма через коммутатор 9 принимается в регистр 13 по сигналу на управляющем входе 38 узла. Далее содержимое регистра 13 сдвигается на один разряд вправо по сигналу сдвига на входе 41. После этого указанная последовательность действий повторяется для оче-. редкого разряда. После прохождения п-1 шиша обработки значащих разрядов на управляющих входах 55-57 устанавливается код. 10О. На информационный вход 26 подается код ОНО, который коммутатором 8 подключается к младщим разрядам входа адреса блока 1 памяти. Из ячейки с двоичным адресом вьйирается значение f i,j4xt и через ком- мутатор 10 по сигналу на входе 32 подается на входы сумматора 4. Значение i i с выходов сумматора 4через коммутатор 9 щэинимается в старшие разяды регистра 13 по сигналу на управляющем входе 38. На этом реализация третьей формулы заканчивается, Далее организуется запись вычисленного решения в точке ( i , j +1) в ячейку блока памяти с адресом 66, Для это го на информационные входы 26 узла подается код ОО1О, который коммутатором 8 подключается к младшим адреса блока 1 памяти. На входах 55-57 щ этом должен быть код 1ОО. По сигналу записи на управляющем входе ЗО ии}юрмация с выходов старших регистра 13 сдвига помещается в указанную ячейку. После этого вьшолняются подготовительные операции для реализации второй фqpмyлы. Старшие разряды регистра 13 устанавливаются по сигналу на утфав ляющем входе 40 в ноль. С управляющих входов 55-57 в старшие входов адреса блока 1 памяти подается код 1ОО и ОООО в младшие разряды адреса с информационных входов 26 через коммутатор. 8. Значение с выходов блока 1 памяти принимается в регистр 13 через коммутатор 1О, сум матор 4 и коммутатор 9 по сигналам на управляющих входах 32, 37, 38 и в преобразователь 23 дополнительного кода в прямой код по сигналу на управляющем входе 45. На управляющих входах 55-57 и информационном входе 26 устанавливаются соответственно коды 1ОО и ООН. По сигналу чтения на управляющем входе ЗО из ячейки с адресом 67 читается значение U -i выходов блока 1 памяти принимается в блок.зфанения и преобразования кода неизвестного по сигналу на .управляющем входе 49. Одновременно значение по сигналам сдвига на входе 41 сдвигается в младщие разряды регистра 13. Старшие разряды регистра 13 устанавливаются в ноль по сигналу на управляющем входе 40. На этом под1Х товительные операции для вычисления f заканчиваются. На управляющих входах 55-57 устанавливается код О01 В течение последующих п циклов раб ты устройства вычисляется новое гфибли жение решения в узле ( i +i,j ) путем реализации второй формулы. В первом цикле на управляющие входы 42,47,51 54,61,64,67 узла подаются единичные управляющие сигналы. Это обеспечивает прием в регистр 12 знаковых раотядов и и(. « i+ij-f из соседшк узловы и - , rtИ VJ , J процессоров по входам 25 и ij, U из преобразователей 23 и 24 соответственно, выдачу в соседние узло вые щэоцессоры знака и из знаковог разряда младшей части регистра 13. В последующие (п - Л.) циклы подаются диничные управляющие сигналы на входы 3,48,52,61,64,66,67. Этим обеспеивается прием начиная с младщих раз - - .ядов прямых кодов 054-04 из соседних узловых точек по входам 5 HUY,V 4VIj+i преобразоватеей 23 и 24, под4ча каждого р -го разяда через коммутатор 8 в младшие раэяды входа адреса блока 1 памяти и поразрядной коньюнкции кодов с выхода егистра 12 и коммутатора в в младшие азряды входа адреса блока 2 памяти, вьщача в соседние узловые процессоры младшего разряда прямого кода О V(j из узловой по Bbixosjy 28. По сигналу чтения блоков I и 2 памяти, подаваемому на управляющие входы ЗО, 31, происходит чтение из соответствующих ячеек кода ранее подготовленного частинного гфоизведения ,,1..U...M«1i,U;.,/ ,,jM и кода коррекции частичного произведения в соответствии со зна&ами, хранящимися в регистре 12. Скорректированное на сумматоре- 3 частинное произведение через коммутатор 1О подается на входы сумматора 4, где складывается с суммой частичных произведений для Щ)едьщущих , хранящейся в регистре 13. С выходов сумматора 4 через коммутатор 9 сумма принимается в регистр 13 по сигналу на управляющем входе 38 узла. Содержимое регистра 13 по сигналу на уцрав- ляющем входе 41 сдвигается на один разряд вправо. Затем указанная последовательность действий повтсфяется для очередного соседних неизвестных, поступающих на входы узла. После прохождения П -1 такта обработки зна, чащих разрядов на управляющих входах 55-57 устанавливается код 1ОО. На информационный вход 26 подается код ОНО, который коммутатором 8 подклю- . чается к младшим разрядам входа адреса блока 1 памяти. Из-ячейки с двоичным адресом 1ОО ОНО выбирается значение «.. и через коммутатор 1О р по сигналу на входе 32 подается на входы сумматора 4. Значение U. j с выходов суммато1 а 4 через коммутатор 9 принимается в старшие разряды регистра 13 по сигналу на управляющем входе 38.1 На этом реализация формулы (2) заканчивается. Далее организуется запись вычисленного решения в точке (i ) fi ячейку блока 1 памяти с адресом 65. Для этого в старшие ра&г рады адреса подается код 100 с управляющих входов 55-57 узла, а в младши разряды - код ООО1 с информационного входа узла 26. По сигналу записи на управляющем входе 3 информация с выходов старщих разрядов регистра 13сдвига помещается в выбранную ячейку. Старшие регистра 13 устанавливаются в ноль по сигналу на входе 40 узла. Описанный ирояесс вычисления U4,. . повторяется фиксированное число раз Р; задаваемое счетчиком количества итераций сеточной модели. Далее выполняются подготовительные операций для реализации формулы (5). Из ячейки 64 блока 1 памяти выбирается fpt значение и « путем пседачи в младшие и старшие разряды входа адреса соответственно кодов ОО О О с. входом 26 узла через коммутатор, и 1ОО с управляющих ВХОДОВ 55-57 и сигнала чтения на управляющий вход ЗО. Значение , с информационных выходов блока 1 памяти передается через коммутатор 10, сумматор 4 и коммутатор 9, по сигналам на входах 32 и 37 в старшие разряды регистра 13. Прием кода ОV в регистр 13 происходит по ух авляюще му сигналу на входе 38 узла. Путем подачи импульсов сдвига на управляющий вход 41 значение и егзивигае я В младшие разряды регистра 13. ПоС ле окончания сдвига старшие рагзр иы регистра 13 по сигналу на управляющек входе 40 устанавливаются в ноль. На управляющих входах 55-57 устанавливается код ООО. Подготовительные операции для вычисления R . на этом заканчиваются. В течение последующих (п -f 2 циклов работы устройства реализуется. формула (5). На управляющие входы узл 42, 62,64, 66, 69 подаются единичные управляющие сигналы. Это обеспечивает цЕрием в регистр 12 в первом цикле, по сигналу на управляющем входе 54, знаковых разрядов . и .. п i.fi из соседних узловых 1l1-Z IJ -orщэоцессоров соответственно входам 25 {р узла и вьщачу знака U - j из знакового разряда младшей части регистра 13 через элементы И 18 и ИЛИ 21 по выходу в соседние узловые процессоры. В последующие (п-1) циклы подаютоя единичные управляющие сигналы на входы 43,62,64,66, 69. Этим обеспе-. чивается подача в младшие разряды адреса блсжа 1 памяти разрядов прямых кодов . . .. из соседних узловых процессоров через коммутатор 8 и вьщача в соседние узловые процессор з младшего разряда U : из регистра 13 через преобразователь 16 в прямой код, элемент И 17 и элемент ИЛИ 21. Поразрядная коньюнкция кодов с вьисодов регистра 12 и коммутатора 8 подается в младшие разряды входа адреса блока 2 памяти. По сигналу чтении на управляющих входах ЗО и 31 происходит чтение из соответствующих ячеек значения ранее пог отовленного частичного произведения «y jM 4i€ljM j j aM. « « tiiW. и кода коррекции данного частичного проиэйедения в соотаетс твии со знаками, зфааяцшмиоя в регистре 12. Скорректирэваннею ш сумматоре 3 частичное произведение через коммутатор 10 подаётся на Ёходы сумматора 4, где складывается с суммой частичных i oiigведешШ ддя предьщуших разрядов, 5фанящейся в регистре 13. С выходов сумШтора 4 через коммутатор 9 сумма хфйнима тся в регнс-ф 13 по сигналу на :упраВляющем входе 38 узла. Содержимое регистра 13 по сигналу на управляющем взиэде 41 сдвигается на один разряд JwqjaBo. Затем указанная последовательность действий повторяется для очередного разряда неизвестных поступающих на входы узла. После 1фохо кдения TI -1 цикла обработки значащих разрядов на управляющих входах 55-57 устанавливается код 1ОО, На иввформационный вход узла 26 подается код 10ОО. По сигналу чтения на управляющем входе ЗО узла из блока 1 памяти выбJфaeтcя значение F ; и через коммутатор 10 передается на вторую группу входов сумматора 4, где складывается с суммой четырехпроизведений« a w/ °M«i,,. накопленной в. .регистре 13 и поступающей на первую группу входов сумматора 4. Из ячейки блока 2 памяти с адресом 64 считывается значение . Для этого на управляющих входах устанавливается код 100, на информационные входы 26 узла подается код OObO и подается сигнал чтеш1Я на управ ляющий вход 31. На сумматяре 3 по сигналу на управляющем входе 34 формируется дополнительный код ; , который коммутатором 10 подключается к входам сумматора-4, Сумма с выходов сумматора 4 гфинимается в регистр 13 по сигналу на управляющем входе 38 На этом реализация формулы 5 заканчивается. Значение R- помещается в ячей t J ку 65 блока 2 памяти. Для этого на ухфавляюших входах 58-60 устанавливается код 100, на информационнь1х.входах 26 код ООО1 и подается сигнал записи на управляющий вход 31. Для реализации формулы (6) регистр . 13 сдвига устанавливается в ноль и на угфавляющие входы 55-57 узла подается код ООО. В течение последующих (п ) циклов осуществляется вычисление W . В первом цикле подаются единичные сигналы на управляющие входы 42, 62, 64, 66, 69, что обеспечивает прием по сигналу на управляющем входе 54 в регистр 12 знаковых разрядов f-i.i.4-, . .«f,j 3 соседних узловых процессоров с входом узла 25 и выдачу знакаШФ по выходу 28 в соседние узловые процессоры. Далее в течение (п -1) цикла единичные сигналы подаются на управляющие входь 44,62,64,66,69, чем обеспечивается подана в младщие разряды адреса блока 1 памяти младших разрядов прямых кодов Wf,i ..j .W,U из соседних узловых процессоров через коммутатор 8 и вьщача в соседние узловые прсщессоры младщегх) разряда W из регистра 13 через преобразователь 1 , в прямой код, элемент И 17 . и элемент ИЛИ 21. Пс азрядная коньюнкция кодов с выходов регистра 12 и коммутатора 8 подается в младщие разряды входа адреса блока 2 памяти. По сигналу чтения на управл щих входах ЗО и 31 про исходит чтение .-из соответствующих ячеек значения ранее подготовленного частичного произведения . Т + -bfcO,%jW,-.j frJ +CO,.,-W-,j.-ttl + dOf,jW| . и кода коррекции дан ного частичного произведения в соответ- ствии со знаками, храшпцимися в регист ре 12. Скорректированное на сумматоре 3 ч тичное произведение через коммутатор 1О подается на входы сумматора 4, где складывается с суммой частичных произведеннй для предыдущих разрядов, хра нящейся В регистре 13. С выходов сумматора 4 через коммутатор 9 сумма пр1шимается в регистр 13 по сигналу на управляющем входе 38 узла. Содержимое регистра 13, по сигналу на управляющем входе 41 сдвигается на один разряд вправо. Затем указанная последовательность действий повторяется для очередного ра ряда соседних неизвестных поступающего на входы узла. После прохождения {п -1) цикла обработки значащих разрядов на . управляющих входах 58-6О устанавливается код 10О, все регистра 12 по сигналу на управляющем входе 53 устанавливаются в единичное состояние, на информационные входы 26 узла подает ся код ОО01. По сигналу чтения на угфавляющем входе 31 значение R j j выбирается из ячейки 65 блока памяти. Путем добавления на сумматоре 3 единицы, поступающей на управляющий вход 34 к обратному коду 1 : , снимаемому с выходов группы инверторов 22, формирует . ся дополнительный код R- . Полученный код с Выходов сумматора 3 через коммутатор 10 по едшшчному сигналу на управляющем входе 33 передается на вторую группу входов сумматора 4, где складывается с суммой четырех произведений Wi-a,j + ьо,-vX/;. 4.co.,j W-f Oj j -i j-. накопленной в регистре 13 л поступающей на первую группу ВХОДОВ сумматора 4. Результат сложения, принимается в регистр 13. В течение последующих (п +2) тактов знагчеш1еед г сдвигается в младщие разряды регистра 13 по сигналу на управляю щем входе 41. Процесс вычисления повторяется циклически фиксированное число раз О. , задаваемое счетчиком количество итераций сеточной модели. В последнем Q-м-цикле сдвиг в младщие разряды регистра 13 дится после записи W в блок. 1 памяти. Для этого на втравляющие входы 55-57 узла подается код 1ОО, на информационные входы 26 - код 1001. По сигналу записи на управляющем входе ЗО узла значение W . помещается в IIJ ячейку с адресом 73 блока 1 памяти, а затем в течение (п +2) тактов подаются сигналы сдвига на вход 41. Далее вычисляется очередное приближение рещения в узле ( i , j ) по формуле (7). Старшие разряды регистра 13 устанавливаются в ноль по сигналу на управляющем входе 40. На информационном входе 26 узла устанавливается код ОООО. Значение UY ; по сигналу чтения на MJ управляющем входе ЗО считывается из 64 ячейки блока 1 памяти.-По сигналу на управляющем входе 32 U передается через сумматор 4 и коммутатор 9 в старшие разряды регистра 13 сдвига. На управляющих входах 55-57 и ин- формационном входе 26 узла устанавливаются соответственно коды 1ОО и 1О0 на управляющий вход ЗО подается сигнал чтения. Значение W выбирается из ячейки с адресом 73блока 1 памяти. По с игналу на управляющем входе 32 передается на входы сумматора 4 где складывается со значением U Л . хранящимся в старших разрядах регистра 13. Одновременно значение wW с выходов блока 1 памяти по сигналам на управляющих входах 45 я 49 принимается в гфеобразователи 23 и 24 дополнительного кода в щ)ямой код. На управ ляющих входах 55-57 и информационном входе 26 устанавливаются соответственно коды IOO и 0000. По сигналу записи на управляющем входе ЗО очередно приближение в узле ({ ,j ), принятое в регистр 13 сдвига с выходов сумматора 4 через коммутатор 9, помещается в 64 ячейку блока 1 памяти, В течение последующих тг тактов на одно разрядных сумматорах 5-7 в последовательном коде формируются суммы ( Wj i +w|b),).Kft,i + И помещаются соответственно в преобразователи 23, 24 и регистр 13 сдвига. Для этого подаются единичные сигналы на управляющие входы 72 и 7-3 обеспечивающие прием младщих разрядов , . и . из соредних узловых пропессоров соответственно на входы сумматоров 5-7, сигналы сдвига на вхо ды 46,50,41, единичные сигналы на управляющие входы 43 и 74, обеспечивающие вьщачу не преобразованного до- полнительного кода , через преоб- разователь 16 и элемент И 17 на выход узла 28. В последующем такте по сигналам . сдвига на управляющих входах 4.6,50 и 41 полученные суммы сдвигаются на один разряд вправо, что соответствует умножению их иа коэффициент 1/2. Сигн лы на управляющих входах 72,73 в. это время нулевые. Далее вычисляется очередное приближение рещения в узле (i +1, J +l). а управляющие входы 55-57 подается код 10О, на информационные входы 26 узла - код ОО11. По сигналу чтения на управляющем входе ЗО значение Ui. ... выбирается из ячеи tiки 67 блока 1 памяти и по сигналу на управляющем входе 32 передается коммутатчром 10 на вторые входы сумматора 4, гае суммтуется со значением 1/2 3 1 jW поступающим на первые вхойы, с выхода регистра 13 сдвига. Значение U | по сигналу на управляющем входе 38 принимается в ,регистр 13 и по сигналу записи, подаваемому на управляющий вход 30, вычисленное рещение заносится в ячейку 67 блока 1 памяти. Величина 1/2 fj+Mf V по сигналам на управляющих входах 36 и 38 через коммутатор 9 предается из преобразователя 24 в старщие разряды регистра 13. На управляющие входы 5557 и информационные входы 26 узла подаются коды 100 и 0010 соответственно. Это обеспечивает, выборку, по сигналу чтения,на угфавляющем входе ЗО значения , из ячейки 66 блока памяти. Очередное приближение рещения в узле ) вычисляется путем суммирования на сумматоре 4 -кода с информационного выхода блока 1 памяти, подключаемого к сумматору 4 коммутатором 10 по единичному сигналу на управляющем входе 32, и величины, хранящейся в старщих разрядах регистра 13. . Полученная сумма через коммутатор 9 по сигналу -на управляющем входе 37 п|зинимается в регистр 13 по сигналу на входе38. На управляющий вход ЗО подается сигнал записи и вычисленное значение помещается в ячейку 66 блока 1 памяти. В старщие и младщие разряды входа адреса блока 1 памяти 1ОО и ООО1 соответстподаются коды 1UU и венно с управляющих входов 5 5-57 и информационного входа 26 узла. Значение 1/2 (W|J5 + .|- ) принимается по сигналу на входе 38 из преобразователя 24 через коммутатор 9, по единичному сигкилу -на управляющем входе 36 в регистр сдвига 13. На управляющий вход 30 подается сигнал чтения. Значение 0 j , выбранное из ячейки 65 блока 1 памяти, подаваемое на входы сумматора 4 через коммутатор 40 по сигналу на входе 32 узла, складывается с величиной, находящейся в регистре 13. Вычисленное новое приближение решения в узле (ч, j ) по сигналу на отправляющем входе 38 принимается в регистр 13 сдвига. По сигналу записи на управляющем входе ЗО значение заносится в ячейку 65 блока 1 памяти. На этом вычисление нового хфиближения решения в узлах {-f , j ., ( f +1. j ), ( i , j +1), С i +1, j +1) заканчивается. Подавая на входы 55-57 и 26 узла коды 100 ОООО, ЮО 0001, 1ОО ОО10 и 1ОО ООН можно, по управляющему сигналу на входах 44 узла и сигналу чтения на входе ЗО, осуществить считывание полученного решения по выходам 29 узла.. Предлагаемое устройство благодаря на личию новых элементов и связей между ними позволяет ускорить процесс получения решения. Формула изобре-тения Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных, содержащий первый блок памяти, выход которого соединен с первым вхойом первого сумматора, выход которого подключен к первому входу первого коммутатора, второй ком.мутатор, выход KOTqporo соединен с первым входом регистра сдвига, первый вы хсзд которого подключен к первому входу первого блока памяти, второй.вход которого соединен с выходом третьего коммутатора, первая группа элементов И, первый элемент И, отличающи йс я тем, что, с целью повьшения быстродействия устройства,. в него введены второй блок памяти, группа элементов НЕ, вторая группа элементов И, второй, третий и четвертый элементы И, второй, третий, четвертый и пятый сумматоры, элемент ИЛИ, первый, втсрой и третий преобразователи дополнительного кода в Щ)ямой код, четвертый коммутатор, выход которого соединен с первым входо первого преобразователя дополнительного кода в 1ФЯМОЙ код, первый выход которого соединен с первым входом второго коммутатора, второй вход которого подключен к первому выходу второго гфеобразователя дополнительного кода в прямой код, вторые входы первого и второго преобразователей дополнительного кода в прямой код подключены к первой группе входов третьего коммутатора и к первым входам второго и треть его сумматоров, вторые входы которых соединены с вы содами первого и второго элементов И, выходы которых подключены к входам четвертого сумматора, вы ход которого соединен с вторым входом регистра сдвига, второй выход которого подключен к первому входу третьего преобразователя дополнительного кода в прямой код, выход которого подключен к первому входу третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, первый вход которого соединен с вторым Входом третьего преобразователя дополнительного кода в прямой код и подключен к третьему выходу регистра сдвига, выход второго сумматора соединен с. вторым входом первого преобразователя дополнительного кода в прямой код, выход третьего сумматора соединен с первым входом второго преобразователя дополнительного кода в прямой код, второй вход которого соединен с первым входом коммутатора, с входами элементов И первой группы, с вторым входом первого коммутатора и подключен к выходу первого блока памяти, выход третьего коммутатора соединен с входами регистра, с первыми, входами элементов И второй группы и подключен к второму входу первого блока памяти, выход регистра соединен с вторыми входами элементов И группы. Выходы которых подключены к первому входу второго блока памяти, второй вход которого соединен с выходом регистра сдвига, выход второго блока памяти через группу элементов НЕ подключен к второму, входу первого сумматора, выход первого коммутатора подключен к первому входу пятого сумматора второй вход которого соединен с выходом регистра сдвига, выход пятого сумматора подключен к третьему входу втсрого коммутатора , вторая группа входов третьего коммутатора соединена с первыми входами первого и второго элементов И. .Источники информации, принятые во внимание гфи экспертизе 1.Авторское свидетельство СССР № 546891, кл. G 06 F 15/34, 1977. 2.Авторское свидетельство СССР по/заявке № 2717710/18-24, кл. Q 06 F 15/32, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1981 |

|

SU976448A1 |

| Вычислительный узел цифровой сеточной модели для решения дифференциальных уравнений в частных производных | 1980 |

|

SU894717A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ | 1971 |

|

SU297070A1 |

| Вычислительный узел цифровой сеточ-НОй МОдЕли для РЕшЕНия диффЕРЕНциАль-НыХ уРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU840920A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

Авторы

Даты

1982-05-07—Публикация

1980-05-14—Подача